6.3. Практика программирования PIC-микроконтроллеров

6.3.1. Описание лабораторного макета

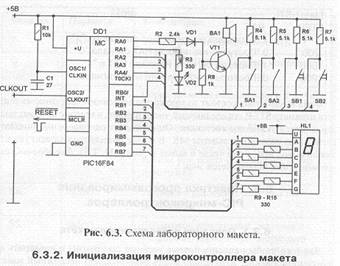

Для того чтобы написать первые учебные программы и проверить их функционирование, желательно иметь относительно несложный макет, содержащий самые распространенные периферийные устройства. Схема подобного макета, используемого при выполнении лабораторных работ студентами, приведена на рис. 6.3.

Макет питается от источника стабилизированного напряжения +5B. Тактовая частота МК задается RC-цепью и составляет около 2 МГц. К линии RA0 порта А подключен биполярный транзистор в ключевом режиме, нагруженный на динамик ВА1. Звучание динамика обеспечивается подачей на выход RA0 изменяющегося сигнала в звуковом диапазоне. К линии RA1 порта А подключен светодиод VD2, светящийся при высоком напряжении на выходе. Тумблеры SA1 и SA2, а также кнопки SB1 и SB2 подключены, соответственно, к линиям RA2 и RA3 порта А, а также к линии RA4 порта А и линии RB0 порта В. Исходное состояние кнопок — разомкнутое, что обеспечивает подачу на соответствующие входы МК высокого уровня сигнала.

Линии RB1 — RB7 порта В обслуживают семисегментный индикатор HL1 с общим анодом. Поэтому свечение сегмента индикатора обеспечивается при низком уровне сигнала на соответствующем выходе порта В. Макет также содержит средства программирования и связи с компьютером, которые на схеме не показаны.

6.3.2. Инициализация микроконтроллера макета

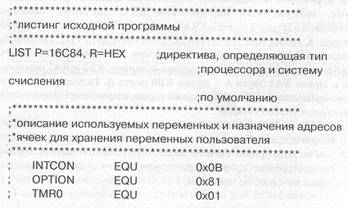

Прежде чем переходить к созданию простейших пользовательских программ, необходимо описать используемые в дальнейшем переменные и настроить МК на работу с выбранным макетом. С этой целью мы напишем и подробно рассмотрим листинг исходной программы init.asm, в состав которой будут включаться все остальные программы пользователя.

Рассмотрим работу этой программы. Вначале она указывает ассемблеру тип используемого МК и систему счисления по умолчанию. Идущие далее ассемблерные директивы EQU определяют ассемблерные константы, используемые в этой и последующих программах. Они позволяют использовать в тексте программы более удобные мнемонические метки, привязанные к структуре конкретного МК, вместо корректных, но более сложных ассемблерных выражений. Указатели ТЕМРА, ТЕМРВ, COUNTI и COUNT2 назначают адреса ячеек памяти для хранения промежуточных данных (текущих состояний, переменных циклов и т.п.).

Ассемблерные директивы #DEFINE задают строку, замещающую соответствующую метку, каждый раз, когда та будет встречаться в исходном тексте. В нашем случае эти директивы позволяют использовать символические имена, привязанные к схеме макета, вместо физических адресов соответствующих разрядов портов и регистров. При этом необходимо иметь в виду, что символы, которые определены директивой #DEFINE, не могут быть просмотрены симулятором. Поэтому для просмотра необходимо использовать физические адреса портов и регистров. Директива 0RG 0х00 устанавливает стартовый адрес программного кода равным 0, т.е. соответствующим начальному состоянию счетчика команд МК после сброса. Команда GOTO BEGIN вместе с ассемблерной директивой 0RG 0х005 и меткой BEGIN обеспечивают переход на адрес памяти программ 0x005, начиная с которого и размещается основная часть программы. Это необходимо для того, чтобы обойти адрес 0х004, используемый в качестве вектора прерывания, и тем самым зарезервировать его для возможных будущих применений.

Затем с помощью команды CALL INITP0kTS производится вызов подпрограммы инициализации портов. Вначале подпрограмма инициализации устанавливает в высокое (единичное) состояние выходные триггеры данных. Эта операция рекомендуется разработчиком МК для того, чтобы исключить неопределенность в состояниях регистров портов. Затем командой BSF STATUS,RP0 производится переключение на банк 1 памяти данных, где расположены регистры управления направлением передачи информации TRISA и TRISB. С помощью команд MOVLW 0xlC и MOVWF TRISA линии RA0 и RA1 порта А настраиваются на вывод, а остальные — на ввод. Команды MOVLW 0x01 и MOVWF TRISB настраивают линию RB0 порта В на ввод, а остальные — на вывод. С помощью команды BCF STATUS,RP0 производится возврат в банк 0, где располагаются необходимые для работы программы регистры и порты.

Поскольку в процессе работы с макетом перенастройка портов не производится, и введенных переменных достаточно для работы всех рассматриваемых учебных задач, они будут далее рассматриваться включенными по умолчанию в состав исходной программы init.asm. При написании учебных задач будет по возможности использоваться метод структурного программирования, при котором прикладная программа строится из некоторого набора программных модулей, каждый из которых реализует определенную процедуру обработки данных. При этом каждый из программных модулей имеет только одну точку входа и одну точку выхода. Введенные однажды программные модули могут использоваться под своим именем в других прикладных программах.

6.3.3. Программирование учебных задач

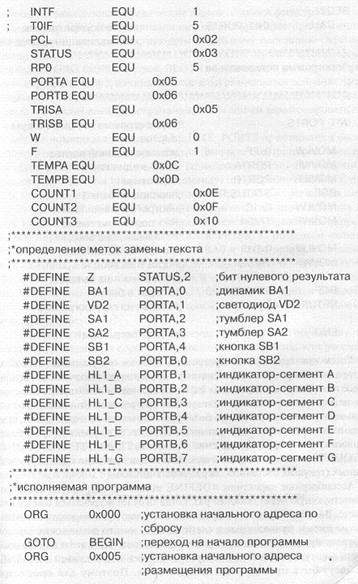

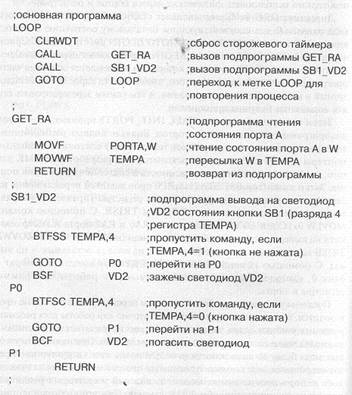

Начнем программирование учебных задач с написания программы, которая считывает состояние кнопки SB1 и выводит его на светодиодный индикатор VD2 так, что не нажатому состоянию кнопки (высокому уровню сигнала на вход е RA4) соответствует светящееся состояние светодиода, и наоборот.

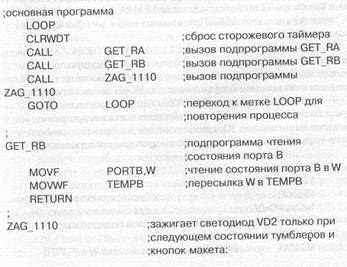

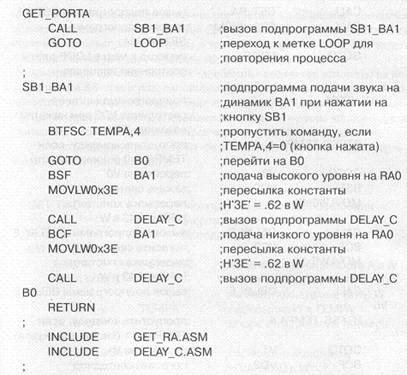

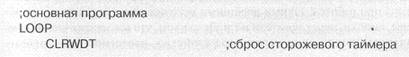

Основная программа содержит замкнутый цикл LOOP — СОТО LOOP, необходимый для периодического повторения цикла контроля состояния кнопки и вывода его на индикатор. Команда CLRWDT исключает влияние возможного сброса по переполнению сторожевого таймера на работу программы. Две следующие команды осуществляют вызов подпрограмм GET_RA и SB1_VD2. Первая из них (GET_RA) вначале считывает текущее состояние порта А, которое помещается в рабочий регистр W. Поскольку рабочий регистр может потребоваться при исполнении других команд, его состояние записывается в регистр TEMPA, используемый

здесь для временного хранения состояния порта А. Таким образом, после возврата из подпрограммы GET_RA в разряде 4 регистра ТЕМРА содержится информация о состоянии кнопки SBI: «1» — не нажата, «0»— нажата.

Подпрограмма SBI VD2 анализирует состояние разряда 4 регистра ТЕМРА и, в зависимости от него, зажигает или гасит светодиод. В системе команд MK PICI6F84 нет команд условного перехода, поэтому для организации проверки того или иного условия используются команды, позволяющие пропустить выполнение следующей команды программы, в зависимости от состояния определенного бита в заданном регистре (BTFSS и BTFSC). В частности, команда BTFSS ТЕМР4 пропускает исполнение команды GOTO Р0, если ТЕМР4 = 1 (кнопка не нажата). Тем самым реализуется команда BSF VD2, которая зажигает светодиод VD2. Затем анализируется условие ТЕМР4 = 0 (кнопка нажата) и, если оно имеет место, светодиод гасится.

Возможна более простая реализация заданного алгоритма, поскольку нажатое состояние кнопки исключает не нажатое (и наоборот), но представленный вариант более нагляден.

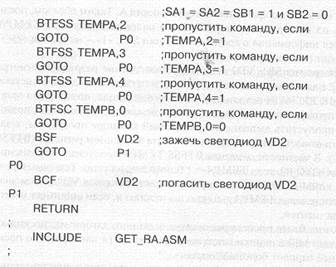

Рассмотрим более сложный вариант программы, предусматривающий зажигание светодиода VD2 только при следующем состоянии тумблеров и кнопок макета: SAI = 1, SA2 = 1, SBI = 1 и SB2 = 0.

Подпрограммы GET_RA и GET_RB помещают в регистры TEMPA и TEMPB текущие состояния портов А и В, соответственно. Подпрограмма ZAG_1110 анализирует состояния разрядов 2,3 и 4 регистра TEMPA и разряда 0 регистра TEMPB, и при условии TEMPA,2,3,4 = 1,1,1 и TEMPB,0 = 0, зажигает светодиод VD2. При невыполнении хотя бы одного из этих условий светодиод гасится.

Использование директивы INCLUDE GET_PORTA.ASM позволяет включать уже отлаженные модули подпрограмм в текущую программу. Для того чтобы этой возможностью можно было воспользоваться, необходимо сохранять отлаженные модули в виде отдельных ассемблерных файлов.

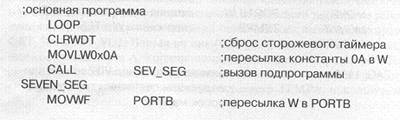

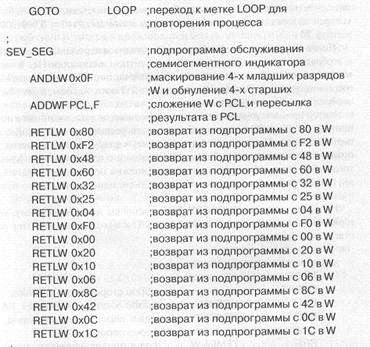

Попробуем теперь использовать семисегментный индикатор для контроля состояния тумблеров макета. Вначале напишем программу, которая выводит на индикатор HL семисегментное изображение любого двоичного числа от 0b до 1111b в шестнадцатеричном представлении.

Программа начинает свою работу с пересылки константы 0х0А в рабочий регистр W. Затем производится вызов подпрограммы обслуживания семисегментного индикатора SEV_SEG. Работа подпрограммы SEV_SEG начинается с маскирования 4-х младших разрядов W и обнуления 4-х старших. Тем самым из анализа исключаются старшие разряды передаваемого из рабочего регистра W числа. Затем маскированное содержимое регистра W добавляется к текущему состоянию младшего байта счетчика команд PCL, и результат помещается в PCL. Таким образом, производится дополнительное смещение счетчика команд на величину, которая была передана в рабочем регистре. Например, если было W=0, то содержимое счетчика команд не изменится, и будет выполнена следующая команда RETLW 0х80, которая вызовет возврат из подпрограммы с записью 0х80 = В'1000000' в регистр W. Если, как было в приведенной программе, W=0A, то к содержимому PCL будет добавлено число 0х0А, и произойдет дополнительное смещение на 10 шагов. В результате будет выполнена команда RETLW 0x10, которая вызовет возврат из подпрограммы с записью 0x10 = В'0001000' в регистр W.

После возврата из подпрограммы производится пересылка W в PORTB и отображение его состояния на семисегментном индикаторе HL. В частности, если W = 0, то при выводе 1000000b на порт В семисегментный индикатор покажет , а при W = А покажет.Таким образом, может быть отображено любое 4-разрядное двоичное число.

Метод прямого управления счетчиком команд, использованный в подпрограмме SEV_SEG, может применяться для реализации табличной конвертации чисел. При этом необходимо иметь в виду, что данный метод не позволяет конвертировать более 256 значений в одной таблице. Кроме того, программа табличной конвертации должна целиком располагаться внутри 256-байтного блока во избежание переполнения младшего байта счетчика команд.

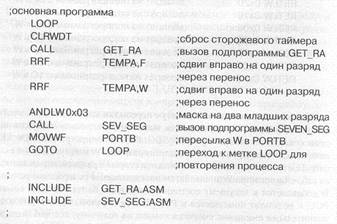

Используя подпрограмму SEV_SEG, напишем теперь программу, которая читает состояния тумблеров SA1 и SA2 и выводит на индикатор соответствующее число.

Подпрограмма GET_RA помещает в регистр TEMPA текущее состояние порта А. Таким образом, в разрядах 2 и 3 регистра TEMPA хранится текущее состояние тумблеров SA1 и SA2. Для того чтобы биты состояния тумблеров заняли позиции 0 и 1 регистра TEMPA, производится два сдвига вправо через перенос, причем результат второго сдвига помещается в регистр W. Затем накладывается маска на два младших разряда рабочего регистра и производится вызов подпрограммы SEV_SEG. После выхода из подпрограммы результат подается на порт В и отображается на индикаторе.

Рассмотрим теперь программы, работающие в реальном масштабе времени, т.е. выдающие сигналы определенной длительности и частоты следования, либо учитывающие временные параметры входных сигналов. Основным элементом таких программ является подпрограмма формирования временной задержки. Рассмотрим один из возможных вариантов такой подпрограммы с использованием программных методов формирования задержки, т.е. без применения встроенного таймера.

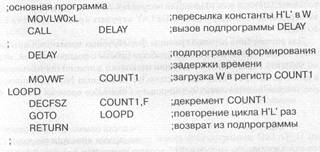

Основная программа производит вызов подпрограммы DELAY c некоторой константой 1. в рабочем регистре W, определяющей число внутренних циклов подпрограммы. Подпрограмма DELAY начинает свою работу с загрузки содержимого рабочего регистра в регистр пользователя COUNT1. Команда DECFSZ COUNT1,F уменьшает на единицу содержимое регистра QOUNT1 и проверяет его на равенство нулю. Нулевое состояние регистра COUNT1 приводит к выходу из цикла и возврату из подпрограммы. Для исполнения каждого внутреннего цикла требуется три машинных цикла МК (1 цикл на исполнение команды DECFSZ при ненулевом результате и 2 цикла на каждую команду GOTO). Выход из подпрограммы DELAY потребует 4-х циклов (2 цикла на исполнение команды DECFSZ при нулевом результате и 2 цикла на RETURN). Если добавить к этому еще 4 цикла, необходимых для загрузки константы в рабочий

регистр, вызова подпрограммы и загрузки регистра пользователя COUNT1, то общее время исполнения подпрограммы DELAY (задержка) составит

ТD = 4 + 3*(L — 1) + 4 = 5 + 3*L циклов,

где L — константа, переданная через рабочий регистр в подпрограмму DELAY.

При тактовой частоте fosc = 2МГц время цикла равно t, = 2 мкс, поэтому при загрузке L = Н'00' = .0 максимальный формируемый интервал времени составит 1,55 мс. Такой результат связан с тем, что команда DECFSZ сначала декрементирует содержимое регистра (Н'00' — 1 = Н'FF'), а затем уже анализирует результат.

Минимальный формируемый интервал времени составит при тех же условиях 5 циклов или 10 мкс. Для получения такого интервала необходимо перед вызовом подпрограммы DELAY загрузить в рабочий регистр число 0х01.

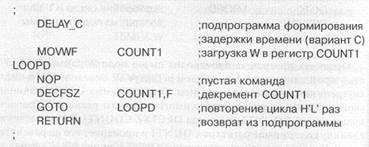

Для расширения верхней границы формируемых временных интервалов, а также с целью повышения удобства работы с подпрограммой, можно добавить в цикл LOOPD одну или несколько дополнительных команд, в качестве которых чаще всего используется команда NOP. Для примера рассмотрим подпрограмму формирования задержки времени DELAY_С

Общее время исполнения подпрограммы DELAY C, включая ее вызов, составит

ТD = 4 + 4*(L — 1) + 4 = 4 + 4*L циклов.

При тактовой частоте fosc = 2МГц и загрузке константы L = Н'F9' = .249 формируемый интервал времени составит ровно 2 мс. Уменьшение константы на единицу уменьшает формируемый временной интервал на 8 мкс. В частности, при L = .124 образуется задержка в 1 мс.

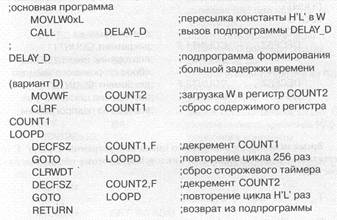

Для формирования больших задержек времени, лежащих в диапазоне долей и единиц секунд, такой подход неудобен. В этом случае используются вложенные циклы, как показано в следующем примере.

Время исполнения внутреннего цикла подпрограммы DELAY_D составляет 3*256 + 4 машинных циклов МК, поэтому общая задержка составит

ТD = 5+ (3*256+ 4)*L циклов.

При тактовой частоте fosc = 2МГц время цикла равно t = 2 мкс, поэтому при загрузке L = Н'00' = .0 максимальный формируемый интервал времени составит около 0,4 с.

Поскольку формируемый интервал времени достаточно велик, во внешний цикл включена команда сброса сторожевого таймера.

Интервал времени 0,4 с не совсем удобен для получения задержек времени, кратных секунде, поэтому рассмотрим еще один вариант подпрограммы формирования больших задержек времени с дополнительной командой NOP во внутреннем цикле.

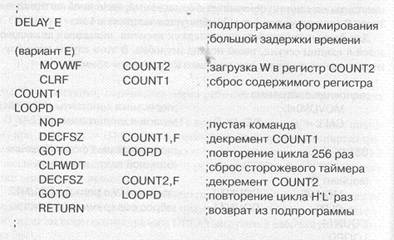

Время исполнения внутреннего цикла подпрограммы DELAY_E составляет 4*256 + 4 машинных циклов МК, поэтому общая задержка составит

ТD = 5 + (4*256 + 4)*L циклов.

При тактовой частоте fosc = 2МГц и при загрузке L = Н'Р3' = .243 формируемый интервал времени составит около 0,5 с при погрешности не более 0,2%. Если необходима более высокая точность, можно вставить необходимое количество пустых операций во внешний цикл формирования задержки.

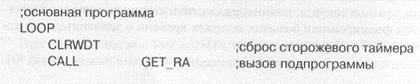

Рассмотрим далее несколько программ с использованием подпрограмм формирования задержки времени. Начнем с написания программы, которая подает звуковой сигнал на динамик ВА1 при нажатии на кнопку SB1. Динамик будет звучать только в том случае, если на выход RA0 будет подан периодически изменяющийся сигнал. Для того чтобы звук был хорошо слышен, его частота должна находиться вблизи максимума слышимости человеческого уха. Выберем частоту звучания равной 1 КГц, что соответствует периоду следования импульсов сигнала 1 мс.

Как и раньше, подпрограмма GET_RA считывает текущее состояние порта А, которое затем передается в регистр ТЕМРА. Подпрограмма SB1_ВА1 анализирует состояние разряда 4 регистра ТЕМРА и, в зависимости от результата, озвучивает динамик ВА1 или нет. Необходимая выдержка линии RA0 в единичном и нулевом состояниях обеспечивается подпрограммой DELAY_С с параметром 1. = Н'3E' = .62. Это соответствует времени задержки около 0,5 мс, что и дает в результате необходимую частоту следования сигнала 1 Кгц.

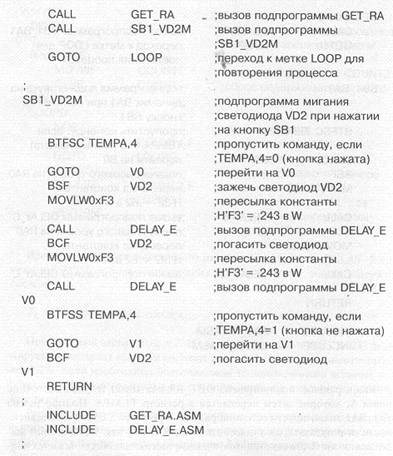

Рассмотрим далее программу, которая заставляет мигать светодиод ЧР2 при нажатии на кнопку SB1. Для того чтобы мигания были хорошо видны, выберем их частоту равной 1 Гц.

Программа работает почти так же, как и предыдущая. Первое отличие заключается в том, что светодиод принудительно гасится при не нажатой кнопке. Второе отличие заключается в величине интервала времени, который составляет здесь 0,5 с и формируется подпрограммой DЕLAY_E.

Подпрограммы формирования задержки времени могут быть также полезны при работе с такими внешними источниками сигналов, как тумблеры, кнопки, переключатели и т.п. Дело в том, что все механические коммутаторы имеют одно негативное свойство, известное как «дребезг» контактов, которое обусловлено механическими колебаниями контактов при их замыкании и размыкание. Длительность колебаний составляет обычно несколько миллисекунд, в течение которых на вход МК может поступать пачка импульсов вместо идеального перепада.

Аппаратные способы борьбы с «дребезгом» контактов основаны на использовании RS-триггеров, одно вибраторов или триггеров Шмитта. В устройствах на основе МК подавление «дребезга» контактов обычно осуществляется программными способами, которые основаны на повторном считывании состояния линии порта через определенное время.

В качестве примера рассмотрим «бездребезговый» вариант подпрограммы чтения состояния порта А.

Суть работы подпрограммы заключается в повторном чтении состояния порта А спустя некоторое время после предыдущего и сравнении его с прежним значением. Константа Н'0А = .10, пересылаемая в регистр W перед вызовом подпрограммы DЕLAY_E, обеспечивает значение задержки времени около 20 мс — этого, как правило, достаточно для завершения переходных процессов при переключении механических коммутаторов. Маскирование неиспользуемых разрядов порта повышает надежность работы подпрограммы. Сброс сторожевого таймера перед вызовом подпрограммы задержки нужен для исключения сброса МК между двумя процедурами опроса порта А.

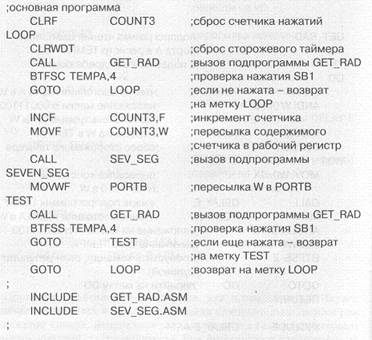

Рассмотрим теперь работу программы, которая использует некоторые из разработанных ранее подпрограмм. Пусть целью работы программы является подсчет числа нажатий на кнопку SB1 с выводом результата на семисегментный индикатор в шестнадцатеричном коде.

Приведенные в главе программы не охватывают и малой доли возможностей, которые предоставляет даже такой простой макет, как изображенный на рис. 6.3. Однако их освоение, надеюсь, будет полезным для начинающих пользователей РIС-контроллеров.

Глава 7. Организация персонального компьютера

Лекция 13. Архитектура и процессоры персональных компьютеров

В этой лекции рассказывается об особенностях архитектуры персональных компьютеров семейства IBM РС, о процессорах, применяемых в персональных компьютерах, об их функциях, характеристиках, этапах их эволюции.

Ключевые слова: архитектура, системные устройства, распределение памяти, чип сет, кэш, защищенный режим, многозадачный режим.

Как уже отмечалось, персональный компьютер представляет собой наиболее развитый вид микропроцессорных систем. На основе персональных компьютеров можно строить самые сложные контрольно-измерительные, управляющие, вычислительные и информационные системы. Имеющиеся в персональном компьютере аппаратные и программные средства делают его универсальным инструментом для самых разных задач.

В случае вычислительных и информационных систем персональный компьютер не нуждается в подключении нестандартной аппаратуры, все сводится к подбору или написанию необходимого программного обеспечения. В случае же контрольно-измерительных и управляющих систем персональный компьютер оснащается набором инструментов для сопряжения с внешними устройствами и соответствующими программными средствами. Во многих случаях строить систему на основе персонального компьютера оказывается гораздо проще, быстрее и даже дешевле, чем проектировать ее с нуля на базе какого-то микропроцессора, микропроцессорного комплекта или микроконтроллера.

Конечно, в большинстве случаев система на основе персонального компьютера оказывается сильно избыточной, это плата за универсальность. Но в то же время один и тот же компьютер может решать самые разнообразные задачи. Например, в системе управления технологическими процессами или научными установками он может математически моделировать происходящие процессы, выдавать в реальном времени управляющие сигналы, принимать в реальном времени ответные сигналы, накапливать информацию, обрабатывать ее, обмениваться информацией с другими компьютерами и т.д. Развитый интерфейс пользователя (видеомонитор, полноразмерная клавиатура мышь) делают работу с персональным компьютером комфортной и эффективной. А стоимость персональных компьютеров вследствие большого объема выпуска постоянно снижается. Поэтому их использование не только удобно, но и экономически выгодно.

Но чтобы грамотно и полноценно использовать персональный компьютер в составе любых систем, надо иметь представление о его архитектуре, об основных принципах построения, об устройствах, входящих в его состав, наконец, о внешних интерфейсах.

7.1. Архитектура персонального компьютера

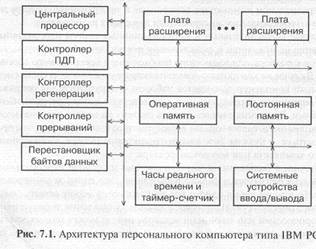

Персональный компьютер типа IBM РС имеет довольно традиционную архитектуру микропроцессорной системы и содержит все обычные функциональные узлы: процессор, постоянную и оперативную память, устройства ввода/вывода, системную шину, источник питания (рис.7.1). Основные особенности архитектуры персональных компьютеров сводятся к принципам компоновки аппаратуры, а также к выбранному набору системных аппаратных средств.

Функции основных узлов компьютера следующие:

•Центральный процессор — это микропроцессор со всеми необходимыми вспомогательными микросхемами, включая внешнюю кэш память и контроллер системной шины. (О кэш-памяти подробнее будет рассказано в следующих разделах). В большинстве случаев именно центральный процессор осуществляет обмен по системной шине.

•Оперативная память может занимать почти все адресуемое пространство памяти процессора. Однако чаще всего ее объем гораздо меньше. В современных персональных компьютерах стандартный объем системной памяти составляет, как правило, от 64 до 512 Мбайт. Оперативная память компьютера выполняется на микросхемах динамической памяти и поэтому требует регенерации.

•Постоянная память (ROM BIOS — Вазе Input/Output System) имеет небольшой объем (до 64 Кбайт), содержит программу начального запуска, описание конфигурации системы, а также драйверы (программы нижнего уровня) для взаимодействия с системными устройствами.

•Контроллер прерываний преобразует аппаратные прерывания системной магистрали в аппаратные прерывания процессора и задает адреса векторов прерывания. Все режимы функционирования контроллера прерываний задаются программно процессором перед началом работы.

•Контроллер прямого доступа к памяти принимает запрос на ПДП из системной магистрали, передает его процессору, а после предоставления процессором магистрали производит пересылку данных между памятью и устройством ввода/вывода. Все режимы функционирования контроллера ПДП задаются программно процессором перед началом работы. Использование встроенных в компьютер контроллеров прерываний и ПДП позволяет существенно упростить аппаратуру применяемых плат расширения.

•Контроллер регенерации осуществляет периодическое обновление информации в динамической оперативной памяти путем проведения по шине специальных циклов регенерации. На время циклов регенерации он становится хозяином (задатчиком) шины.

•Перестановщнк байтов данных помогает производить обмен данными между 16-разрядным и 8-разрядным устройствами, пересылать целые слова или отдельные байты.

•Часы реального времени и таймер-счетчик — это устройства для внутреннего контроля времени и даты, а также для программной выдержки временных интервалов, программного задания частоты и т.д.

•Системные устройства ввода/вывода — это те устройства, которые необходимы для работы компьютера и взаимодействия со стандартными внешними устройствами по параллельному и последовательному интерфейсам. Они могут быть выполнены на материнской плате, а могут располагаться на платах расширения.

• Платы расширения устанавливаются в слоты (разъемы) системной магистрали и могут содержать оперативную память и устройства ввода/вывода. Они могут обмениваться данными с другими устройствами на шине в режиме программного обмена, в режиме прерываний и в режиме ПДП. Предусмотрена также возможность захвата шины, то есть полного отключения от шины всех системных устройств на некоторое время.

Важная особенность подобной архитектуры — ее открытость, то есть возможность включения в компьютер дополнительных устройств, причем как системных устройств, так и разнообразных плат расширения. Открытость предполагает также возможность простого встраивания программ пользователя на любом уровне программного обеспечения компьютера.

Первый компьютер семейства, получивший широкое распространение, IBM PC ХТ, быть выполнен на базе оригинальной системной магистрали PC ХТ-Bus. В дальнейшем (начиная с IBM PC АТ) она была доработана до магистрали, ставшей стандартной и получившей название ISA (Industry Standard Architecture). До недавнего времени ISA оставалась основой компьютера. Однако, начиная с появления процессоров i486 (в 1989 году), она перестала удовлетворять требованиям производительности, и ее стали дублировать более быстрыми шинами: VLB (VESA Local Bus) и PCI (Peripheral Component Interconnect bus) или заменять совместимой с ISA магистралью EISA (Enhanced ISA). Постепенно шина PCI вытеснила конкурентов и стала фактическим стандартом, а начиная с 1999 года в новых компьютерах рекомендуется полностью отказываться от магистрали ISA, оставляя только PCI. Правда, при этом приходится отказываться от применения плат расширения, разработанных за долгие годы для подключения к магистрали ISA.

Другое направление совершенствования архитектуры персонального компьютера связано с максимальным ускорением обмена информацией с системной памятью. Именно из системной памяти компьютер читает все исполняемые команды, и в системной же памяти он хранит данные. То есть больше всего обращений процессор совершает именно к памяти. Ускорение обмена с памятью приводит к существенному ускорению работы всей системы в целом.

Но при использовании для обмена с памятью системной магистрали приходится учитывать скоростные ограничения магистрали. Системная магистраль должна обеспечивать сопряжение с большим числом устройств, поэтому она должна иметь довольно большую протяженность; она требует применения входных и выходных буферов для согласования с линиями магистрали. Циклы обмена по системной магистрали сложны, и ускорять их нельзя. В результате существенного ускорения обмена процессора с памятью по магистрали добиться невозможно.

Разработчиками был предложен следующий подход. Системная память подключается не к системной магистрали, а к специальной высокоскоростной шине, находящейся «ближе» к процессору, не требующей сложных буферов и больших расстояний. В таком случае обмен с памятью идет с максимально возможной для данного процессора скоростью, и системная магистраль не замедляет его. Особенно актуальным это становится с ростом быстродействия процессора (сейчас тактовые частоты процессоров персональных компьютеров достигают 1 — 3 ГГц).

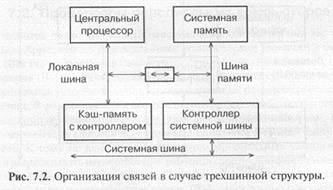

Таким образом, структура персонального компьютера из одношинной, применявшейся только в первых компьютерах, становится трехшинной (рис. 7.2).

Назначение шин следующее:

• к локальной шине подключаются центральный процессор и кэш память (быстрая буферная память);

• к шине памяти подключается оперативная и постоянная память компьютера, а также контроллер системной шины;

• к системной шине (магистрали) подключаются все остальные устройства компьютера.

Все три шины имеют адресные линии, линии данных и управляющие сигналы. Но состав и назначение линий этих шин не совпадают между собой, хотя они и выполняют одинаковые функции. С точки зрения процессора, системная шина (магистраль) в системе всего одна, по ней о» получает данные и команды и передает данные как в память, так и в устройства ввода/вывода.

Временные задержки между системно памятью и процессором в дан ном случае минимальны, так как локальная шина и шина памяти соединены только простейшими быстродействующими буферами. Еще меньше задержки между процессором и кэш-памятью, подключаемой непосредственно к локальной шине процессора и служащей для ускорения обмен процессора с системной памятью.

Если в компьютере применяются две системные шины, например, IS3 и РС1, то каждая из них имеет свой собственный контроллер шины, и работают они параллельно, не влияя друг на друга. Тогда получается уже четырехшинная, а иногда и пятишинная структура. Пример такой структуры компьютера приведен на рис. 7.3.

В наиболее распространенных настольных компьютерах класса Desktop в качестве конструктивной основы используется системная или материнская плата (motherboard), на которой располагаются все основные системные узлы компьютера, а также несколько разъемов (слотов) системной шины для подключения дочерних плат — плат расширения (интерфейсных модулей, контроллеров, адаптеров). Как правило, современные системные платы допускают замену процессора, выбор его тактовой частоты, замену и наращивание оперативной памяти, выбор режимов работы других узлов.

На системной плате сейчас обычно располагаются также основные средства внешнего интерфейса, служащие для присоединения как встроенных устройств (например, дисковых носителей), так и внешних устройств компьютера (например, клавиатуры, мыши, принтера, сканера, модема). Для подключения видеомонитора, как правило, используется специальная плата расширения (контроллер дисплея), вставляемая в один из слотов. Это позволяет заменять ее более мощной при необходимости установки нового монитора.

Отметим, что для получающих все более широкое распространение портативных персональных компьютеров класса ноутбуков (notebook) применяются несколько иные конструктивные решения. В частности, в них отсутствуют слоты расширения системной шины, а практически все узлы компьютера выполняются на одной плате. Но мы в основном будем говорить о компьютерах типа desktop (настольных), так как именно они наиболее приспособлены для построения сложных систем, допускают довольно простую модернизацию (upgrade) и настройку на конкретные нужды пользователя.

7.2. Процессоры персональных компьютеров

Несмотря на то, что первый персональный компьютер был выпущен фирмой Apple, сейчас персональными компьютерами называют в основном IBM PC-совместимые компьютеры. Это связано, прежде всего, с тем, что фирма IBM выбрала правильную рыночную политику: она не скрывала принципов устройства своих компьютеров и не патентовала основных решений. В результате многие производители стали выпускать совместимые компьютеры, и они быстро стали фактическим стандартом. Из-за большого объема выпуска персональные компьютеры начали быстро дешеветь. К тому же для IBM-совместимых персональных компьютеров стали разрабатывать множество программных средств, что еще больше способствовало их распространению. Поэтому, несмотря на некоторые существенные архитектурные недостатки, IBM-совместимые персональные компьютеры сейчас уверенно занимают первое место на рынке.

С самого начала фирма IBM ориентировалась на процессоры Intel. У этих процессоров были очень мощные конкуренты, например, процессоры фирм Motorola или Zilog, превосходившие процессоры Intel по многим параметрам, но именно благодаря персональным компьютерам процессоры Intel смогли выйти победителями в конкурентной борьбе. К тому же еще некоторые фирмы (например, AMD, VIA, Cyrix) выпускают Intel совместимые процессоры. Поэтому мы рассмотрим основные особенности процессоров фирмы Intel. Это позволит нам также проследить основные тенденции в развитии процессоров за последние десятилетия.

Свой первый 16-разрядный процессор i8086 фирма Intel выпустила в 1978 году. Он мог адресовать 1 Мбайт памяти (то есть имел 20-разрядную шину адреса), производительность его при тактовой частоте 5 МГц составляла 0,33 MIPS, но вскоре появились процессоры с тактовой частотой 8 и 10 МГц. Чуть позже (через год) была выпущена упрощенная версия процессора i8086 — i8088, который отличался только 8-разрядной внешней шиной данных. За счет этого он был медленнее, чем i8086, на 20 — 60% при той же тактовой частоте, но зато заметно дешевле. Именно на его основе был собран очень популярный персональный компьютер IBM РС ХТ.

16-разрядный процессор i80286, выпущенный в 1982 году, был использован в персональных компьютерах IВМ РС АТ. Принципиально новым было в нем то, что он мог адресовать до 16 Мбайт памяти и имел помимо реального режима, аналогичного i8086, еще и так называемый защищенный режим, позволяющий более гибко управлять памятью. Производительность этого процессора при тактовой частоте 8 МГц составляла 1,2 M I PS.

Важным шагом стало появление в 1985 году полностью 32-разрядного процессора i80386, способного адресовать до 4 Гбайт памяти (32-разрядная адресная шина). Он имел еще более развитую систему управления памятью M MU (Memory Management Unit). Производительность его при тактовой частоте 16 МГц составляла 6 MIPS. С появлением этого процессора стала бурно развиваться операционная система MS Windows, существенно изменившая процесс работы с компьютерами типа IВМ РС.

Еще одним принципиальным шагом стало создание в 1989 году процессора 1п1е! 486DX, в котором появились встроенный математический сопроцессор, существенно ускоривший выполнение арифметических операций, и внутренняя кэш-память, ускоряющая обмен с оперативной памятью. Максимальный объем адресуемой памяти этого процессора — 4 Гбайт. На тактовой частоте 25 МГц производительность была 16,5 MIPS. Начиная с процессора 486, получило распространение так называемое умножение тактовой частоты, то есть внутреннее удвоение и даже учетверение внешней тактовой частоты (обозначается 486DX2, 486DX4).

В 1995 году появились первые процессоры Pentium, открывшие новый этап в развитии семейства. Они были 32-разрядными внутри, но имели 64-разрядную внешнюю шину данных. Принципиальным отличием было использование в них так называемой суперскалярной архитектуры, следствием чего стало более высокое быстродействие при той же тактовой частоте, что и i486DX. При тактовой частоте 66 М Гц производительность процессора достигала 112 МIРS. В 1996 году тактовая частота Pentium была доведена до 200 МГц, а стоимость снизилась настолько, что он стал рядовым процессором персональных компьютеров семейства IBM РС.

В 1997 году Pentium был дополнен технологией ММХ, призванной ускорять выполнение мультимедийных приложений (обработку изображений и звука). И в этом же году появился процессор Pentium II, который включает в себя технологию ММХ и имеет более высокое быстродействие. Возможная тактовая частота достигла 400 МГц.

В последние годы появились процессоры Pentium III и Pentium IV, имеющие еще более развитую архитектуру и тактовую частоту, превышающую 1 ГГц у Pentium III и 3 ГГц у Pentium IV.

Таким образом, содружество компании Intel и производителей IBM совместимых персональных компьютеров успешно продолжается. Другие фирмы, выпускающие процессоры, вряд ли существенно потеснят в ближайшие годы Intel. Поэтому рассмотрим чуть подробнее характерные особенности процессоров для персональных компьютеров этой компании.

7.2.1. Особенности процессоров 8086/8088

Описание микропроцессоров фирмы Intel мы начнем с процессоров i8086/8088. Именно заложенные в них архитектурные решения во многом определили архитектуру последующих моделей семейства Intel, поддерживающих совместимость с более ранними моделями. В том числе и с недостатками и ограничениями предыдущих моделей.

Процессор i8086 имеет совмещенную (мультиплексированную) 20-разрядную внешнюю шину адреса/данных. Данные передаются по 16 разрядам, адрес — по 20 разрядам. Шина управления имеет 16 разрядов (в частности, в нее входят строб адреса и стробы обмена с памятью и устройствами ввода/вывода). Среднее время выполнения команды занимает 12 тактов синхронизации, один цикл обмена по внешней шине требует 4 тактов (без учета тактов ожидания, вводимых при асинхронном обмене). У процессора i8088 внешняя шина данных 8-разрядная.

Одна из характерных особенностей процессоров i8086/8088 — принцип сегментирования памяти. То есть вся память представляется не в виде непрерывного пространства, а в виде нескольких кусков — сегментов заданного размера (по 64 Кбайта), положение которых в пространстве памяти можно программно изменять. Об этом уже говорилось в разделе 3.1.2 (см. рис. 3.5 и 3.6).

Процессор 8086/8088 имеет 14 регистров разрядностью по 16 бит. Об их назначении также уже говорилось в разделе 3.2.

Для ускорения выборки команд из памяти в процессоре 8086 предусмотрен внутренний 6-байтный конвейер (в процессоре 8088 — 4-байтный). Конвейер заполняется читаемыми из памяти командами во время выполнения предыдущей команды и сбрасывается (считается пустым) при выполнении любой команды перехода (даже если это команда перехода на следующий адрес).

Система команд процессора включает в себя 133 команды, поддерживающие 24 метода адресации операндов. Такое большое число команд может рассматриваться как достоинство (можно гибко выбирать команду, оптимально подходящую для каждого конкретного случая), но оно же заметно усложняет структуру процессора.

Каждая команда содержит 1, 2 или 4 байта кода команды, за которыми могут следовать 1, 2 или 4 байта операнда.

В процессоре предусмотрены программные и аппаратные прерывания, разделение внешней шины с другими процессорами или с контроллером прямого доступа к памяти, а также возможность подключения математического сопроцессора i8087, существенно увеличивающего производительность вычислений.

При старте процессора (по внешнему сигналу RESET) он переходит в адрес памяти FFFFO и начинает выполнение программы, которая размещается начиная с этого адреса.

Процессор может обрабатывать 256 типов прерываний: внешних (аппаратных), программных и внутренних. Векторы прерываний представляют собой двойное слово (два слова по 16 разрядов), определяющее сегмент и смещение начального адреса программы обработки прерываний. Для векторов прерываний отведена область памяти с адресами 00000...003FF. Внутренние прерывания вырабатываются при особых ситуациях:

• прерывание 0 соответствует переполнению при делении на нуль;

• прерывание 1 вырабатывается после каждой команды при установленном флаге трассировки TF в регистре состояния процессора (см. раздел 3.2);

• прерывание 4 вырабатывается по специальной команде INTO, если установлен флаг переполнения OF в регистре состояния процессора (это условное прерывание по переполнению).

Особое место занимает немаскируемое прерывание NMI (Non-Masked Interrupt), которое вырабатывается при поступлении внешнего сигнала NMI и не зависит от состояния флага разрешения аппаратных прерываний IF. В компьютере оно используется для контроля четности памяти, контроля корректности обмена с памятью и устройствами ввода/вывода, а также для обработки так называемых исключений, то есть особых условий, возникающих в процессе работы. Немаскируемым оно называется именно потому, что его нельзя запретить.

Важная отличительная особенность процессора — разделение операций обмена с устройствами ввода/вывода и с памятью. Для обмена с устройствами ввода/вывода используются как отдельные команды ввода и вывода, так и специальные управляющие сигналы на шине управления. Адреса и данные как при обмене с памятью, так и при обмене с устройствами ввода/вывода передаются по одним и тем же шинам. Но если для обмена с памятью используются все 20 разрядов шины адреса (адресуется 1 Мбайт — адреса 00000 ... FFFFF), то в циклах обмена с устройствами ввода/вывода — только 16 разрядов шины адреса (адресуется 64 Кбайта — адреса 00000 ... 0FFFF). Такой подход имеет как свои преимущества (например, упрощение реализации прямого доступа к памяти), так и недостатки (усложнение системы команд, увеличение количества управляющих сигналов).

Микропроцессоры i8086/8088 выполнены в виде интегральной микросхемы в 40-выводном корпусе. Отличие в назначении выводов микро схемы между ними только одно: адрес в процессоре 8088 не мультиплексирован с данными (передается по отдельным линиям), а в процессоре 8086 — мультиплексирован.

Процессор работает от одного источника питания напряжением +5В и требует внешнего тактирующего сигнала с частотой, определяемой номером модели (от 4,77 МГц до 10 МГц).

Специальный управляющий сигнал MN/МХ определяет минимальный или максимальный режим работы процессора. В минимальном режиме процессор сам вырабатывает сигналы управления для внешней шины. Этот режим используется для построения простейших систем. Для работы в составе компьютера применяется максимальный режим, при котором сигналы управления внешней шиной вырабатываются специальной микро схемой контроллера шины i8288.

7.2.2. Особенности процессора 80286

Несмотря на то, что процессор 80286 остался 16-разрядным, как и ей предшественник 8086, он представлял собой новое поколение процессоров, что определило его высокую популярность и обеспечило персональному компьютеру на его основе (IBM РС АТ) довольно долгую жизнь. Этот процессор отличается тем, что он имеет специальные средства для работы в многопользовательских и многозадачных системах.

Наиболее существенное отличие от процессора 8086/8088 — это механизм управления адресацией памяти, который обеспечивает четырехуровневую систему защиты и поддержку виртуальной памяти. (Виртуальная память — это внешняя память большого объема, с которой процессор может взаимодействовать как со своей системной памятью, но с некоторыми ограничениями). Специальные средства предусмотрены также для поддержки механизма переключения задач (Task switching). То есть процессор способен выполнять несколько задач одновременно, переключаясь время от времени между ними. В процессоре 80286 также расширена система команд за счет добавления команд управления защитой и нескольких новых команд общего назначения.

Процессор 80286 может работать в двух режимах:

• Реальный режим (8086 Real Address Mode — режим реальной адресации), полностью совместимый с процессором 8086/8088. В этом режиме возможна адресация только в пределах 1 Мбайта физической памяти. Он используется для обеспечения программной преемственности с процессором 8086/8088.

• Защищенный режим (Protected Virtual Address Mode — защищенный режим виртуальной адресации). В этом режиме возможна адресация в пределах 16 Мбайт физической памяти. Такое решение связано с необходимостью построения компьютеров с большим объемом памяти, которые обеспечивали бы поддержку более сложных программ. В защищенном режиме система команд включает набор команд 8086, расширенный для обеспечения аппаратной поддержки многозадачного режима и виртуальной памяти.

Переключение в защищенный режим осуществляется одной командой (с предварительно подготовленными таблицами дескрипторов, описывающих параметры режима). Естественно, это довольно быстрый процесс. Обратное переключение в реальный режим гораздо сложнее: оно возможно только через аппаратный сброс процессора (по сигналу RESET), что требует гораздо больше времени.

В составе компьютера под управлением операционной системы MS DOS процессор 80286 работает в реальном режиме, а защищенный режим используют операционные системы типа UN 1Х, OS/2, NetWare286, а также операционные системы семейства MS Windows. Подробнее особенности этих режимов будут рассмотрены в следующем разделе.

Как и процессор 8086, 80286 имеет 16-разрядную внешнюю шину данных и 6-байтный конвейер команд. Однако быстродействие процессора 80286 при тактовой частоте 12,5 МГц примерно в 6 раз выше, чем у 8086 с тактовой частотой 5 М Гц. Это достигается за счет усовершенствованной архитектуры и снижения количества тактов на одну команду. Для ускорения выполнения математических операций предусмотрено подключение к процессору 80286 микросхемы математического сопроцессора 80287.

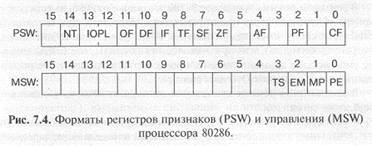

Назначение внутренних регистров процессора 80286 такое же, как у процессора 8086/8088. Но в слове состояния процессора (PSW) добавлены три используемых разряда, и, кроме того, появился еще один внутренний регистр — регистр управления со словом состояния машины

Дополнительные биты слова состояния процессора PSW имеют следующее назначение (подробнее о них — в следующем разделе):

• IOPL (Input/Output Privilege Level) — два бита, определяющие уровень привилегий ввода/вывода;

• NT (Nested Task flag) — флаг вложенной задачи. Регистр MSW управляет режимом процессора. Для изменения его содержимого и сохранения его в памяти предназначены специальные команды. Назначение его битов следующее:

• РЕ (Protection Enable) — разрешение защиты. Установка этого флага переводит процессор в защищенный режим. Но очистка флага не переводит в реальный режим (требуется аппаратный сброс процессора).

• МР (Monitor Processor extension) — мониторинг внешнего математического сопроцессора.

• ЕМ (Processor Extension Emulated) — эмуляция математического сопроцессора.

• TS (Task Switch) — переключение задач. Как и два предыдущих разряда, этот разряд управляет сопроцессором.

Сочетание МР=0 ЕМ=0 TS=0, устанавливаемое по аппаратному сбросу (по сигналу RESET), обеспечивает совместимость с 8086/8088. Сочетание МР=1 ЕМ=0 используется при совместном включении с сопроцессором 80287, а сочетание МР=0 EM=1 применяется в случае программной эмуляции сопроцессора, при которой функции сопроцессора выполняются основным процессором, но гораздо медленнее.

Остановимся подробнее на организации памяти процессора 80286. 24 разрядная внешняя шина адреса позволяет адресовать 16 Мбайт физической памяти, но в реальном режиме доступен только 1 Мбайт, начинающийся с нулевого адреса (000000...OFFFFF). Так же, как и в 8086, применяется сегментация памяти, но управление сегментацией в реальном и защищенном режимах различно.

В реальном режиме процессор 80286 в отличие от 8086, имеет средства контроля перехода через границу сегмента. Например, при попытке обращения к слову, имеющему смещение РРРР (его старший байт выходит за границу сегмента), или при выполнении команды, все байты которой не умещаются в данном сегменте, процессор вырабатывает специальное прерывание — Segment Overrun Interrupt.

В защищенном режиме существуют отличия от 8086, касающиеся определения сегментов:

• Сегментные регистры CS, DS, SS и ES хранят не сами базовые (начальные) адреса сегментов, а селекторы, определяющие адреса в памяти, по которым хранятся дескрипторы (описатели) сегментов. Область памяти с дескрипторами называется таблицей дескрипторов.

• Каждый дескриптор сегмента содержит базовый адрес сегмента, размер сегмента (от 1 до 64 Кбайт) и его атрибуты.

• Базовый адрес сегмента имеет разрядность 24 бит, что и обеспечивает адресацию 16 Мбайт физической памяти.

• Селекторы, загружаемые в 16-битные сегментные регистры, имеют три поля: RPL (Requested Privilege Level) — запрашиваемый уровень привилегий, Tl (Table Indicator) — индикатор использования локальной или глобальной таблицы дескрипторов, INDEX — номер дескриптора в таблице (формат показан на рис. 7.5).

О порядке вычисления адреса памяти в защищенном режиме процессора 80286 уже говорилось в разделе 3.1.2 (см. рис.3.7). На сумматор, вычисляющий физический адрес памяти, подается не содержимое сегментного регистра, а базовый адрес сегмента из таблицы дескрипторов.

Дескрипторы хранятся в памяти и занимают по четыре смежных 16- разрядных слова (то есть 8 байт). При загрузке нового значения селектора дескрипторы считываются из памяти и сохраняются во внутренних программно недоступных (и невидимых) регистрах процессора. До смены значения селектора при обращениях к памяти используются значения дескрипторов только из этих невидимых регистров (их называют кэш-регистрами).

В защищенном режиме команды ввода/вывода процессора являются привилегированными. Это означает, что они могут выполняться задачами только с определенным уровнем привилегий, определяемых полем IOPL регистра признаков. Несанкционированная попытка выполнения этих команд вызывает прерывание по нарушению защиты.

Как и 8086, процессор 80286 может обрабатывать до 256 типов прерываний. Прерывания подразделяются на аппаратные (маскируемые или немаскируемые), вызываемые сигналами на входах процессора, программные, вызываемые командой INT, и исключения инструкций. При этом аппаратные и программные прерывания работают точно так же, как в 8086/8088.

Исключения инструкций (Instruction Exceptions) или просто исключения случаются при возникновении особых условий при выполнении операций (в 8086 аналогом исключений являлись внутренние прерывания процессора). Обработка исключений проводится аналогично обработке прерываний.

Каждому номеру прерывания соответствует свой элемент в таблице дескрипторов прерываний IDT (Interrupt Descriptor Table). В реальном режиме эта таблица организована так же, как у 8086/8088, то есть содержит двойные слова, определяющие адрес начала процедур обработки прерываний. В защищенном режиме таблица содержит 8-байтные дескрипторы прерываний. Ее размер может быть от 32 до 256 дескрипторов, и располагаться она может в любом месте памяти.

Система команд процессора 80286 включает, помимо полного набора8086, ряд дополнительных команд, например:

• сохранение константы в стеке, сохранение в стеке и восстановление из стека всех регистров одной командой;

• целочисленное умножение на константу;

• сдвиги (включая циклические) на заданное в константе количество шагов;

• вход и выход из процедур;

• команды управления защитой. Попытка выполнения недействительной команды (или попытка выполнения в реальном режиме команды, предназначенной только для защищенного режима) вызывает специальное исключение.

Процессор 80286 выпускался в 68-выводных корпусах. Внешние шины адреса и данных были разделены. Напряжение питания процессора составляет +5В.

7.2.3. Особенности процессора 80386

32-разрядный процессор i80386 открыл новый этап в истории микро процессоров Intel и персональных компьютеров типа 1 ВМ РС. Естественно, он сохранял полную совместимости со своими 16-разрядными предшественниками, чтобы не отказываться от разработанного для них программного обеспечения. Но именно в 80386 преодолено жесткое ограничение на длину непрерывного сегмента памяти в 64 Кбайт, что являлось пережитком прошлого и следствием не самых удачных архитектурных решений 8086.

В защищенном режиме 80386 длина сегмента может достигать 4 Гбайт, то есть всего объема физически адресуемой памяти. Таким образом, память фактически стала непрерывной. Кроме того, 80386 обеспечивает поддержку виртуальной памяти объемом до 64 Тбайт (1 Тбайт = 1024 Гбайт). Встроенный блок управления памятью поддерживает механизмы сегментации и страничной трансляции адресов (Paging). Обеспечивается четырехуровневая система защиты памяти и ввода/вывода, а также переключение задач.

Процессор 80386, как и 80286, может работать в двух режимах:

• Реальный режим, который полностью совместим с 8086.

• Защищенный режим. В этом режиме возможна адресация до 4 Гбайт физической памяти (32 разряда), через которые при использовании механизма страничной адресации может отображаться до 16 Тбайт виртуальной памяти каждой задачи.

Переключение между этими двумя режимами в обе стороны, в отличие от 80286, производится достаточно быстро, с помощью простой последовательности команд, и аппаратного сброса процессора не требуется.

Процессор может оперировать с 8, 16, 32-битными операндами, строками байт, слов и двойных слов, а также с битами, битовыми полями и строками бит.

В архитектуру процессора введены средства отладки и тестирования. Разрядность регистров данных (АХ, BX, СХ, DX) и адресов (SI, DI, ВР, SP) увеличена до 32. При этом в их обозначении появилась приставка Е (Extended — расширенный), например, ЕАХ, ESI. Отсутствие приставки в имени означает ссылку на младшие 16 разрядов соответствующего регистра. Регистры данных и адресов объединены в группу регистров общего назначения, которые иногда могут заменять друг друга. Это может рассматриваться как отход от идеологии специализации всех регистров.

Регистры селекторов оставлены 16-разрядными, но добавлено два новых регистра FS и GS для задания дополнительных сегментов данных. Также расширен до 32 разрядов регистр-указатель (счетчик) команд EIP.

32-разрядным стал и регистр флагов EFLAGS. Его биты, определенные для 8086 и 80286, остались прежними, но добавлены 6 новых бит (рис. 7.6). Такой же формат используется и в процессорах 80486 и Pentium.

Регистры сегментов процессора содержат 16-битные указатели (в реальном режиме) или селекторы (в защищенном режиме) шести сегментов. С каждым из шести сегментных регистров связаны программно недоступные регистры дескрипторов, как и в случае 80286. В защищенном режиме в регистры дескрипторов загружается 32-битный базовый адрес сегмента, 32-битный лимит и атрибуты сегментов.

Помимо упомянутых регистров в состав процессора входят еще четыре управляющих регистра (CRO, CR1, CR2, CR3), которые хранят признаки состояния процессора, общие для всех задач. В процессоре Pentium к ним добавлен еще и регистр CR4. Кроме того, процессор содержит еще системные адресные регистры для ссылок на сегменты и таблицы в защищенном режиме, регистры отладки и регистры тестирования. Как видим, от модели к модели количество регистров процессора постоянно возрастает.

Процессор позволяет выделять в памяти сегменты и страницы. Сегменты в реальном режиме имеют фиксированный размер, в защищенном — переменный. Страницы, которых не было в предыдущих моделях, представляют собой области логической памяти размером 4 Кбайт, каждая из которых может отображаться на любую область физической памяти. Если сегменты используются на прикладном уровне, то страницы применяются на системном.

Применительно к памяти различают три адресных пространства: логическое, линейное и физическое. О принципах адресации памяти у процессора 80386 уже говорилось в разделе 3.1.2 (см. рис. 3.8).

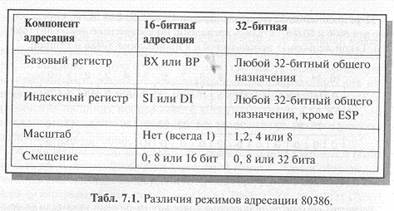

Процессор 80386 может использовать режимы 32-битной или 16-битной адресации. Режим 16-битной адресации соответствует режимам процессоров 8086 и 80286, при этом в качестве компонентов адреса используются младшие 16 бит соответствующих регистров. Отличие 32-битной адресации отражено в табл. 7.1.

Так же, как и предшественники, процессор 80386 обрабатывает все виды прерывания: аппаратные (маскируемые и немаскируемые) и программные, которые в данном случае обрабатываются как разновидность исключений, и собственно исключения. Исключения подразделяются на отказы, ловушки и аварийные завершения.

• Отказ (Fault) — это исключение, которое обнаруживается и обслуживается до выполнения команды, вызывающей ошибку.

• Ловушка (Trap) — это исключение, которое обнаруживается и обслуживается после выполнения команды, вызывающей это исключение. К классу ловушек относятся и программные прерывания.

• Аварийное завершение (Abort) — это исключение, которое не позволяет точно установить команду, вызвавшую его. Оно используется для сообщения о серьезной ошибке, такой как аппаратная ошибка или повреждение системных таблиц.

Каждому номеру прерывания (0...255) или исключения соответствует элемент в таблице дескрипторов прерываний IDT (Interrupt Descriptor Table). В защищенном режиме IDT может иметь размер от 32 до 256 дескрипторов, каждый из которых состоит из 8 байт.

Отличия от предшествующего процессора 80286 в выполнении операций ввода/вывода сводятся к добавлению возможностей обращения к 32 битным портам. Важно отметить, что строковые команды процессора 80386 обеспечивают блочный ввод/вывод с большей скоростью, чем стандартный контроллер прямого доступа к памяти.

Процессор выпускался в 100-выводном корпусе. Была предусмотрена возможность подключения внешнего сопроцессора 80387.

А теперь остановимся чуть подробнее на защищенном режиме, который используется на полную мощность именно начиная с 32-разрядных процессоров, так как процессор 80286 имел существенные ограничения и в большинстве случаев работал все-таки в реальном режиме.

Защищенный режим был предложен для обеспечения независимости одновременного выполнения нескольких задач (как системных, так и прикладных). Для этого предусмотрена защита ресурсов каждой задачи от действий других задач. Под ресурсами здесь понимается память с данными, программами, системными таблицами, а также используемая задачей аппаратура. Защита основывается на сегментации памяти, причем, в отличие от реального режима, задача не может переопределять положения своих сегментов в памяти и использует только сегменты, определенные для нее операционной системой. Сегмент определяется дескриптором сегмента, который задает положение сегмента в памяти, его размер (или лимит), назначение и характеристики защиты.

Защита с помощью сегментации не позволяет:

• использовать сегменты не по назначению, например, трактовать область данных как область программы;

• нарушать права доступа (например, пытаться записывать информацию в сегмент, предназначенный только для чтения, или обращаться к сегменту, не имея достаточных привилегий);

• адресоваться к элементам, выходящим за границу сегмента;

• изменять дескрипторы сегментов, не имея достаточных привилегий. Защищенный режим предусматривает средства переключения задач.

Состояние каждой задачи (то есть состояние всех регистров процессора) хранится в специальном сегменте состояния задачи, на который указывает селектор в регистре задачи. При переключении задачи достаточно загрузить в регистр задачи новый селектор, и состояние предыдущей задачи автоматически сохранится, а в процессор загрузится состояние новой (или ранее прерванной) задачи. Это развитие идеи стека.

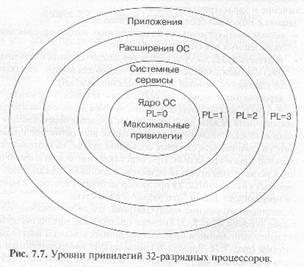

В защищенном режиме предусматривается иерархическая четырехуровневая (уровни 0, 1, 2, 3) система привилегий, предназначенная для управления выполнением привилегированных команд и доступом к дескрипторам (рис. 7.7). Уровень 0 соответствует неограниченным правам доступа и отводится ядру операционной системы. Уровень 3 дает минимальные права и отводится прикладным задачам. Уровни привилегий относятся к дескрипторам, селекторам и задачам. Кроме того, в регистре флагов имеется двух битовое поле привилегий ввода/вывода (см. рис. 7.4 и 7.6), управляющее доступом к командам ввода/вывода и флагом прерываний.

Механизм виртуальной памяти, используемый в защищенном режиме, позволяет любой задаче использовать логическое пространство размером до 64 Мбайт (16К сегментов по 4 Кбайта). Для этого каждый сегмент в своем дескрипторе имеет специальный бит, указывающий на присутствие данного сегмента в оперативной памяти в текущий момент. Неиспользуемый сегмент может быть выгружен из оперативной памяти во внешнюю память (обычно — на диск), о чем делается пометка в его дескрипторе. На освободившееся место из внешней памяти может закачиваться другой сегмент (это называется свопингом или подкачкой). При обращении задачи к отсутствующему в оперативной памяти сегменту вырабатывается специальное исключение, которое и выполняет свопинг. С точки зрения выполняемой программы, виртуальная память ничем не отличается от реальной (говорят, что виртуальная память прозрачна), не считая задержки на процесс перекачки информации на диск и с диска.

Реальное использование системы защиты и виртуальной памяти возлагается на операционную систему, которая в идеале должна обеспечивать работоспособность даже в случае некорректного выполнения прикладных задач.

В памяти существует три типа таблиц дескрипторов: локальная таблица дескрипторов LDT, глобальная таблица дескрипторов GDT и таблица дескрипторов прерываний IDT. Каждой таблице соответствует свой регистр процессора (соответственно, LDTR, GDTR и IDTR), где хранятся дескрипторы сегментов. Глобальная таблица содержит дескрипторы, доступные всем задачам, а локальная может быть для каждой задачи своя.

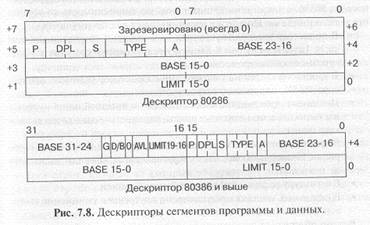

Дескрипторы состоят из 8 байтов (как и у 80286). Однако назначение байтов различно. Для примера на рис. 7.8 показаны форматы дескрипторов сегмента программ и данных процессоров 80286 и 80386.

Существуют также системные сегменты, предназначенные для хранения локальных

таблиц дескрипторов и таблиц состояния задач. Их дескрипторы (тоже 8-байтные) определяют базовый адрес, лимит сегмента, права доступа (чтение, чтение/запись, только исполнение или исполнение/чтение) и присутствие сегмента в оперативной памяти.

Задачи, дескрипторы и селекторы имеют свои уровни привилегий. Привилегии задач действуют на выполнение команд и использование дескрипторов. Текущий уровень привилегии задач определяется двумя младшими битами регистра CS. Привилегии дескриптора описываются полем DPL (рис. 7.8). DPL определяет наименьший уровень привилегий, с которым возможен доступ к данному дескриптору. Привилегии селектора задаются полем RPL (см. рис. 7.5). Привилегии проверяются при попытках записи в сегментные регистры, а также при выполнении некоторых команд.

Таким образом, начиная с процессора 80386, появляются средства обслуживания многозадачного режима. Естественно, процессор не может обрабатывать несколько задач одновременно, выполняя по несколько команд сразу. Он только периодически переключается между задачами. Но с точки зрения пользователя получается, что компьютер параллельно работает с несколькими задачами.