Команды переходов предназначены для организации всевозможных циклов, ветвлений, вызовов подпрограмм и т.д., то есть они нарушают последовательный ход выполнения программы. Эти команды записывают в регистр-счетчик команд новое значение и тем самым вызывают переход процессора не к следующей по порядку команде, а к любой другой команде в памяти программ. Некоторые команды переходов предусматривают в дальнейшем возврат назад, в точку, из которой был сделан переход, другие не предусматривают этого. Если возврат предусмотрен, то текущие параметры процессора сохраняются в стеке. Если возврат не предусмотрен, то текущие параметры процессора не сохраняются.

Команды переходов без возврата делятся на две группы:

• команды безусловных переходов;

• команды условных переходов. В обозначениях этих команд используются слова Branch (ветвление) и Jump (прыжок).

Команды безусловных переходов вызывают переход в новый адрес независимо ни от чего. Они могут вызывать переход на указанную величину смещения (вперед или назад) или же на указанный адрес памяти. Величина смещения или новое значение адреса указываются в качестве входного операнда.

Команды условных переходов вызывают переход не всегда, а только при выполнении заданных условий. В качестве таких условий обычно выступают значения флагов в регистре состояния процессора (PSW). То есть условием перехода является результат предыдущей операции, меняющей значения флагов. Всего таких условий перехода может быть от 4 до 16. Несколько примеров команд условных переходов:

• переход, если равно нулю;

• переход, если не равно нулю;

• переход, если есть переполнение;

• переход, если нет переполнения;

• переход, если больше нуля;

• переход, если меньше или равно нулю. Если условие перехода выполняется, то производится загрузка в регистр-счетчик команд нового значения. Если же условие перехода не выполняется, счетчик команд просто наращивается, и процессор выбирает и выполняет следующую по порядку команду.

Специально для проверки условий перехода применяется команда сравнения (CMP), предшествующая команде условного перехода (или даже нескольким командам условных переходов). Но флаги могут устанавливаться и любой другой командой, например командой пересылки данных, любой арифметической или логической командой. Отметим, что сами команды переходов флаги не меняют, что как раз и позволяет ставить несколько команд переходов одну за другой.

Совместное использование нескольких команд условных и безусловных переходов позволяет процессору выполнять разветвленные алгоритмы любой сложности. Для примера на рис. 3.13 показано разветвление программы на две ветки с последующим соединением, а на рис. 3.14— разветвление на три ветки с последующим соединением.

Команды переходов с дальнейшим возвратом в точку, из которой был произведен переход, применяются для выполнения подпрограмм, то есть вспомогательных программ. Эти команды называются также командами вызова подпрограмм (распространенное название — CALL). Использование подпрограмм позволяет упростить структуру основной программы, сделать ее более логичной, гибкой, легкой для написания и отладки. В то же время надо учитывать, что широкое использование подпрограмм, как правило, увеличивает время выполнения программы.

Все команды переходов с возвратом предполагают безусловный переход (они не проверяют никаких флагов). При этом они требуют одного входного операнда, который может указывать как абсолютное значение нового адреса, так и смещение, складываемое с текущим значением адреса. Текущее значение счетчика команд (текущий адрес) сохраняется перед выполнением перехода в стеке.

Для обратного возврата в точку вызова подпрограммы (точку перехода) используется специальная команда возврата (RET или RTS). Эта команда извлекает из стека значение адреса команды перехода и записывает его в регистр-счетчик команд.

Особое место среди команд перехода с возвратом занимают комары прерываний (распространенное название — INT). Эти команды в качестве входного операнда требуют номер прерывания (адрес вектора). Обслуживание таких переходов осуществляется точно так же, как и аппаратных прерываний. То есть для выполнения данного перехода процессор обращается к таблице векторов прерываний и получает из нее по номеру прерывания адрес памяти, в который ему необходимо перейти. Адрес вызова прерывания и содержимое регистра состояния процессора (PSW) сохраняются в стеке. Сохранение PSW — важное отличие команд прерывания от команд переходов с возвратом.

Команды прерываний во многих случаях оказываются удобнее, чем обычные команды переходов с возвратом. Сформировать таблицу векторов прерываний можно один раз, а потом уже обращаться к ней по мере необходимости. Номер прерывания соответствует номеру подпрограммы, то есть номеру функции, выполняемой подпрограммой. Поэтому команды прерывания гораздо чаще включаются в системы команд процессоров, чем обычные команды переходов с возвратом.

Для возврата из подпрограммы, вызванной командой прерывания, используется команда возврата из прерывания (I RET или RTI). Эта команда извлекает из стека сохраненное там значение счетчика команд и регистра состояния процессора (PSW).

Отметим, что у некоторых процессоров предусмотрены также комары условных прерываний, например, команда прерывания при переполнении. Конечно, в данном разделе мы рассмотрели только основные команды, наиболее часто встречающиеся в процессорах. У конкретных процессоров могут быть и многие другие команды, не относящиеся к перечисленным группам команд. Но изучать их надо уже после того, как выбран тип процессора, подходящий для задачи, решаемой данной микропроцессорной системой.

3.4. Быстродействие процессора

Быстродействие процессора — это одна из важнейших его характеристик, определяющая эффективность работы всей микропроцессорной системы в целом. Быстродействие процессора зависит от множества факторов, что затрудняет сравнение быстродействия даже разных процессоров внутри одного семейства, не говоря уже о процессорах разных фирм и разного назначения.

Выделим важнейшие факторы, влияющие на быстродействие процессора. Прежде всего, быстродействие зависит от тактовой частоты процессора. Все операции внутри процессора выполняются синхронно, тактируются единым тактовым сигналом. Понятно, что чем больше тактовая частота, тем быстрее работает процессор, причем, например, двукратное увеличение тактовой частоты какого-то процессора снижает вдвое время выполнения команд этим процессором.

Однако надо учитывать, что разные процессоры выполняют одинаковые команды за разное количество тактов, причем количество тактов, затрачиваемых на команду, может изменяться от одного такта до десятков или даже сотен. В некоторых процессорах за счет распараллеливания микроопераций на команду тратится даже меньше одного такта.

Количество тактов, затрачиваемых на выполнение команды, зависит от сложности этой команды и от методов адресации операндов. Например, быстрее всего (за меньшее число тактов) выполняются команды пересылки данных между внутренними регистрами процессора. Медленнее всего (за большое число тактов) выполняются сложные арифметические команды с плавающей запятой, операнды которых хранятся в памяти.

Первоначально для количественной оценки производительности процессоров применялась единица измерения MIPS (Mega Instruction Per Second), соответствовавшая количеству миллионов выполняемых инструкций (команд) за секунду. Естественно, изготовители микропроцессоров старались ориентироваться на самые быстрые команды. Понятно, что подобный показатель не слишком удачен. Для измерения производительности при выполнении вычислений с плавающей запятой (точкой) чуть позже была предложена единица FLOPS (Floating point Operations Per Second), но она по определению узкоспециальная, так как в некоторых системах операции с плавающей запятой просто не используются.

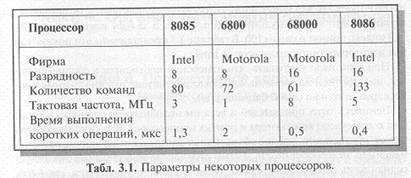

Другой аналогичный показатель быстродействия процессора — время выполнения коротких (быстрых) операций. Для примера в таблице 3.1 представлены показатели быстродействия нескольких 8-разрядных и 16 разрядных процессоров. В настоящее время этот показатель практически не используется, как и MIPS.

Время выполнения команд — важный, но далеко не единственный фактор, определяющий быстродействие. Большое значение имеет также структура системы команд процессора. Например, некоторым процессорам для выполнения какой-то операции понадобится одна команда, а другим процессорам — несколько команд. Какие-то процессоры имеют систему команд, позволяющую быстро решать задачи одного типа, а какие-то — задачи другого типа. Важны и методы адресации, разрешенные в данном процессоре, и наличие сегментирования памяти, и способы взаимодействия процессора с устройствами ввода/вывода и т.д.

Существенно влияет на быстродействие системы в целом и то, как процессор «общается> с памятью команд и памятью данных, применяется ли совмещение выборки команд из памяти с выполнением ранее выбранных команд.

Быстродействие системы в целом определяется также и разрядностью процессора. Например, 8-разрядный процессор будет медленнее пересыпать и обрабатывать большие массивы данных, чем 16-разрядный процессор. Точно так же 16-разрядный процессор будет значительно медленнее работать с большими числами (большими, чем 65536), чем 32-разрядный процессор.

При высокой сложности решаемых задач быстродействие системы зависит и от общего объема системной памяти. Ведь если системной памяти мало, системе приходится сохранять данные во внешней памяти (например, на магнитном диске), а это очень сильно (на несколько порядков) замедляет работу. Так что разрядность шины адреса процессора тоже важна.

Поэтому количественные показатели производительности процессоров очень условны, они лишь косвенно характеризуют быстродействие системы на базе этого процессора. Тем не менее, некоторые производители предлагают количественные показатели для своих процессоров, которые характеризуют время выполнения специально составленных тестовых программ, содержащих самые различные команды в тех или иных соотношениях.

Так, для сравнения производительности 32-разрядных процессоров фирма Intel, производящая процессоры для персональных компьютеров, в 1992 году предложила свою единицу измерения iCOMP Index (Intel COmparative Microprocessor Performance). Для вычисления этого показателя используется смесь 16 и 32-битных целочисленных команд, команд с плавающей точкой, команд обработки графики и видео. В качестве базового взят процессор t486SX-25, чей индекс принят равным 100. В Таблице 3.2 приведены индексы iCOMP для некоторых процессоров фирмы Intel. Как видно из таблицы, за счет более развитой архитектуры процессоры семейства 486 всегда быстрее процессоров семейства 386, а любой Pentium быстрее любого процессора из семейства 486. Тактовая частота (указана в таблице через черточку) определяет производительность только в пределах одного семейства. В 1996 году разработчиками Intel был предложен другой показатель—iCOMP Index 2.0, для вычисления которого не используются 16-разрядные команды, зато введен мультимедийный тест, а за базу взят Pentium-120, чей индекс принят равным 100. В таблице 3.3 представлены эти показатели для некоторых типов процессоров Intel.

При этом надо учитывать, что измерения проводятся в составе системы, настроенной на максимальное быстродействие именно данных процессоров, и только самой фирмой Intel.

Ценность этих показателей и всех им подобных не слишком велика. Для конкретного компьютера и разных процессоров величина показателя может предоставить вполне объективные данные, позволяющие оценить, например, целесообразность замены процессора на более мощный. Но усредненность показателей iCOMP не позволяет точно сказать, как будет себя вести процессор в различных задачах, которые ориентированы на преимущественное использование разных типов команд.

Точная оценка быстродействия процессора возможна только в составе конкретной системы при решении определенной задачи. Но все перечисленные здесь факторы можно и нужно учитывать при выборе процессора. А количественные показатели помогают сделать выбор.

Глава 4. Организация микроконтроллеров

Лекция 6. Процессорное ядро и память микроконтроллеров

В этой лекции рассказывается о структуре процессорного ядра и особенностях системы команд микроконтроллеров, функциях и организации памяти программ и данных, об использовании стека и внешней памяти микроконтроллеров.

Ключевые слова: микроконтроллер, процессорное ядро, команды, память программ, память данных, стек.

Основной особенностью современного этапа развития МПС является завершение перехода от систем, выполненных на основе нескольких больших ИС, к однокристальным МК, которые объединяют в одном кристалле все основные элементы МПС: центральный процессор (ЦП), постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ), порты ввода/выводы, таймеры.

4.1. Классификация и структура микроконтроллеров

В настоящее время выпускается целый ряд типов МК. Все эти приборы можно условно разделить на три основных класса:

• 8-разрядные МК для встраиваемых приложений;

• 16и 32-разрядные МК;

• цифровые сигнальные процессоры (DSP).

Наиболее распространенным представителем семейства МК являются 8-разрядные приборы, широко используемые в промышленности, бытовой и компьютерной технике. Они прошли в своем развитии путь от простейших приборов с относительно слаборазвитой периферией до современных многофункциональных контроллеров, обеспечивающих реализацию сложных алгоритмов управления в реальном масштабе времени. Причиной жизнеспособности 8-разрядных МК является использование их для управления реальными объектами, где применяются, в основном, алгоритмы с преобладанием логических операций, скорость обработки которых практически не зависит от разрядности процессора.

Росту популярности 8-разрядных МК способствует постоянное расширение номенклатуры изделий, выпускаемых такими известными фирмами, как Motorola, Microchip, Intel, Zilog, Atmel и многими другими.

Современные 8-разрядные МК обладают, как правило, рядом отличительных признаков. Перечислим основные из них:

• модульная организация, при которой на базе одного процессорного ядра (центрального процессора) проектируется ряд (линейка) МК, различающихся объемом и типом памяти программ, объемом памяти данных, набором периферийных модулей, частотой синхронизации;

• использование закрытой архитектуры МК, которая характеризуется отсутствием линий магистралей адреса и данных на выводах корпуса МК. Таким образом, МК представляет собой законченную систему обработки данных, наращивание возможностей которой с использованием параллельных магистралей адреса и данных не предполагается;

• использование типовых функциональных периферийных модулей (таймеры, процессоры событий, контроллеры последовательных интерфейсов, аналого-цифровые преобразователи и др.), имеющих незначительные отличия в алгоритмах работы в МК различных производителей;

• расширение числа режимов работы периферийных модулей, которые задаются в процессе инициализации регистров специальных функций МК.

При модульном принципе построения все MK одного семейства содержат процессорное ядро, одинаковое для всех МК данного семейства, и изменяемый функциональный блок, который отличает МК разных моделей. Структура модульного МК приведена на рис. 4.1.

Процессорное ядро включает в себя:

• центральный процессор;

• внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления;

• схему синхронизации МК;

• схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса) и т.д.

Изменяемый функциональный блок включает в себя модули памяти различного типа и объема, порты ввода/вывода, модули тактовых генераторов (Г), таймеры. В относительно простых МК модуль обработки прерываний входит в состав процессорного ядра. В более сложных МК он представляет собой отдельный модуль с развитыми возможностями. В состав изменяемого функционального блока могут входить и такие дополнительные модули как компараторы напряжения, аналого-цифровые преобразователи (АЦП) и другие. Каждый модуль проектируется для работы в составе МК с учетом протокола ВКМ. Данный подход позволяет создавать разнообразные по структуре МК в пределах одного семейства.

4.2. Процессорное ядро микроконтроллера

4.2.1. Структура процессорного ядра МК

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

• набор регистров для хранения промежуточных данных;

• система команд процессора;

• способы адресации операндов в пространстве памяти;

• организация процессов выборки и исполнения команды.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализует один из двух принципов построения процессоров:

• процессоры с CISC-архитектурой, реализующие так называемую полную систему команд (Complicated Instruction Set Computer);

• процессоры с RISC-архитектурой, реализующие сокращенную систему команд (Reduced Instruction Set Computer).

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК процессор с CISC-архитектурой может иметь однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. При этом система команд, как правило, не ортогональна, то есть не все команды могут использовать любой из способов адресации применительно к любому из регистров процессора. Выборка команды на исполнение осуществляется побайтно в течение нескольких циклов работы М К. Время выполнения команды может составлять от 1 до 12 циклов. К МК с CISC-архитектурой относятся МК фирмы Intel с ядром MCS-51, которые поддерживаются в настоящее время целым рядом производителей, МК семейств HC05, НС08 и НС11 фирмы Motorola и ряд других.

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК PIC16 и PIC17 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

Во-первых, оценка производительности МК по времени выполнения команд различных систем (RISC и CISC) не совсем корректна. Обычно производительность МП и МК принято оценивать числом операций пересылки «регистр-регистр», которые могут быть выполнены в течение одной секунды. В М К с CISC-процессором время выполнения операции «регистр-регистр» составляет от 1 до 3 циклов, что, казалось бы, уступает производительности МК с RISC-процессором. Однако стремление к сокращению формата команд при сохранении ортогональности системы команд RISC-процессора приводит к вынужденному ограничению числа доступных в одной команде регистров. Так, например, системой команд МК PIC16 предусмотрена возможность пересылки результата операции только в один из двух регистров — регистр-источник операнда 1 или рабочий регистр W. Таким образом, операция пересылки содержимого одного из доступных регистров в другой (не источник операнда и не рабочий) потребует использования двух команд. Такая необходимость часто возникает при пересылке содержимого одного из регистров общего назначения (РОН) в один из портов М К. В то же время, в системе команд большинства CISC-процессоров присутствуют команды пересылки содержимого РОН в один из портов ввода/вывода. То есть более сложная система команд иногда позволяет реализовать более эффективный способ выполнения операции.

Во-вторых, оценка производительности МК по скорости пересылки «регистр-регистр» не учитывает особенностей конкретного реализуемого алгоритма управления. Так, при разработке быстродействующих устройств автоматизированного управления основное внимание следует уделять времени выполнения операций умножения и деления при реализации уравнений различных передаточных функций. А при реализации пульта дистанционного управления бытовой техникой следует оценивать время выполнения логических функций, которые используются при опросе клавиатуры и генерации последовательной кодовой посылки управления. Поэтому в критических ситуациях, требующих высокого быстродействия, следует оценивать производительность на множестве тех операций, которые преимущественно используются в алгоритме управления и имеют ограничения по времени выполнения.

В-третьих, необходимо еще учитывать, что указанные в справочных данных на МК частоты синхронизации обычно соответствуют частоте подключаемого кварцевого резонатора, в то время как длительность цикла центрального процессора определяется частотой обмена по ВКМ. Соотношение этих частот индивидуально для каждого МК и должно быть принято в расчет при сравнении производительности различных моделей контроллеров.

С точки зрения организации процессов выборки и исполнения команды в современных 8-разрядных МК применяется одна из двух уже упоминавшихся архитектур МПС: фон-неймановская (принстонская) или гарвардская.

Основной особенностью фон-неймановской архитектуры является использование общей памяти для хранения программ и данных, как показано на рис. 4.2.

Основное преимущество архитектуры Фон-Неймана — упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МПС с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтому фон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

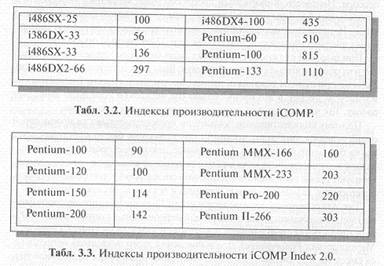

Основной особенностью гарвардской архитектуры является использование раздельных адресных пространств для хранения команд и данных, как показано на рис. 4.3.

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению.

4.2.2. Система команд процессора МК

Так же, как и в любой микропроцессорной системе, набор команд процессора МК включает в себя четыре основные группы команд:

• команды пересылки данных;

• арифметические команды;

• логические команды;

• команды переходов.

Для реализации возможности независимого управления разрядами портов (регистров) в большинстве современных МК предусмотрена также группа команд битового управления (булевый или битовый процессор). Наличие команд битового процессора позволяет существенно сократить объем кода управляющих программ и время их выполнения.

В ряде МК выделяют также группу команд управления ресурсами контроллера, используемую для настройки режимов работы портов ввода/вывода, управления таймером и т.п. В большинстве современных МК внутренние ресурсы контроллера отображаются на память данных, поэтому для целей управления ресурсами используются команды пересылки данных.

Система команд МК по сравнению с системой команд универсального МП имеет, как правило, менее развитые группы арифметических и логических команд, зато более мощные группы команд пересылки данных и управления. Эта особенность связана со сферой применения МК, требующей, прежде всего, контроля окружающей обстановки и формирования управляющих воздействий.

Схема синхронизации МК обеспечивает формирование сигналов синхронизации, необходимых для выполнения командных циклов центрального процессора, а также обмена информацией по внутренней магистрали. В зависимости от исполнения центрального процессора командный цикл может включать в себя от одного до нескольких (4 — 6) тактов синхронизации. Схема синхронизации формирует также метки времени, необходимые для работы таймеров МК. В состав схемы синхронизации входят делители частоты, которые формируют необходимые последовательности синхросигналов.

4.3. Память программ и данных МК

В МК используется три основных вида памяти. Память программ представляет собой постоянную память (ПЗУ), предназначенную для хранения программного кода (команд) и констант. Ее содержимое в ходе выполнения программы не изменяется. Память данных предназначена для хранения переменных в процессе выполнения программы и представляет собой ОЗУ. Регистры МК — этот вид памяти включает в себя внутренние регистры процессора и регистры, которые служат для управления периферийными устройствами (регистры специальных функций).

Основным свойством памяти программ является ее энергонезависимость, то есть возможность хранения программы при отсутствии питания. С точки зрения пользователей МК следует различать следующие типы энергонезависимой памяти программ:

• ПЗУ масочного типа — mask-ROM. Содержимое ячеек ПЗУ этого типа заносится при ее изготовлении с помощью масок и не может быть впоследствии заменено или допрограммировано. Поэтому МК с таким типом памяти программ следует использовать только после достаточно длительной опытной эксплуатации. Основным недостатком данной памяти является необходимость значительных затрат на создание нового комплекта фотошаблонов и их внедрение в производство. Обычно такой процесс занимает 2-3 месяца и является экономически выгодным только при выпуске десятков тысяч приборов. ПЗУ масочного типа обеспечивают высокую надежность хранения информации по причине программирования в заводских условиях с последующим контролем результата.

• ПЗУ, программируемые пользователем, с ультрафиолетовым стиранием — EPROM (Erasable Programmable ROM). ПЗУ данного типа программируются электрическими сигналами и стираются с помощью ультрафиолетового облучения. Ячейка памяти EPROM представляет собой МОП-транзистор с «плавающим» затвором, заряд на который переносится с управляющего затвора при подаче соответствующих электрических сигналов. Для стирания содержимого ячейки она облучается ультрафиолетовым светом, который сообщает заряду на плавающем затворе энергию, достаточную для преодоления потенциального барьера и стекания на подложку. Этот процесс может занимать от нескольких секунд до нескольких минут. МК с EPROM допускают многократное программирование и выпускаются в керамическом корпусе с кварцевым окошком для доступа ультрафиолетового света. Такой корпус стоит довольно дорого, что значительно увеличивает стоимость МК. Для уменьшения стоимости МК с EPROM его заключают в корпус без окошка (версия EPROM однократным программированием).

• ПЗУ, однократно программируемые пользователем, — OTPROM (One-Time Programmable ROM). Представляют собой версию EPROM, выполненную в корпусе без окошка для уменьшения стоимости МК на его основе. Сокращение стоимости при использовании таких корпусов настолько значительно, что в последнее время эти версии EPROM часто используют вместо масочных ПЗУ.

• ПЗУ, программируемые пользователем, с электрическим стиранием — EEPROM (Electrically Erasable Programmable ROM). ПЗУ данного типа можно считать новым поколением EPROM, в которых стирание ячеек памяти производится также электрическими сигналами за счет использования туннельных механизмов. Применение EEPROM позволяет стирать и программировать МК, не снимая его с платы. Таким способом можно производить отладку и модернизацию программного обеспечения. Это дает огромный выигрыш на начальных стадиях разработки микроконтроллерных систем или в процессе их изучения, когда много времени уходит на поиск причин неработоспособности системы и выполнение циклов стирания-программирования памяти программ. По цене EEPROM занимают среднее положение между OTPROM и EPROM. Технология программирования памяти EEPROM допускает побайтовое стирание и программирование ячеек. Несмотря на очевидные преимущества EEPROM, только в редких моделях МК такая память используется для хранения программ. Связано это с тем, что, во-первых, EEPROM имеют ограниченный объем памяти. Во-вторых, почти одновременно с EEPROM появились Flash-ПЗУ, которые при сходных потребительских характеристиках имеют более низкую стоимость;

• ПЗУ с электрическим стиранием типа Flash — Flash-ROM. Функционально Flash-память мало отличается от EEPROM. Основное различие состоит в способе стирания записанной информации. В памяти EEPROM стирание производится отдельно для каждой ячейки, а во Flash-памяти стирать можно только целыми блоками. Если необходимо изменить содержимое одной ячейки Flash-памяти, потребуется перепрограммировать весь блок. Упрощение декодирующих схем по сравнению с EEPROM привело к тому, что МК с Flash-памятью становятся конкурентоспособными по отношению не только к МК с однократно программируемыми ПЗУ, но и с масочными ПЗУ также.

Память данных МК выполняется, как правило, на основе статического ОЗУ. Термин «статическое» означает, что содержимое ячеек ОЗУ сохраняется при снижении тактовой частоты МК до сколь угодно малых значений (с целью снижения энергопотребления). Большинство МК имеют такой параметр, как «напряжение хранения информации»— U»~» При снижении напряжения питания ниже минимально допустимого уровня 13 „,„, но выше уровня 0 „„, работа программы МК выполняться не будет, но информация в ОЗУ сохраняется. При восстановлении напряжения питания можно будет сбросить МК и продолжить выполнение программы без потери данных. Уровень напряжения хранения составляет обычно около 1 В, что позволяет в случае необходимости перевести МК на питание от автономного источника (батареи) и сохранить в этом режиме данные ОЗУ.

Объем памяти данных МК, как правило, невелик и составляет обычно '. десятки и сотни байт. Это обстоятельство необходимо учитывать при разработке программ для МК. Так, при программировании МК константы, если возможно, не хранятся как переменные, а заносятся в ПЗУ программ. Максимально используются аппаратные возможности МК, в частности, таймеры. Прикладные программы должны ориентироваться на работу без использования больших массивов данных.

Как и все МПС, МК имеют набор регистров, которые используются для управления его ресурсами. В число этих регистров входят обычно регистры процессора (аккумулятор, регистры состояния, индексные регистры), регистры управления (регистры управления прерываниями, таймером), регистры, обеспечивающие ввод/вывод данных (регистры данных портов, регистры управления параллельным, последовательным или аналоговым вводом/выводом). Обращение к этим регистрам может производиться по-разному.

В МК с RISC-процессором все регистры (часто и аккумулятор) располагаются по явно задаваемым адресам. Это обеспечивает более высокую гибкость при работе процессора.

Одним из важных вопросов является размещение регистров в адресном пространстве МК. В некоторых МК все регистры и память данных располагаются в одном адресном пространстве. Это означает, что память данных совмещена с регистрами. Такой подход называется «отображением ресурсов МК на память».

В других МК адресное пространство устройств ввода/вывода отделено от общего пространства памяти. Отдельное пространство ввода/вывода дает некоторое преимущество процессорам с гарвардской архитектурой, обеспечивая возможность считывать команду во время обращения к регистру ввода/ вывода.

В микроконтроллерах ОЗУ данных используется также для организации вызова подпрограмм и обработки прерываний. При этих операциях содержимое программного счетчика и основных регистров (аккумулятор, регистр состояния и другие) сохраняется и затем восстанавливается при возврате к основной программе.

В фон-неймановской архитектуре единая область памяти используется, в том числе, и для реализации стека. При этом снижается производительность устройства, так как одновременный доступ к различным видам памяти невозможен. В частности, при выполнении команды вызова подпрограммы следующая команда выбирается после того, как в стек будет помещено содержимое программного счетчика.

В гарвардской архитектуре стековые операции производятся в специально выделенной для этой цели памяти. Это означает, что при выполнении программы вызова подпрограмм процессор с гарвардской архитектурой производит несколько действий одновременно.

Необходимо помнить, что МК обеих архитектур имеют ограниченную емкость памяти для хранения данных. Если в процессоре имеется отдельный стек и объем записанных в него данных превышает его емкость, то происходит циклическое изменение содержимого указателя стека, и он начинает ссылаться на ранее заполненную ячейку стека. Это означает, что после слишком большого количества вызовов подпрограмм. в стеке окажется неправильный адрес возврата. Если МК использует общую область памяти для размещения данных и стека, то существует опасность, что при переполнении стека произойдет запись в область данных либо будет сделана попытка записи загружаемых в стек данных в область ПЗУ.

4.3.5. Внешняя память

Несмотря на существующую тенденцию по переходу к закрытой архитектуре М К, в некоторых случаях возникает необходимость подключения дополнительной внешней памяти (как памяти программ, так и данных).

Если МК содержит специальные аппаратные средства для подключения внешней памяти, то эта операция производится штатным способом (как для МП).

Второй, более универсальный, способ заключается в том, чтобы использовать порты ввода/вывода для подключения внешней памяти и реализовать обращение к памяти программными средствами. Такой способ позволяет задействовать простые устройства ввода/вывода без реализации сложных шинных интерфейсов, однако приводит к снижению быстродействия системы при обращении к внешней памяти.

Лекция 7. Организация связи микроконтроллера с внешней средой и временем

В этой лекции рассказывается о структуре и организации портов ввода/вывода информации микроконтроллеров, режимах работы таймеров и процессоров событий, а также об организации обработки прерываний.

Ключевые слова: порт, ввод, вывод, таймер, счетчик, процессор событий, прерывания.

Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в много разрядные (чаще 8-разрядные) параллельные порты ввода/вывода. В памяти МК каждому порту ввода/вывода соответствует свой адрес регистра данных. Обращение к регистру данных порта ввода/ вывода производится теми же командами, что и обращение к памяти данных. Кроме того, во многих МК отдельные разряды портов могут быть опрошены или установлены командами битового процессора.

В зависимости от реализуемых функций различают следующие типы параллельных портов:

• однонаправленные порты, предназначенные только для ввода или только для вывода информации;

• двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации МК;

• порты с альтернативной функцией (мультиплексированные порты). Отдельные линии этих портов используются совместно со встроенными периферийными устройствами МК, такими как таймеры, АЦП, контроллеры последовательных интерфейсов;

• порты с программно управляемой схемотехникой входного/выходного буфера.

Порты выполняют роль устройств временного согласования функционирования МК и объекта управления, которые в общем случае работают асинхронно. Различают три типа алгоритмов обмена информацией между МК и внешним устройством через параллельные порты ввода/вывода:

• режим простого программного ввода/вывода;

• режим ввода/вывода со стробированием;

• режим ввода/вывода с полным набором сигналов подтверждения обмена.

Типичная схема двунаправленного порта ввода/вывода МК приведена на рис. 4.4.

Триггер управления разрешает вывод данных на внешний вывод. В современных МК, как правило, обеспечивается индивидуальный доступ к триггерам данных и управления, что позволяет использовать каждую линию независимо в режиме ввода или вывода.

Необходимо обратить особое внимание на то, что при вводе данных считывается значение сигнала, поступающее на внешний вывод, а не содержимое триггера данных. Если к внешнему выводу М К подключены выходы других устройств, то они могут установить свой уровень выходного сигнала, который и будет считан вместо ожидаемого значения триггера данных.

Другим распространенным вариантом схемотехнической организации порта ввода/вывода является вывод с «открытым истоком», называемый еще «квазидвунаправленным». Такая организация вывода позволяет создавать шины с объединением устройств по схеме «монтажное И».

4.5. Таймеры и процессоры событий

Большинство задач управления, которые реализуются с помощью МК, требуют исполнения их в реальном времени. Под этим понимается способность системы получить информацию о состоянии управляемого объекта, выполнить необходимые расчетные процедуры и выдать управляющие воздействия в течение интервала времени, достаточного для желаемого изменения состояния объекта.

Возлагать функции формирования управления в реальном масштабе времени только на центральный процессор неэффективно, так как это занимает ресурсы, необходимые для расчетных процедур. Поэтому в большинстве современных МК используется аппаратная поддержка работы в реальном времени с использованием таймера (таймеров).

Модули таймеров служат для приема информации о времени наступления тех или иных событий от внешних датчиков событий, а также для формирования управляющих воздействий во времени.

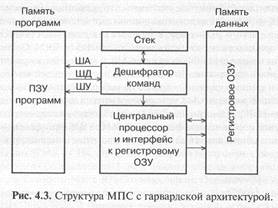

Модуль таймера 8-разрядного МК представляет собой 8-ми или 16-разрядный счетчик со схемой управления. Схемотехникой МК обычно предусматривается возможность использования таймера в режиме счетчика внешних событий, поэтому его часто называют таймером/счетчиком. Структура типичного 16 разрядного таймера/счетчика в составе МК приведена на рис. 4.5.

В памяти МК 16-разрядный счетчик отображается двумя регистрами: ТН — старший байт счетчика, TL — младший байт. Регистры доступны для чтения и для записи. Направление счета — только прямое, то есть при поступлении входных импульсов содержимое счетчика инкрементируется. В зависимости от настройки счетчик может использовать один из источников входных сигналов:

• импульсную последовательность с выхода управляемого делителя частоты fBUS;

• сигналы внешних событий, поступающие на вход TOCKI контроллера. В первом случае говорят, что счетчик работает в режиме таймера, во втором — в режиме счетчика событий. При переполнении счетчика устанавливается в «единицу» триггер переполнения TF, который генерирует запрос на прерывание, если прерывания от таймера разрешены. Пуск и останов таймера могут осуществляться только под управлением программы. Программным способом можно также установить старший и младший биты счетчика в произвольное состояние или прочитать текущий код счетчика.

Рассмотренный «классический» модуль таймера/счетчика широко применяется в различных моделях относительно простых МК. Он может использоваться для измерения временных интервалов и формирования последовательности импульсов. Основными недостатками «классического» таймера/счетчика являются:

• потери времени на выполнение команд пуска и останова таймера, приводящие к появлению ошибки при измерении временных интервалов и ограничивающие минимальную длительность измеряемых интервалов времени единицами мс;

• сложности при формировании временных интервалов (меток времени), отличных от периода полного коэффициента счета, равного (Кдел /fBUS)∙ 216;

• невозможность одновременного обслуживания (измерения или формирования импульсного сигнала) сразу нескольких каналов.

Первые их двух перечисленных недостатков были устранены в усовершенствованном модуле таймера/счетчика, используемом в МК семейства MCS-51 (Intel). Дополнительная логика счетного входа позволяет тактовым импульсам поступать на вход счетчика, если уровень сигнала на одной из линий ввода равен «1». Такое решение повышает точность измерения временных интервалов, так как пуск и останов таймера производится аппаратно. Также в усовершенствованном таймере реализован режим перезагрузки счетчика произвольным кодом в момент переполнения. Это позволяет формировать временные последовательности с периодом, отличным от периода полного коэффициента счета.

Однако эти усовершенствования не устраняют главного недостатка модуля «классического» таймера — одноканального режима работы. Совершенствование подсистемы реального времени МК ведется по следующим направлениям:

• увеличение числа модулей таймеров/счетчиков. Этот путь характерен для фирм, выпускающих М К со структурой MCS-51, а также для МК компаний Mitsubishi и Hitachi;

• модификация структуры модуля таймера/счетчика, при которой увеличение числа каналов достигается не за счет увеличения числа счетчиков, а за счет введения дополнительных аппаратных средств входного захвата (input capture — 1С) и выходного сравнения (output compare — ОС). Такой подход используется, в частности, в МК компании Motorola.

Принцип действия канала входного захвата таймера/счетчика иллюстрирует рис. 4.6.

Схема детектора события «наблюдает» за уровнем напряжения на одном из входов МК. Чаще всего это одна из линий порта ввода/вывода. При изменении уровня логического сигнала с «0» на «1» и наоборот вырабатывается строб записи, и текущее состояние счетчика таймера записывается в 16-разрядный регистр входного захвата. Описанное действие в микропроцессорной технике называют событием захвата. Предусмотрена возможность выбора типа сигнала на входе, и это воспринимается как событие:

• положительный (передний) фронт сигнала;

• отрицательный (задний) фронт сигнала;

• любое изменение логического уровня сигнала. Выбор типа события захвата устанавливается в процессе инициализации таймера и может неоднократно изменяться в ходе выполнения программы. Каждое событие захвата приводит к установке в «1» триггера входного захвата и появлению на его выходе флага (признака) входного захвата ICF. Состояние триггера входного захвата может быть считано программно, а если прерывания по событию захвата разрешены — формируется запрос на прерывание INT IС.

Использование режима входного захвата позволяет исключить ошибки измерения входного интервала времени, связанные со временем перехода к подпрограмме обработки прерывания, так как копирование текущего состояния счетчика осуществляется аппаратными, а не программными средствами. Однако время перехода на подпрограмму обработки прерывания накладывает ограничение на длительность измеряемого интервала времени, так как предполагается, что второе событие захвата произойдет позже, чем код первого события будет считая МК.

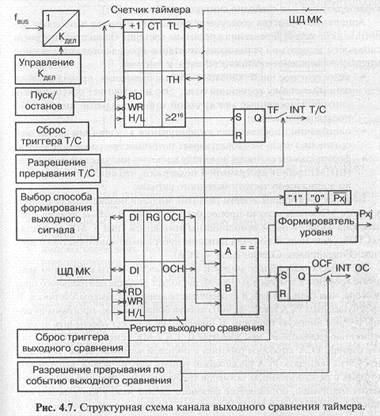

Структура аппаратных средств канала выходного сравнения представлена на рис. 4.7.

Цифровой компаратор непрерывно сравнивает текущий код счетчика таймера с кодом, который записан в 16-разрядном регистре выходного сравнения. В момент равенства кодов на одном из выходов МК (Pxj на рис. 4.7) устанавливается заданный уровень логического сигнала. Обычно предусмотрено три типа изменения сигнала на выходе Pxj в момент события выходного сравнения:

• установка высокого логического уровня;

• установка низкого логического уровня;

• инвертирование сигнала на выходе. При наступлении события сравнения устанавливаются в «1» триггер выходного сравнения и соответствующий ему признак выходного сравнения OCF. Аналогично режиму входного захвата состояние триггера выходного сравнения может быть считано программно, а если прерывания по событию сравнения разрешены — формируется запрос на прерывание INT ОС.

Режим выходного сравнения предназначен, прежде всего, для формирования временных интервалов заданной длительности. Длительность сформированного временного интервала определяется только разностью кодов, последовательно загружаемых в регистр выходного сравнения, и не зависит от программного обеспечения МК. Время, необходимое для записи нового значения кода в регистр канала сравнения, ограничивает минимальную длительность формируемого временного интервала.

Модули усовершенствованного таймера используются в составе МК в различных модификациях. При этом число каналов входного захвата и выходного сравнения в модуле может быть различным. Так, в МК семейства НС05 фирмы Motorola типовыми решениями являются. модули 1IC+10C или 2IC+2OC, а модуль таймера в составе МК только один. В

ряде модулей каналы могут быть произвольно настроены на функцию входного захвата или выходного сравнения посредством инициализации. Счетчик модуля усовершенствованного таймера может не иметь функции программного останова. В этом случае состояние счетчика нельзя синхронизировать с каким-либо моментом работы МК, и такой счетчик характеризуется как свободно считающий (free counter).

Аппаратные средства усовершенствованного таймера позволяют решить многие задачи управления в реальном времени. Однако по мере роста сложности алгоритмов управления отчетливо проявляются ограничения модулей усовершенствованного таймера, а именно:

• недостаточное число каналов захвата и сравнения, принадлежащих одному счетчику временной базы. Это не позволяет сформировать синхронизированные между собой многоканальные импульсные последовательности;

• однозначно определенная конфигурация канала (или захват или сравнение) часто не удовлетворяет потребностям решаемой задачи;

• формирование сигналов по методу широтно-импульсной модуляции (ШИМ) требует программной поддержки, что снижает максимально достижимую частоту выходного сигнала.

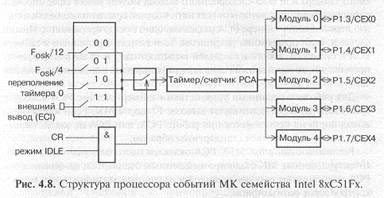

Поэтому следующим этапом развития модулей подсистемы реального времени МК стали модули процессоров событий. Впервые модули процессоров событий были использованы компанией Intel в МК семейства SxC51Fx. Этот модуль получил название программируемого счетного массива (Programmable Counter Array — PCA).

PCA обеспечивает более широкие возможности работы в реальном масштабе времени и в меньшей степени расходует ресурсы центрального процессора, чем стандартный и усовершенствованный таймеры/счетчики. К преимуществам PCA также можно отнести более простое программирование и более высокую точность. К примеру, PCA может обеспечить лучшее временное разрешение, чем таймеры 0, 1 и 2 МК семейства МС$-51, так как счетчик PCA способен работать с тактовой частотой, втрое большей, чем у этих таймеров. PCA также может решать многие задачи, выполнение которых с использованием таймеров требует дополнительных аппаратных затрат (например, определение фазового сдвига между импульсами или генерация ШИМ-сигнала). PCA состоит из 16-битного таймера-счетчика и пяти 16-битных модулей сравнения-защелки, как показано на рис. 4.8.

Таймер-счетчик PCA используется в качестве базового таймера для функционирования всех пяти модулей сравнения-защелки. Вход таймера-счетчика PCA может быть запрограммирован на счет сигналов от следующих источников:

• выход делителя на 12 тактового генератора МК;

• выход делителя на 4 тактового генератора М К;

• сигнал переполнения таймера 0;

• внешний входной сигнал на выводе ECI (Р1.2).

Любой из модулей сравнения-защелки может быть запрограммирован для работы в следующих режимах:

• защелкивания по фронту и/или спаду импульса на входе CEXi;

• программируемого таймера;

• высокоскоростного выхода;

• широтно-импульсного модулятора. Модуль 4 может быть также запрограммирован как сторожевой таймер (Watchdog Timer — WDT).

Режим защелкивания по импульсу на входе М К эквивалентен режиму входного захвата (IC) усовершенствованного таймера. Режимы программируемого таймера и высокоскоростного выхода близки по своим функциональным возможностям к режиму выходного сравнения (ОС).

В режиме ШИМ на соответствующем выводе МК формируется последовательность импульсов с периодом, равным периоду базового таймера/ счетчика РСА. Значение 8-разрядного кода, записанное в младший байт регистра-защелки соответствующего модуля задает скважность формируемого сигнала. При изменении кода от 0 до 255 скважность меняется от 100% до 0,4%.

Режим ШИМ очень прост с точки зрения программного обслуживания. Если изменения скважности не предполагается, то достаточно один раз занести соответствующий код в регистр данных модуля, проинициализировать режим ШИМ, и импульсная последовательность будет воспроизводиться с заданными параметрами без вмешательства программы.

Назначение и особенности работы сторожевого таймера будут рассмотрены далее отдельно.

При работе модуля сравнения-защелки в режиме защелки, программируемого таймера или высокоскоростного выхода модуль может сформировать сигнал прерывания. Сигналы от всех пяти модулей сравнения-защелки и сигнал переполнения таймера РСА разделяют один вектор прерывания. Иными словами, если прерывания разрешены, то и сигнал переполнения таймера РСА и сигнал от любого из модулей вызывают одну и ту же подпрограмму прерываний, которая должна сама идентифицировать источник, вызвавший ее.

Для работы с внешними устройствами таймер-счетчик РСА и модули сравнения-защелки используют выводы Р1 порта МК. Если какой-либо вывод порта не используется при работе РСА, или РСА не задействован, порт может применяться стандартным образом.

Реализованный в SxC51FX РСА оказался настолько удачным, что архитектура данных МК стала промышленным стандартом де-факто, а сам РСА многократно воспроизводился в различных модификациях микро контроллеров разных фирм.

Тенденция развития подсистемы реального времени современных МК находит свое отражение в увеличении числа каналов процессоров событий и расширении их функциональных возможностей.

Обработка прерываний в МК происходит в соответствии с общими принципами обработки прерываний в МПС. Модуль прерываний принимает запросы прерывания и организует переход к выполнению определенной прерывающей программы. Запросы прерывания могут поступать как от внешних источников, так и от источников, расположенных в различных внутренних модулях МК.

В качестве входов для приема запросов от внешних источников чаще всего используются выводы параллельных портов ввода/вывода, для которых эта функция является альтернативной. Источниками запросов внешних прерываний также могут быть любые изменения внешних сигналов на некоторых специально выделенных линиях портов ввода/вывода.

Источниками внутренних запросов прерываний могут служить следующие события:

• переполнение таймеров/счетчиков;

• сигналы от каналов входного захвата и выходного сравнения таймеров/счетчиков или от процессора событий;

• готовность памяти EEPROM;

• сигналы прерывания от дополнительных модулей МК, включая завершение передачи или приема информации по одному из последовательных портов и другие.

Любой запрос прерывания поступает на обработку, если прерывания в МК разрешены и разрешено прерывание по данному запросу. Адрес, который загружается в программный счетчик при переходе к обработке прерывания, называется «вектор прерывания». В зависимости от организации модуля прерываний конкретного МК различные источники прерываний могут иметь разные векторы или использовать некоторые из них совместно. Использование различными прерываниями одного вектора обычно не вызывает проблем при разработке программного обеспечения, так как аппаратная часть МК фиксирована, а контроллер чаще всего выполняет одну-единственную программу.

Вопрос о приоритетах при одновременном поступлении нескольких запросов на прерывание решается в различных МК по-разному. Есть МК с одноуровневой системой приоритетов (все запросы равноценны), многоуровневой системой с фиксированными приоритетами и многоуровневой программируемой системой приоритетов.

Отдельно необходимо описать аппаратные прерывания, связанные с включением питания, подачей сигнала «сброс» и переполнением сторожевого таймера. Они имеют немаскируемый характер и чаще всего разделяют один общий вектор прерывания. Это вполне логично, поскольку результатом каждого из событий является начальный сброс МК.

Лекция 8. Вспомогательные аппаратные средства микроконтроллера

В этой лекции рассказывается о режимах пониженного энергопотребления микроконтроллера, а также о структуре и организации таких вспомогательных аппаратных средств как тактовые генераторы, схемы контроля напряжения питания, сторожевые таймеры и дополнительные модули микроконтроллера.

Ключевые слова: энергопотребление, тактовый генератор, сторожевой таймер, последовательный порт, АЦП, ЦАП.

4.7. Минимизация энергопотребления в системах на основе МК

Малый уровень энергопотребления является зачастую определяющим фактором при выборе способа реализации цифровой управляющей системы. Современные МК предоставляют пользователю большие возможности в плане экономии энергопотребления и имеют, как правило, следующие основные режимы работы:

• активный режим (Run mode) — основной режим работы МК. В этом режиме МК исполняет рабочую программу, и все его ресурсы доступны. Потребляемая мощность имеет максимальное значение РRUN. Большинство современных МК выполнено по КМОП-технологии, поэтому мощность потребления в активном режиме сильно зависит от тактовой частоты;

• режим ожидания (Wait mode, Idle mode или Halt mode). В этом режиме прекращает работу центральный процессор, но продолжают функционировать периферийные модули, которые контролируют состояние объекта управления. При необходимости сигналы от периферийных модулей переводят МК в активный режим, и рабочая программа формирует необходимые управляющие воздействия. Перевод МК из режима ожидания в рабочий режим осуществляется по прерываниям от внешних источников или периферийных модулей, либо при сбросе МК. В режиме ожидания мощность потребления МК PWAIT снижается по сравнению с активным режимом в 5...10 раз;

• режим останова (Stop mode, Sleep mode или Power Down mode). В этом

режиме прекращает работу как центральный процессор, так и большинство периферийных модулей. Переход М К из состояния останова в рабочий режим возможен, как правило, только по прерываниям от внешних источников или после подачи сигнала сброса. В режиме останова мощность потребления МК РSTOP снижается по сравнению с активным режимом примерно на три порядка и составляет единицы микроватт.

Два последних режима называют режимами пониженного энергопотребления. Минимизация энергопотребления системы на МК достигается за счет оптимизации мощности потребления МК в активном режиме, а также использования режимов пониженного энергопотребления. При этом необходимо иметь в виду, что режимы ожидания и останова существенно отличаются временем перехода из режима пониженного энергопотребления в активный режим. Выход из режима ожидания обычно происходит в течение 3...5 периодов синхронизации МК, в то время как задержка выхода из режима останова, составляет несколько тысяч периодов синхронизации. Кроме снижения динамики работы системы значительное время перехода в активный режим является причиной дополнительного расхода энергии.

Мощность потребления МК в активном режиме является одной из важнейших характеристик контроллера. Она в значительной степени зависит от напряжения питания МК и частоты тактирования.

В зависимости от диапазона питающих напряжений все МК можно разделить на три основные группы:

• МК с напряжением питания 5,0 B+10%. Эти МК предназначены, как правило, для работы в составе устройств с питанием от промышленной или бытовой сети, имеют развитые функциональные возможности и высокий уровень энергопотребления.

• МК с расширенным диапазоном напряжений питания: от 2,0...3,0 В до 5,0-7,0 В. МК данной группы могут работать в составе устройств как с сетевым, так и с автономным питанием.

• МК с пониженным напряжением питания: от 1,8 до 3 В. Эти МК предназначены для работы в устройствах с автономным питанием и обеспечивают экономный расход энергии элементов питания.

Зависимость тока потребления от напряжения питания МК почти прямо пропорциональная. Поэтому снижение напряжения питания весьма существенно понижает мощность потребления МК. Необходимо, однако, иметь в виду, что для многих типов МК с понижением напряжения питания уменьшается максимально допустимая частота тактирования, то есть выигрыш в потребляемой мощности сопровождается снижением производительности системы.

Большинство современных МК выполнено по технологии КМОП, по этому мощность потребления в активном режиме РRUN практически прямо пропорциональна тактовой частоте. Поэтому, выбирая частоту тактового генератора, не следует стремиться к предельно высокому быстродействию МК в задачах, которые этого не требуют. Часто определяющим фактором оказывается разрешающая способность измерителей или формирователей временных интервалов на основе таймера или скорость передачи данных по последовательному каналу.

В большинстве современных МК используется статическая КМОП технология, поэтому они способны работать при сколь угодно низких тактовых частотах вплоть до нулевых. В справочных данных при этом указывается, что минимальная частота тактирования равна 4с (direct current). Это означает, что возможно использование МК в пошаговом режиме, например, для отладки. Мощность потребления МК при низких частотах тактирования обычно отражает значение тока потребления при fOSC = 32768 Гц (часовой кварцевый резонатор).

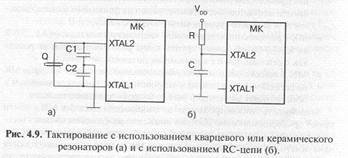

Современные МК содержат встроенные тактовые генераторы, которые требуют минимального числа внешних времязадающих элементов. На практике используются три основных способа определения тактовой частоты генератора: с помощью кварцевого резонатора, керамического резонатора и внешней RC-цепи.

Типовая схема подключения кварцевого или керамического резонатора приведена на рис. 4.9а.

Кварцевый или керамический резонатор Q подключается к выводам XTAL1 и XTAL2, которые обычно представляют собой вход и выход инвертирующего усилителя. Номиналы конденсаторов C1 и С2 определяются производителем МК для конкретной частоты резонатора. Иногда требуется включить резистор порядка нескольких мегаом между выводами XTAL1 и XTAL2 для стабильной работы генератора.

Использование кварцевого резонатора позволяет обеспечить высокую точность и стабильность тактовой частоты (разброс частот кварцевого резонатора обычно составляет менее 0,01%). Такой уровень точности требуется для обеспечения точного хода часов реального времени или организации интерфейса с другими устройствами. Основными недостатками кварцевого резонатора являются его низкая механическая прочность (высокая хрупкость) и относительно высокая стоимость.

При менее жестких требованиях к стабильности тактовой частоты возможно использование более стойких к ударной нагрузке керамических резонаторов. Многие керамические резонаторы имеют встроенные конденсаторы, что позволяет уменьшить количество внешних подключаемых элементов с трех до одного. Керамические резонаторы имеют разброс частот порядка нескольких десятых долей процента (обычно около 0,5 %).

Самым дешевым способом задания тактовой частоты МК является использование внешней RC-цепи, как показано на рис. 4.96. Внешняя RC- цепь не обеспечивает высокой точности задания тактовой частоты (разброс частот может доходить до десятков процентов). Это неприемлемо для многих приложений, где требуется точный подсчет времени. Однако имеется масса практических задач, где точность задания тактовой частоты не имеет большого значения.

Зависимость тактовой частоты МК от номиналов RC-цепи зависит от конкретной реализации внутреннего генератора и приводится в руководстве по применению контроллера.

Практически все МК допускают работу от внешнего источника тактового сигнала, который подключается ко входу XTAL1 внутреннего усилителя. При помощи внешнего тактового генератора можно задать любую тактовую частоту МК (в пределах рабочего диапазона) и обеспечить синхронную работу нескольких устройств.

Некоторые современные МК содержат встроенные RC или кольцевые генераторы, которые позволяют контроллеру работать без внешних цепей синхронизации. Работа внутреннего генератора обычно разрешается путем программирования соответствующего бита регистра конфигурации МК

В большинстве моделей МК частота времязадающего элемента (резонатора или RC-цепи) и частота тактирования fBUS жестко связаны коэффициентом деления встроенного делителя частоты. Поэтому изменение частоты программным путем не представляется возможным. Однако ряд последних семейств МК (например, НС08 фирмы Motorola) имеют в своем составе схему тактирования, основанную на принципе синтезатора частоты с контуром фазовой автоподстройки (РLL — phase loop lock). Такая схема работает как умножитель частоты и позволяет задавать тактовую частоту с помощью низкочастотного кварцевого резонатора, что снижает уровень электромагнитного излучения МК. Коэффициенты деления контура PLL могут быть изменены программным путем, что позволяет снизить тактовую частоту (и, соответственно, потребляемую мощность) в промежутки времени, когда высокое быстродействие не требуется.

В некоторых МК семейства AVR фирмы Atmel тактовая частота контроллера, задаваемая внутренней RC-цепью, также может изменяться программными средствами.

4.9. Аппаратные средства обеспечения надежной работы МК

Прикладная программа, записанная в память программ МК, должна обеспечивать его надежную работу при любых комбинациях входных сигналов. Однако в результате электромагнитных помех, колебаний напряжения питания и других внешних факторов предусмотренный разработчиком ход выполнения программы может быть нарушен. С целью обеспечения надежного запуска, контроля работы МК и восстановления работоспособности системы в отсутствие оператора все современные МК снабжаются аппаратными средствами обеспечения надежной работы. К ним относятся:

• схема формирования сигнала сброса МК;

• модуль мониторинга напряжения питания;

• сторожевой таймер.

4.9.1. Схема формирования сигнала сброса МК

При включении напряжения питания МК должен начать выполнять записанную в памяти программу работы. На этапе нарастания напряжения питания М К принудительно переводится в начальное состояние, которое называют состоянием сброса. При этом устанавливаются в исходное состояние внутренние магистрали МК, сигналы управления и регистры специальных функций. Последние определяют начальное состояние периферийных модулей МК, которое чаще всего по умолчанию неактивно.

С целью обеспечения надежного запуска от любых источников питания с различной динамикой нарастания напряжения большинство современных МК содержат встроенный детектор напряжения питания (схема Power-On-Reset — POR), который формирует сигнал сброса при нарастании напряжения питания. В частности, входящий в состав МК семейства PIC16 таймер установления питания (PWRT) начинает отсчет времени после того, как напряжение питания пересекло уровень около 1,2...1,8 В. По истечении выдержки около 72 мс считается, что напряжение достигло номинала.

Сразу после выхода из состояния сброса М К выполняет следующие действия:

• запускает генератор синхронизации МК. Для стабилизации частоты тактирования внутренними средствами формируется задержка времени;

• считывает энергонезависимые регистры конфигурации в соответствующие регистры ОЗУ (если необходимо);

• загружает в счетчик команд адрес начала рабочей программы;

• производит выборку первой программы из памяти программ и приступает к выполнению программы.

Адрес ячейки памяти, в которой хранится код первой исполняемой команды, называют вектором начального запуска или вектором сброса. В некоторых МК этот адрес однозначно определен и приведен в техническом описании. Про такие МК говорят, что они имеют фиксированный вектор сброса. В других МК вектор сброса может быть произвольно определен пользователем. На этапе программирования МК необходимый вектор начального запуска записывается в ячейки с фиксированными адресами, и при выходе МК из сброса автоматически загружается в счетчик команд. О таких МК говорят, что они имеют загружаемый вектор сброса. Загружаемый вектор сброса имеют все 8-разрядные МК фирмы Motorola, выполненные по структуре с единым адресным пространством команд и данных.

Для перевода МК в состояние сброса при установившемся напряжении питания достаточно подать сигнал высокого или низкого уровня (в соответствии со спецификацией МК) на вход сброса (RESET). Обычно для формирования сигнала сброса при включении напряжения питания и нажатии кнопки сброса используют RC-цепь. Типовые схемы формирования сигнала сброса представлены на рис. 4.10.

Кнопка Кн предназначена для «ручного» сброса МК при отладке. Диод VD препятствует попаданию на вход RESET отрицательного напряжения при выключении питания. Номиналы R и С определяют задержку времени, необходимую для завершения всех переходных процессов при сбросе (указываются в техническом описании на М К). Триггер Шмидта на входе допускает подачу сигнала сброса с ненормированной длительностью фронта. При отсутствии триггера Шмитта на входе приходится использовать специальную внешнюю схему формирователя.

В современных М Клиния RESET обычно является двунаправленной и имеет низкий активный уровень. При нажатии кнопки «сброс» или включении питания буферлинии устанавливается в режим ввода и реализует так называемый внешний сброс. МК может перейти в состояние сброса также по сигналам устройств контроля состояния, которые имеются в составе контроллера. В этом случае говорят, что МК находится в состоянии внутреннего сброса. При этом буфер линии RESET устанавливается в состояние вывода с низким логическим уровнем на выходе. Данный сигнал может быть использован для установки в начальное состояние периферийных ИС.

Порядок выхода МК из состояний внешнего и внутреннего сброса в целом одинаков.

4.9.2. Блок детектирования пониженного напряжения питания

В реальных условиях эксплуатации может сложиться такая ситуация, при которой напряжение питания МК опустится ниже минимально допустимого, но не достигнет порога отпускания схемы FOR. В этих условиях МК может «зависнуть». При восстановлении напряжения питания до номинального значения М К останется неработоспособным.

Для восстановления работоспособности системы после «просадки» напряжения питания МК необходимо снова сбросить. Для этой цели в современных МК реализован дополнительный блок детектирования пониженного напряжения питания. Такой модуль используется в МК семейства НС08 фирмы Motorola, аналогичный модуль имеется в составе семейства PIC 17 фирмы Microchip. Рассматриваемый модуль генерирует сигнал внутреннего сброса при снижении напряжения питания до уровня чуть ниже минимально допустимого. Уровень срабатывания блока детектирования пониженного напряжения питания значительно превышает напряжение сохранения данных в ОЗУ МК. Событие сброса по сигналу блока пониженного напряжения питания отмечается специальным битом в одном из регистров МК. Следовательно, программно анализируя этот бит после сброса МК, можно установить, что данные целы, и продолжить выполнение программы.

Если, несмотря на все принятые меры, МК все же «завис>, то на случай выхода из этого состояния все современные контроллеры имеют встроенный модуль сторожевого таймера. Принцип действия сторожевого таймера показан на рис. 4.11.

Основу сторожевого таймера составляет много разрядный счетчик. При сбросе МК счетчик обнуляется. После перехода МК в активный режим работы значение счетчика начинает увеличиваться независимо от выполняемой программы. При достижении счетчиком максимального кода генерируется сигнал внутреннего сброса, и МК начинает выполнять рабочую программу сначала.

Для исключения сброса по переполнению сторожевого таймера рабочая программа МК должна периодически сбрасывать счетчик. Сброс счетчика сторожевого таймера осуществляется путем исполнения специальной команды (например, CLRWDT) или посредством записи некоторого указанного кода в один из регистров специальных функций. Тогда при нормальном, предусмотренном разработчиком, порядке исполнения рабочей программы переполнения счетчика сторожевого таймера не происходит, и он не оказывает влияния на работу МК. Однако, если исполнение рабочей программы было нарушено, например, вследствие «зависания», то велика вероятность того, что счетчик не будет сброшен вовремя. Тогда произойдет сброс по переполнению сторожевого таймера, и нормальный ход выполнения рабочей программы будет восстановлен.

Модули сторожевых таймеров конкретных МК могут иметь различные особенности:

• в ряде М К векторы внешнего сброса и сброса по переполнению сторожевого таймера совпадают. Это не позволяет выявить причину сброса программным путем и затрудняет написание рабочей программы. Более высокоуровневые МК имеют либо различные векторы сброса, либо отмечают событие сброса по переполнению сторожевого таймера установкой специального бита в одном из регистров специальных функций;

• в некоторых МК при переходе в один из режимов пониженного энергопотребления, когда рабочая программа не выполняется, автоматически приостанавливается работа сторожевого таймера. В других МК сторожевой таймер имеет независимый тактовый генератор, который продолжает функционировать и в режиме ожидания. В этом случае необходимо периодически выводить МК из состояния ожидания для сброса сторожевого таймера. В Р1С-контроллерах фирмы Microchip выработка таких сбросов может быть запрещена путем записи нуля в специальный бит конфигурации WDTE.

Использование сторожевого таймера существенно повышает способность к самовосстановлению системы на основе МК.

4.10. Дополнительные модули МК

Описанные выше модули составляют так называемый базовый комплект МК и входят в состав любого современного контроллера. Очевидна необходимость включения в состав МК дополнительных модулей, состав и возможности которых определяются конкретной решаемой задачей. Среди таких дополнительных модулей следует, прежде всего, отметить:

• модули последовательного ввода/вывода данных;

• модули аналогового ввода/вывода.

4. 10.1. Модули последовательного ввода/вывода

Наличие в составе 8-разрядного МК модуля контроллера последовательного ввода/вывода стало в последнее время обычным явлением. Задачи, которые решаются средствами модуля контроллера последовательного ввода/вывода, можно разделить на три основные группы:

• связь встроенной микроконтроллерной системы с системой управления верхнего уровня, например, с персональным компьютером. Чаще всего для этой цели используются интерфейсы RS-232С и RS- 485;

• связь с внешними по отношению к МК периферийными ИС, а также с датчиками физических величин с последовательным выходом. Для этих целей используются интерфейсы I2С, SPI, а также нестандартные протоколы обмена;

• интерфейс связи с локальной сетью в мультимикро контроллерных системах. В системах с числом МК до пяти обычно используются сети на основе интерфейсов I2С, RS-232С и RS-485 с собственными сетевыми протоколами высокого уровня. В более сложных системах все более популярным становится протокол CAN.

С точки зрения организации обмена информацией упомянутые типы интерфейсов последовательной связи отличаются режимом передачи данных (синхронный или асинхронный), форматом кадра (число бит в посылке при передаче байта полезной информации) и временными диаграммами сигналов на линиях (уровни сигналов и положение фронтов при переключениях).

Число линий, по которым происходит передача в последовательном коде, обычно равно двум (I'С, RS-232С, RS-485) или трем (SPI, некоторые нестандартные протоколы). Данное обстоятельство позволяет спроектировать модули контроллеров последовательного обмена таким образом, чтобы с их помощью на аппаратном уровне можно было реализовать несколько типов последовательных интерфейсов. При этом режим передачи (синхронный или асинхронный) и формат кадра поддерживаются на уровне логических сигналов, а реальные физические уровни сигналов для каждого интерфейса получают с помощью специальных ИС, которые называют приемопередатчиками, конверторами, трансиверами.

Среди различных типов встроенных контроллеров последовательного обмена, которые входят в состав тех или иных 8-разрядных МК, сложился стандарт «де-факто» — модуль UART (Universal Asynchronous Receiver and Transmitter). UART — это универсальный асинхронный приемопередатчик. Однако большинство модулей UART, кроме асинхронного режима обмена, способны также реализовать режим синхронной передачи данных.

Не все производители МК используют термин UART для обозначения типа модуля контроллера последовательного обмена. Так, в МК фирмы Motorola модуль асинхронной приемопередачи, который поддерживает те же режимы асинхронного обмена, что и UART, принято называть SCI (Serial Communication Interface). Следует отметить, что модуль типа SCI обычно реализует только режим асинхронного обмена, то есть его функциональные возможности уже по сравнению с модулями типа UART. Однако бывают и исключения: под тем же именем SCI в МК МС68НС705В16 скрывается модуль синхронно-асинхронной передачи данных.

Модули типа UART в асинхронном режиме работы позволяют реализовать протокол обмена для интерфейсов RS-232С, RS-422А, RS-485, в синхронном режиме — нестандартные синхронные протоколы обмена, и в некоторых моделях — SPI. В МК фирмы Motorola традиционно предусмотрены два модуля последовательного обмена: модуль SCI с возможностью реализации только протоколов асинхронной приемопередачи для интерфейсов RS-232С, RS-422А, RS-485 и модуль контроллера синхронного интерфейса в стандарте SPI.

Протоколы интерфейсов локальных сетей на основе МК (!'С и CAN) отличает более сложная логика работы. Поэтому контроллеры CAN интерфейса всегда выполняются в виде самостоятельного модуля. Интерфейс I'С с возможностью работы как в ведущем, так и ведомом режиме, также обычно поддерживается специальным модулем (модуль последовательного порта в МК 89C52 фирмы Philips). Но если реализуется только ведомый режим I2С, то в МК Р1С16 фирмы Microchip он успешно сочетается с S PI: настройка одного и того же модуля на один из протоколов осуществляется путем инициализации.

В последнее время появилось большое количество МК со встроенными модулями контроллеров CAN и модулями универсального последовательного интерфейса периферийных устройств USB (Universal Serial Bus). Каждый из этих интерфейсов имеет достаточно сложные протоколы обмена, для ознакомления с которыми следует обращаться к специальной литературе.