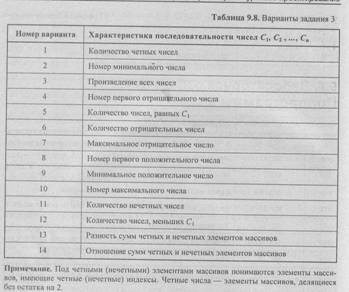

1. Написать программу определения заданной характеристики последовательности чисел C1, C2, ..., Сn. Варианты заданий приведены в табл. 9.8.

2. Записать программу в мнемокодах, введя ее в поле окна Текст программы.

3. Сохранить набранную программу в виде текстового файла и произвести ассемблирование мнемокодов.

4. Загрузить в ОЗУ необходимые константы и исходные данные.

5. Отладить программу.

1. Формулировка варианта задания.

2. Граф-схема алгоритма решения задачи.

3. Распределение памяти (размещение в ОЗУ переменных, программы и не-

обходимых констант).

4. Программа.

5. Значения исходных данных и результата выполнения программы.

1. Как организовать цикл в программе?

2. Что такое параметр цикла?

3. Как поведет себя программа, приведенная в табл. 9.7, если в ней будет отсутствовать команда WR 31 по адресу 014?

4. Как поведет себя программа, приведенная в табл. 9.7, если метка MI будет поставлена по адресу 005? 007?

9.4. Лабораторная работа № 4. Подпрограммы и стек

В программировании часто встречаются ситуации, когда одинаковые действия необходимо выполнять многократно в разных частях программы (например, вычисление функции sin x). При этом с целью экономии памяти не следует многократно повторять одну и ту же последовательность команд — достаточно один раз написать так называемую

подпрограмму (в терминах языков высокого уровня — процедуру) и обеспечить правильный вызов этой подпрограммы и возврат в точку вызова по завершению подпрограммы.

Для вызова подпрограммы необходимо указать ее начальный адрес в памяти и передать (если необходимо) параметры — те исходные данные, с которыми будут выполняться предусмотренные в подпрограмме действия. Адрес под программы указывается в команде вызова CALL, а параметры могут передаваться через определенные ячейки памяти, регистры или стек.

Возврат в точку вызова обеспечивается сохранением адреса текущей команды (содержимого регистра PC) при вызове и использованием в конце подпрограммы команды возврата RET, которая возвращает сохраненное значение адреса возврата в РС.

Для реализации механизма вложенных подпрограмм (возможность вызова подпрограммы из другой подпрограммы и т. д.) адреса возврата целесообразно сохранять в стеке. Стек ("магазин") — особым образом организованная безадресная память, доступ к которой осуществляется через единственную ячейку, называемую верхушкой стека. При записи слово помещается в верхушку стека, предварительно все находящиеся в нем слова смещаются вниз на одну позицию; при чтении извлекается содержимое верхушки стека (оно при этом из стека исчезает), а все оставшиеся слова смещаются вверх на одну позицию. Такой механизм напоминает действие магазина стрелкового оружия (отсюда и второе название). В программировании называют такую дисциплину обслуживания LIFO (Last In First Out, последним пришел — первым вышел) в отличие от дисциплины типа очередь — FIFO (First In First Out, первым пришел — первым вышел).

В обычных ОЗУ нет возможности перемещать слова между ячейками, поэтому при организации стека перемещается не массив слов относительно не под важной верхушки, а верхушка относительно неподвижного массива. Под стек отводится некоторая область ОЗУ, причем адрес верхушки хранится в специальном регистре процессора — указателе стека SP.

В стек можно поместить содержимое регистра общего назначения по команде PUSH или извлечь содержимое верхушки в регистр общего назначения по команде РOP. Кроме того, по команде RET вызова подпрограммы CALL значение программного счетчика PC (адрес следующей команды) помещается в верхушку стека, а по команде ют содержимое верхушки стека извлекается в PC. При каждом обращении в стек указатель SP автоматически модифицируется

В большинстве ЭВМ стек "растет" в сторону меньших адресов, поэтому перед каждой записью содержимое SP уменьшается на 1, а после каждого извлечения содержимое SP увеличивается на 1. Таким образом, SP всегда указывает на верхушку стека.

Цель настоящей лабораторной работы — изучение организации программ с использованием подпрограмм. Кроме того, в процессе организации циклов мы будем использовать новые возможности системы команд модели ЭВМ, которые позволяют работать с новым классом памяти — сверхоперативной (регистры общего назначения — POH). В реальных ЭВМ доступ в POH занимает значительно меньшее время, чем в ОЗУ; кроме того, команды обращения с регистрами короче команд обращения к памяти. Поэтому в POH размещаются наиболее часто используемые в программе данные, промежуточные результаты, счетчики циклов, косвенные адреса и т. п.

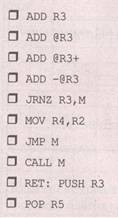

В системе команд учебной ЭВМ для работы с POH используются специальные команды, мнемоники которых совпадают с мнемониками соответствующих команд для работы с ОЗУ, но в адресной части содержат символы регистров RO — R9.

Кроме обычных способов адресации (прямой и косвенной) в регистровых командах используются два новых — постинкрементная и пред декрементная (см. табл. 8.5). Кроме того, к регистровым относится команда организации цикла JRNZ R,М. По этой команде содержимое указанного в команде регистра уменьшается на 1, и если в результате вычитания содержимого регистра не равно 0, то управление передается на метку м. Эту команду следует ставить в конце тела цикла, метку м — в первой команде тела цикла, а в регистр R помещать число повторений цикла.

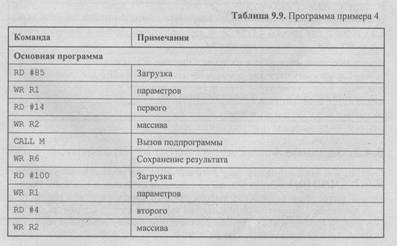

Даны три массива чисел. Требуется вычислить среднее арифметическое их максимальных элементов. Каждый массив задается двумя параметрами адресом первого элемента и длиной.

Очевидно, в программе трижды необходимо выполнить поиск максимального элемента массива, поэтому следует написать соответствующую подпрограмму.

Параметры в подпрограмму будем передавать через регистры: Rl — начальный адрес массива, R2 — длина массива.

Рассмотрим конкретную реализацию этой задачи. Пусть первый массив начинается с адреса 085 и имеет длину 14 элементов, второй — 100 и 4, третий — 110 и 9. Программа будет состоять из основной части и подпрограммы. Основная программа задает параметры подпрограмме, вызывает ее и сохраняет результаты работы подпрограммы в рабочих ячейках. Затем осуществляет вычисление среднего арифметического и выводит результат на устройство вывода. В качестве рабочих ячеек используются регистры общего назначения R6 и R7 — для хранения максимальных элементов массивов. Подпрограмма получает параметры через регистры Rl (начальный адрес массива) и R2 (длина массива). Эти регистры используются подпрограммой в качестве регистра текущего адреса и счетчика цикла соответственно. Кроме того, R3 используется для хранения текущего максимума, а R4 — для временного хранения текущего элемента. Подпрограмма возвращает результат через аккумулятор. В табл. 9.9 приведен текст основной программы и под программы. Обратите внимание, цикл в подпрограмме организован с помощью команды жни, а модификация текущего адреса — средствами постинкрементной адресации.

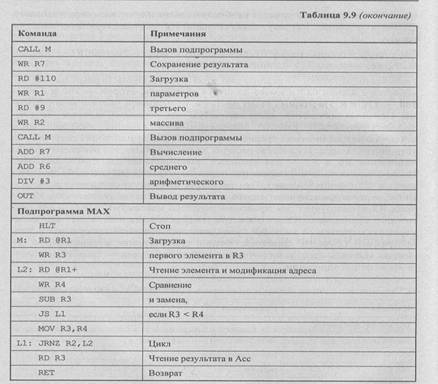

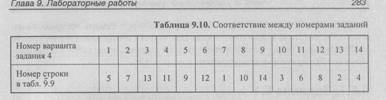

Составить и отладить программу учебной ЭВМ для решения следующей задачи. Три массива в памяти заданы начальными адресами и длинами. Вычислить и вывести на устройство вывода среднее арифметическое параметров этих массивов. Параметры определяются заданием к предыдущей лабораторной работе (см. табл. 9.8), причем соответствие между номерами вариантов заданий 3 и 4 устанавливается по табл. 9.10.

1. Формулировка варианта задания.

2. Граф-схема алгоритма основной программы.

3. Граф-схема алгоритма подпрограммы.

4. Распределение памяти (размещение в ОЗУ переменных, программы и необходимых констант).

5. Тексты программы и подпрограммы.

6. Значения исходных данных и результата выполнения программы.

9.4.4. Контрольные вопросы

1. Как работает команда MOV R3, R7?

2. Какие действия выполняет процессор при реализации команды CALL?

3. Как поведет себя программа примера 4, если в ней вместо команд CALL M использовать команды JMP M?

4. После начальной установки процессора (сигнал Сброс) указатель стека SP устанавливается в 000. По какому адресу будет производиться запись в стек первый раз, если не загружать SP командой WRSP?

5. Как, используя механизмы постинкрементной и преддекрементной адресации, организовать дополнительный стек в произвольной области памяти, не связанный с SP?

9.5. Лабораторная работа № 5. Командный цикл процессора

Реализация программы в ЭВМ сводится к последовательному выполнению команд. Каждая команда, в свою очередь, выполняется как последовательность микрокоманд, реализующих элементарные действия над операционными элементами процессора.

В программной модели учебной ЭВМ предусмотрен Режим микрокоманд, в котором действие командного цикла реализуется и отображается на уровне микрокоманд. Список микрокоманд текущей команды выводится в специальном окне Микрокомандный уровень (см. рис. 8.8).

9.5.1. Задание 5 1

Выполнить снова последовательность команд по варианту задания 1 (см. табл. 9.3), но в режиме Шаг. Зарегистрировать изменения состояния процессора и памяти в форме табл. 9.11, в которой приведены состояния ЭВМ при выполнении примера 1 (фрагмент).

Записать последовательность микрокоманд для следующих команд модели учебной ЭВМ:

1. Какие микрокоманды связаны с изменением состояния аккумулятора?

2. Какие действия выполняются в модели по микрокоманде MRd? RWr?

3. Попробуйте составить микропрограмму (последовательность микрокоманд, реализующих команду) для несуществующей команды "умножение модулей чисел".

4. Что изменится в работе процессора, если в каждой микропрограмме микрокоманду увеличения программного счетчика РС:= PC + 1 переместить в самый конец микропрограммы?

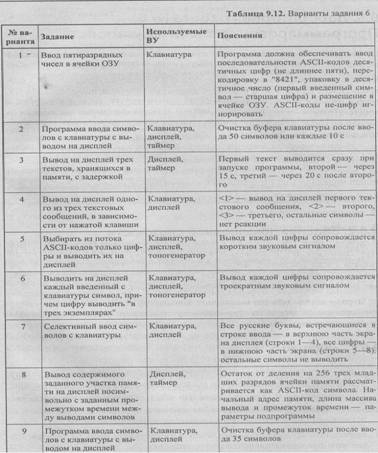

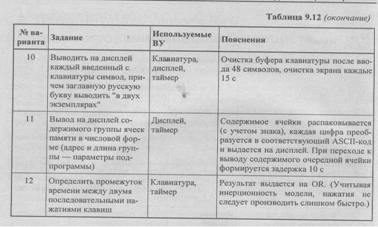

9.6. Лабораторная работа № 6. Программирование внешних устройств

Целью этой лабораторной работы является изучение способов организации. взаимодействия процессора и внешних устройств (ВУ) в составе ЭВМ.

Выше отмечалось, что связь процессора и ВУ может осуществляться в синхронном или асинхронном режиме. Синхронный режим используется для ВУ, всегда готовых к обмену. В нашей модели такими ВУ являются дисплей и тоногенератор — процессор может обращаться к этим ВУ, не анализируя их состояние (правда дисплей блокирует прием данных после ввода 128 символов, формируя флаг ошибки).

Асинхронный обмен предполагает анализ процессором состояния ВУ, которое

определяет готовность ВУ выдать или принять данные или факт осуществления некоторого события, контролируемого системой. К таким устройствам в нашей модели можно отнести клавиатуру и блок таймеров.

Анализ состояния ВУ может осуществляться процессором двумя способами:

• в программно-управляемом режиме;

• в режиме прерывания.

В первом случае предполагается программное обращение процессора к регистру состояния ВУ с последующим анализом значения соответствующего разряда слова состояния. Такое обращение следует предусмотреть в программе с некоторой периодичностью, независимо от фактического наступления контролируемого события (например, нажатие клавиши).

Во втором случае при возникновении контролируемого события ВУ формирует процессору запрос на прерывание программы, по которому процессор и осуществляет связь с ВУ.

Свой вариант задания (табл. 9.12) требуется выполнить двумя способами сначала в режиме программного контроля, далее модифицировать программу таким образом, чтобы события обрабатывались в режиме прерывания программы. Поскольку "фоновая" (основная) задача для этого случая в заданиях отсутствует, роль ее может сыграть "пустой цикл": k

M; NOP

NOP

JMP M

9.6.2. Задания повышенной сложности

1. Разработать программу-тест на скорость ввода символов с клавиатуры. По звуковому сигналу включается клавиатура и таймер на Т секунд. Можно начинать ввод символов, причем каждый символ отображается на дисплее, ведется подсчет количества введенных символов (после каждых 50 дается команда на очистку буфера клавиатуры, после 128 — очищается дисплей). Переполнение таймера выключает клавиатуру и включает сигнал завершения ввода (можно тон этого сигнала сопоставить с количеством введенных символов). Параметр Т вводится из IR. Результат S — средняя скорость ввода (символ/с) выдается на OR. Учитывая, что модель учебной ЭВМ оперирует только целыми числами, можно выдавать результат в формате S х 60 символов/мин.

2. Разработать программу тест на степень запоминания текста. Три различных вариантах текста выводятся последовательно на дисплей на Т, секунд с промежутками Т1 секунд. Далее эти тексты (то, что запомнилось) вводятся с клавиатуры (в режиме ввода строки) и программно сравниваются с исходными текстами. Выдается количество (процент) ошибок.

3. Разработать программу калькулятор. Осуществлять ввод из буфера клавиатуры последовательности цифр, упаковку (см. задание 1 в табл. 9.12),

Разделители — знаки бинарных арифметических операций и =. Результат переводится в ASCII-коды и выводится на дисплей.

9.6.3. Порядок выполнения работы

1. Запустить программную модель учебной ЭВМ и подключить к ней определенные в задании внешние устройства (меню Внешние устройства - Менеджер ВУ).

Написать и отладить программу, предусмотренную заданием, с использованием программного анализа флагов готовности ВУ. Продемонстрировать работающую программу преподавателю.

Изменить отлаженную в п. 2 программу таким образом, чтобы процессор

реагировал на готовность ВУ с помощью подсистемы прерывания. Продемонстрировать работу измененной программы преподавателю.

1. Текст программы с программным анализом флагов готовности ВУ.

2. Текст программы с обработчиком прерывания.

1. При каких условиях устанавливается и сбрасывается флаг готовности клавиатуры Rd?

2. Возможно ли в блоке таймеров организовать работу всех трех таймеров с разной тактовой частотой?

3. Как при получении запроса на прерывание от блока таймеров определить номер таймера, достигшего состояния 99 999 (00 000)?

4. Какой текст окажется на экране дисплея, если после нажатия в окне обозревателя дисплея кнопки Очистить и загрузки по адресу CR (11) константы #10 вывести по адресу DR (10) последовательно пять ASCII-кодов русских букв А, Б, В, Г, Д?

5. В какой области памяти модели ЭВМ могут располагаться программы— обработчики прерываний?

6. Какие изменения в работе отлаженной вами второй программы произойдут, если завершить обработчик прерываний командой акт, а не такт?

9.7. Лабораторная работа № 7. Принципы работы кэш-памяти

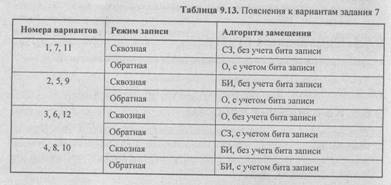

В разд. 8.8 данной книги описаны некоторые алгоритмы замещения строк, кэш-памяти. Цель настоящей лабораторной работы — проверить работу различных алгоритмов замещения при различных режимах записи.

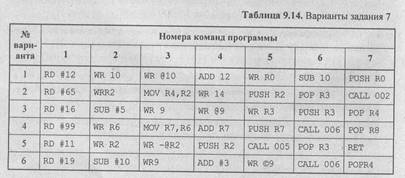

В качестве задания предлагается некоторая короткая "программа" (табл. 9.14), которую необходимо выполнить с подключенной кэш-памятью (размером 4 и 8 ячеек) в шаговом режиме для следующих двух вариантов алгоритмов замещения (табл. 9.13).

Не следует рассматривать заданную последовательность команд как фрагмент программы. Некоторые конструкции, например, последовательность команд PUSH R6, RET в общем случае не возвращает программу в точку вызова подпрограммы. Такие группы команд введены в задание для того, чтобы обратить внимание студентов на особенности функционирования стека.

9.7.2. Порядок выполнения работы

1. Ввести в модель учебной ЭВМ текст своего варианта программы (см. табл. 9.14), ассемблировать его и сохранить на диске в виде txt-файла.

2. Установить параметры кэш-памяти размером 4 ячейки, выбрать режим записи и алгоритм замещения в соответствии с первой строкой своего варианта из табл. 9.13.

3. В шаговом режиме выполнить программу, фиксируя после каждого шага состояние кэш-памяти.

4. Для одной из команд записи (WR) перейти в режим Такт и отметить, в каких микрокомандах происходит изменение кэш-памяти.

5. Для кэш-памяти размером 8 ячеек установить параметры в соответствии со второй строкой своего варианта из табл. 9.13 и выполнить программу в шаговом режиме еще раз, фиксируя последовательность номеров замещаемых ячеек кэш-памяти.

1. Вариант задания — текст программы и режимы кэш-памяти.

2. Последовательность состояний кэш-памяти размером 4 ячейки при однократном выполнении программы (команды 1 — 7).

3. Последовательность микрокоманд при выполнении команды WR с отметкой тех микрокоманд, в которых возможна модификация кэш-памяти.

4. Для варианта кэш-памяти размером 8 ячеек — последовательность номеров замещаемых ячеек кэш-памяти для второго варианта параметров кэш- памяти при двукратном выполнении программы (команды 1 — 7).

1. В чем смысл включения кэш-памяти в состав ЭВМ?

2. Как работает кэш-память в режиме обратной записи? Сквозной записи?

3. Как зависит эффективность работы ЭВМ от размера кэш-памяти?

4. В какую ячейку кэш-памяти будет помещаться очередное слово, если свободные ячейки отсутствуют?

5. Какие алгоритмы замещения ячеек кэш-памяти вам известны?

Алгоритмы замещения строк кэш-памяти

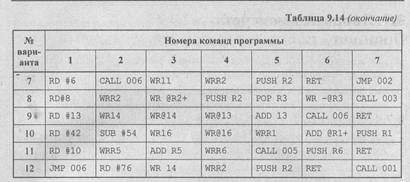

Цель работы — изучение влияния параметров кэш-памяти и выбранного алгоритма замещения. на эффективность работы системы. Эффективность в данном случае оценивается числом кэш-попаданий по отношению к общему числу обращений к памяти. Учитывая разницу в алгоритмах в режимах сквозной и обратной записи, эффективность использования кэш-памяти вычисляется выражениям (8.2) и (8.3) соответственно для сквозной и обратной записи.

Очевидно, эффективность работы системы с кэш-памятью будет зависеть не только от параметров кэш-памяти и выбранного алгоритма замещения, но и от класса решаемой задачи. Так, линейные программы должны хорошо работать с алгоритмами замещения типа очередь, а программы с большим числом условных переходов, зависящих от случайных входных данных, могут давать неплохие результаты с алгоритмами случайного замещения. Можно предположить, что программы, имеющие большое число повторяющихся участков (часто вызываемых подпрограмм и/или циклов) при прочих равных условиях обеспечат более высокую эффективность применения кэш-памяти, чем линейные программы. И, разумеется, на эффективность напрямую должен влиять размер кэш-памяти.

Для проверки высказанных выше предположений выполняется настоящая лабораторная работа.

В данной лабораторной работе все варианты задания одинаковы: исследовать эффективность работы кэш-памяти при выполнении двух разнотипных программ, написанных и отлаженных вами при выполнении лабораторных работ № 2 и 4.

9.8.2. Порядок выполнения работы

1. Загрузить в модель учебной ЭВМ отлаженную программу из лабораторной работы № 2.

2. В меню Работа установить режим Кэш-память.

3. В меню Вид выбрать команду Кэш-память, открыв тем самым окно Кэш- память, в нем нажать первую слева кнопку на панели инструментов, открыв диалоговое окно Параметры кэш-памяти, и установить следующие параметры кэш-памяти: размер — 4, режим записи — сквозная, алгоритм замещения — случайное, без учета бита записи (W).

4. Запустить программу в автоматическом режиме; по окончании работы просмотреть результаты работы кэш-памяти в окне Кэш-память, вычислить значение коэффициента эффективности К и записать в ячейку табл. 9.15, помеченную звездочкой.

5. Выключить кэш-память модели (Работа ) Кэш-память) и изменить один из ее параметров — установить флаг с учетом бита записи (в окне Параметры кэш-памяти).

6. Повторить п. 4, поместив значение полученного коэффициента эффективности в следующую справа ячейку табл. 9.15.

7. Последовательно меняя параметры кэш-памяти, повторить п. 3 — 5, заполняя все ячейки табл. 9.15.

Совет_____________________________________________________

При очередном запуске программы не забывайте устанавливать процессор модели в начальное состояние, нажимая кнопку R в окне Процессор!

8. Повторить все действия, описанные в кп. 1 — 7 для программы из лабораторной работы № 4, заполняя вторую таблицу по форме табл. 9.15.

1. Две таблицы по форме табл. 9.15 с результатами моделирования программ из лабораторных работ № 2 и 4 при разных режимах работы кэш-памяти.

2. Выводы, объясняющие полученные результаты.

1. Как работает алгоритм замещения очередь при установленном флажки" С учетом бита записи в диалоговом окне Параметры кэш-памяти?

2. Какой алгоритм замещения будет наиболее эффективным в случае применения кэш-памяти большого объема (в кэш-память целиком помещается программа)?

3. Как скажется на эффективности алгоритмов замещения учет значения бита записи W при работе кэш-памяти в режиме обратной записи? Сквозной записи?

4. Для каких целей в структуру ячейки кэш-памяти включен бит использования. Как устанавливается и сбрасывается этот бит?

Курсовая работа

10.1. Цель и содержание работы

Целью курсовой работы является:

• обобщение, закрепление и углубление знаний по дисциплинам, связанным с проектированием средств ВТ;

• формирование навыков разработки и оформления текстовой и графической технической документации;

• развитие навыков устных сообщений по содержанию работы. Содержанием курсовой работы является разработка арифметико-логического устройства (АЛУ), реализующего заданный набор операций с учетом ограничений на код выполнения операций и способ построения управляющего автомата.

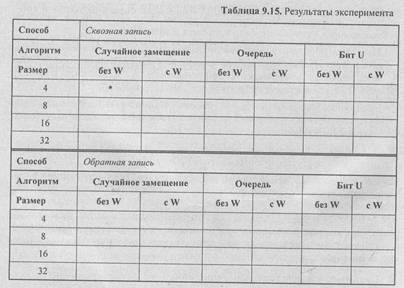

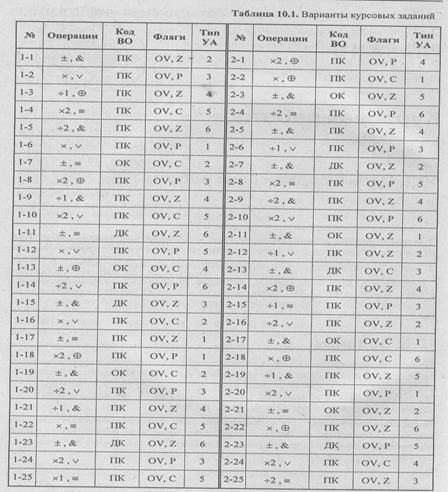

Задания на курсовую работу включают в себя некоторый набор исходных данных и ограничений для проектирования АЛУ. Все варианты задания сведены в табл. 10.1. Строка таблицы представляет один вариант задания, причем номер варианта определяется номером группы (1 — 2) и порядковым номером студента по списку группы (1 — 25).

Разрабатываемое АЛУ должно выполнять одну арифметическую и одну поразрядную бинарную логическую операцию, причем на способ выполнения арифметической операции заданием накладываются некоторые ограничения. Варианты операций обозначаются в табл.

± — алгебраическое сложение/вычитание;

х — умножение обыкновенное;

х2 — умножение ускоренное (с анализом двух разрядов множителя);

![]() 1 —

деление с восстановлением остатка;

1 —

деление с восстановлением остатка;

![]() 2 — деление

без восстановления остатка;

2 — деление

без восстановления остатка;

V — дизъюнкция;

&— конъюнкция;

![]() неравнозначность;

неравнозначность;

≡ — эквивалентность.

Для всех вариантов заданий исходные данные (операнды) поступают в формате 16-разрядных двоичных чисел с фиксированной запятой, представленных в прямом коде [а0 а1 ...а15], [b0 b1 ...b15]d, причем нулевой разряд является знаковым и запятая фиксирована после знакового разряда. Таким образом, в арифметических операциях участвуют правильные дроби со своими знаками (в логических операциях, естественно, положение запятой и знак игнорируются, операции выполняются над 16-разрядными двоичными векторами). Соответственно, результат операции должен быть представлен в той же форе: (с0 с1 ...с15]d.

В задании вводится ограничение на код выполнения операции (столбец Код ВО в табл. 10.1). Если код ВО отличается от прямого — обратный (ОК) или дополнительный (ДК), то при выполнении арифметической операции следует перевести операнды в заданный код, выполнить в нем операцию, а результат вновь перевести в прямой код. Логические операции, естественно, выполняются без всякого преобразования.

Результатом выполнения операции в АЛУ должно быть не только значение суммы (произведения, конъюнкции и др.) но и признаки результата (флаги). Каждый вариант задания предполагает формирования двух различных флагов (заданных в столбце Флаги табл. 10.1) из приведенного ниже множества.

Z — признак нулевого результата;

Р — признак четности числа единиц в результате;

С — признак переноса (заема) из старшего разряда;

OV — признак арифметического переполнения.

В столбце Тип УА задан номер типа управляющего автомата, который необходимо использовать при проектировании заданного АЛУ. Список типов УА приведен ниже.

1 — "жесткая логика", автомат Мура;

2 — "жесткая логика", автомат Мили;

3 — программируемая логика, единый формат микрокоманды, принудительная адресация;

4 — программируемая логика, единый формат микрокоманды, естественная адресация;

5 — программируемая логика, различные форматы для операционными микрокоманд и микрокоманд перехода, естественная адресация;

6 — программируемая логика, различные форматы для операционных микрокоманд и микрокоманд перехода, принудительная адресация.

В задании не определены ограничения на базис логических, операционных, элементов и элементов памяти. Поэтому при разработке структурных и функциональных схем можно использовать любые стандартные логические и операционные элементы.

В главе 4 настоящего пособия подробно рассматривается процесс проектирования цифрового устройства. При проектировании его удобно представить в виде композиции операционного и управляющего автоматов (см. разд. 4.2). Тогда процесс проектирования устройства сводится к процедурам последовательного проектирования операционного и управляющего автоматов. Здесь можно выделить следующие этапы:

1. Разработка алгоритмов выполняемых операций. На этом этапе следует определить список входных, выходных и внутренних переменных и выбрать коды выполняемых операций. Поскольку все задания предполагают реализацию одной/двух арифметических и одной логической операций, целесообразно представить все алгоритмы в форме объединенной ГСА.

2. Разработка структуры операционного автомата — определение состава элементов и связей между ними. Разработка структуры нестандартных элементов. Результатом работы. на этом этапе должна стать структурная (функциональная) схема операционного автомата, а также функциональные схемы всех использованных в ОА нестандартных элементов.

3. Определение списка микроопераций и логических условий. Необходимо сопоставить каждому оператору из ГСА микрокоманду или группу микро команд, обеспечивающих реализацию этого оператора на разработанной ранее структуре. На этом этапе возможно расширение набора элементов и/или связей структуры, если без такого расширения не удается реализовать все операторы ГСА. Кроме того, необходимо определить, где будут формироваться значения логических переменных, которые анализируются в логических вершинах ГСА и при необходимости предусмотреть специальные элементы структуры для формирования этих значений. Результат работы на этом этапе — списки микроопераций и логических условий ОА. Разработка микропрограммы выполнения заданных операций на выбранной структуре ОА. В простейшем случае можно сохранить топологию графа алгоритма и просто заменить операторы во всех операторных вершинах на соответствующие микрооперации, а условия, которые анализируются в условных вершинах — на соответствующие логические условия из списка, полученного на предыдущем этапе. Однако при переходе от ГСА к микропрограмме следует всегда стремиться к уменьшению числа (операторных) вершин, что, в свою очередь, приведет к упрощению c схемы управляющего автомата. Достигнуть этого можно, например, совмещением двух или более операторных вершин ГСА в одну вершину микропрограммы, если смысл реализуемого алгоритма и разработанная ранее структура операционного автомата позволяют выполнить эти действия одновременно. Разработанная на этом этапе микропрограмма является исходной для проектирования управляющего автомата.

На этом заканчивается процесс разработки операционного автомата.

Этапы разработки управляющего автомата различны в зависимости от его типа. Для разработки микропрограммного автомата с "жесткой" логикой следует:

1. Осуществить разметку микропрограммы. Эта процедура устанавливает

соответствие между вершинами микропрограммы и состояниями автомата. В разд. 4.4.1 настоящего пособия описано, как осуществлять разметку микропрограммы для проектирования автомата Мура и автомата Мили

2. Построить граф автомата. Граф автомата строят по размеченной микропрограмме, причем вершины графа соответствуют состояниям автомата, а ребра — переходам, на этом этапе можно не показывать на графе функцию переходов.

3. Выбрать тип элемента памяти, закодировать состояния автомата. Составить автоматную таблицу переходов. Пример построения такой таблицы для случая использования в качестве элементов памяти D-триггеров приведен в разд. 4.4.1.

4. Аналогичный формат имеет таблица при использовании Т-триггеров. Если в качестве элемента памяти автомата выбран RS- триггер, в каждом разряде необходимо сформировать две функции возбуждения — для R- и S-входов.

5. Определить функции возбуждения для переключения элементов памяти. Автоматная таблица может рассматриваться как таблица истинности, задающая функции возбуждения для входов элементов памяти автомата. Все функции возбуждения в общем случае зависят от значений элементов памяти Тj и значений логических условий Хj . При необходимости можно для каждой из функций построить карту Карно и записать ее минимальное выражение. Иногда проще бывает предварительно дешифрировать состояния автомата и записать функции возбуждения в зависимости от текущего состояния автомата и слова логических условий.

6. Определить функции выходов, формирующие значения микроопераций.: Для автомата Мура функция выходов в каждом такте дискретного времени зависит только от текущего состояния автомата и значение выхода определяется содержимым операторной вершины микропрограммы, соответствующей этому состоянию автомата. В автомате Мили выходное слово соответствует содержимому той операторной вершины микропрограммы, через которую осуществляется переход из текущего состояния автомата в следующее. Поэтому функция выходов автомата Мили, как и его функция переходов, зависит от текущего состояния автомата и слова логических условий.

7. Построить функциональную схему УА. Получив выражения для функций возбуждения и выходов, можно построить функциональную схему управляющего автомата с использованием выбранных элементов памяти и стандартного базиса логических и операционных элементов.

Для разработки микропрограммного автомата с программируемой логикой следует:

1. Разбить множество микроопераций на подмножества попарно несовместимых микроопераций(этот пункт не выполняется, если выбран "вертикальный" или "горизонтальный" способ кодирования поля микро операций).

2. Определить формат микрокоманды (микрокоманд).

3. Разработать функциональную схему управляющего автомата.

4. Заполнить таблицу программирования ПЗУ микрокоманд. Проектирование управляющего автомата с программируемой логикой с различными способами адресации микрокоманд и кодирования микроопераций подробно описаны в разд. 4.4.2.

10.4. Содержание пояснительной записки

Пояснительная записка к курсовой работе должна включать следующую информацию (для вариантов с управляющими автоматами с "жесткой" логикой):

1. Титульный лист.

2. Задание на проектирование АЛУ.

3. Форматы входных, выходных и внутренних переменных, с которыми оперирует АЛУ.

4. ГСА выполняемых операций и объединенную ГСА.

5. Структурную схему операционного автомата АЛУ.

6. Функциональные схемы "нестандартных" элементов ОА. При необходимости привести процедуры синтеза операционных элементов (например, карты Карно для минимизации булевых функций).

7. Список микроопераций, реализуемых в ОА.

8. Список логических условий, формируемых в ОА.

9. Микропрограмму выполняемых в АЛУ операций в терминах микроопераций и логических условий с разметкой состояний для проектирования управляющего автомата.

10. Граф автомата.

11. Таблицу кодирования внутренних состояний автомата.

12. Описание выбранного элемента памяти (триггера) и его таблица функционирования.

13. Автоматную таблицу переходов.

14. Выражения для функций возбуждения элементов памяти (при необходимости — процедуру минимизации).

15. Выражения для функций выходов управляющего автомата.

16. Функциональную схему управляющего автомата.

17. Заключение.

18. Библиографический список.

Для вариантов с управляющими автоматами с программируемой логикой вместо информации, приведенной в кп. 9 -16, необходимо включить:

1. Микропрограмму выполняемых в АЛУ операций в терминах микроопераций и логических условий.

2. Формат или форматы микрокоманд с указанием размеров и назначения нолей.

3. Разбиение множества микроопераций ОА на подмножества несовместимых микроопераций.

4. Функциональную схему управляющего автомата.

5. Таблицу программирования ПЗУ микрокоманд.