ТОШКЕНТ АХБОРОТ ТЕХНОЛОГИЯЛАРИ УНИВЕРСИТЕТИ

Маълумот узатиш тармоқлари ва тизимлари кафедраси

РАҚАМЛИ ТЕХНИКА ВА МИКРОПРОЦЕССОРЛАР

5522100 – Телевидение, радиоэшиттириш ва радиоалоқа йўналиши талабалари учун амалий машғулотларни бажариш (Electronics Workbench (EWB)) бўйича услубий қўлланма

Тошкент 2011

Муаллифлар: Х.Ю.Абасхонова , Ж. Ю. Юнусов, Б.А. Алиев.

«Рақамли ТЕХНИКА ВА МИКРОПРОЦЕССОРЛАР».

/ ТАТУ. Тошкент, 2012.

Рақамли техника ва микропроцессорлар курсининг мақсади рақамли қурилмаларнинг тузилиш тамойиллари ва турли функционал қийинликдаги, яъни рақамли мантиқий элементлардан (МЭ) тортиб, то микропроцессорларгача (МП) бўлган рақамли қурилмаларнинг ишлатилишини ўрганишдан иборатдир.

Ушбу амалий ишларни бажариш бўйича услубий қўлланма асосида талабалар рақамли техника элементлари асосида турли қурилмаларни яратиш жараёнини ўрганадилар.

Услубий қўлланма “Телекоммуникация ” факультетининг илмий-услубий кенгашида кўриб чиқилиб, босмага тавсия этилган (“___” “ ___ “_____” йил № ____ сонли баённома)

Тақризчилар:

ЎзААА

РРТ бўлими бошлиғи

т.ф.н., доцент __________ Ю. К. Камолов

ТАТУ, «Телекоммуникация

узатиш тизимлари» кафедраси

мудири, т.ф.н., доцент __________ Р.И.Исаев

Муҳаррир: __________ К. А. Гаюбова

© ТОШКЕНТ АХБОРОТ ТЕХНОЛОГИЯЛАРИ УНИВЕРСИТЕТИ, 2012

КИРИШ

Рақамли техника ва микропроцессорлар курсининг мақсади рақамли қурилманинг тузилиш тамойиллари ва турли функционал мураккаб, яъни рақамли мантиқий элементлардан тортиб, то микропроцессорларгача бўлган рақамли қурилмаларнинг ишлатилишини ўрганишдир.

Рақамли техника ва микропроцессорлар курси дастурга мос равишда назарий материаллар, назорат ишлари, лаборатория ишлари ва курс ишларини ўз ичига олади.

Назарий материалларнинг ўзлаштирилишини осонлаштириш учун ушбу ишда методик кўрсатмалар, адабиётларга мурожаат, айрим холларда эса саволнинг кенгроқ ёритилиши, ҳамда талабага бериш учун мавжуд бўлган адабиётлардан бирини танлаб олиш имконини берувчи бир нечта адабиётлар кўрсатиб ўтилган.

Рақамли техника ва микропроцессорлар курси икки қисмга бўлинган. Биринчи қисмда асосий диққат унча қийин бўлмаган рақамли қурилмаларнинг таркиби ва қуриш тамойилларига қаратилади. Биринчи қисмдан олинган билимларни умумлаш учун талабларга уч саволдан иборат бўлган назорат иши берилади.

Иккинчи қисмда эса юқори қийинликка эга бўлган МП ва микро-ЭҲМларни қуриш тамойиллари ва уларни ишлатилиш қоидалари кўриб чиқилади.

Мазкур услубий қўлланма турли рақамли қурилмаларни синтезлаш ва яратиш бўйича амалий малака оширишга мўлжалланган.

№1 Амалий машғулот

Мантиқий элементларнинг оддий модели ва тизим параметрларнинг чиқиш қийматлари. Electronics Workbench (EWB) дастури билан танишиш.

Ишдан мақсад:

Electronics Workbench рақамли схемаларни таҳлил қилиш дастури билан ишлаш қоидаларини ўрганиш.

Кириш.

Ушбу методик кўрсатмадан мақсад мантиқий элементларнинг вазифаси ва қурилиш жараёнларини амалий ўрганиш, EWB дастуридан фойдаланган ҳолда комбинацион кетма кет турдаги кичик ва ўрта даражадаги тайёр интеграл микросхемаларни амалий ўрганиш ҳисобланади Electronics Workbench (EWB).

Ҳар қандай электрон қурилмани тузиб чиқиш физик ёки математик моделлаш билан бирга боради. Физик моделлаш катта материал сарфи билан боғлиқ бўлади; шунинг учун макетни тайёрлаш ва уларнинг ишчи сиғимини текшириш керак. Кўпинча физик моделлашда ҳаддан ташқари мураккаб қурилмаларни, мисол учун катта ва жуда катта интеграл микросхемаларни моделлаш имкони йўқ.

Бу ҳолда ҳисоблаш техникаси усулини ва воситасидан фойдаланиладиган математик моделлашга мурожаат қилинади.

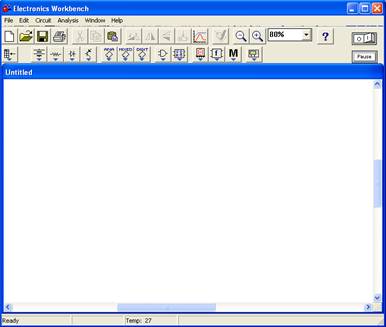

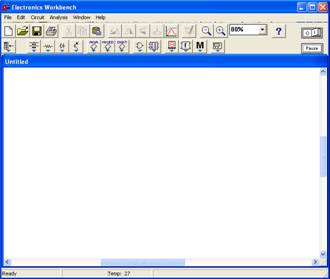

EWB барча турдаги электрон схемаларни қуриш ва анализ қилишда фойдаланилади дастурнинг ҳусусияти шуки текшириш ўлчов асбоблари аниқ ҳисобланади.Дастур ўрганишга осон ва ишлатишга етарлича қулай.

Ишни бажариш.

|

EWB дастурининг асосий панеллари ва компанентларини ўрганиш.

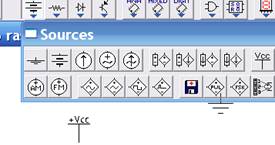

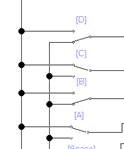

Расм 1. Компoнентлар панели

Асосий элементлар тавсифи.

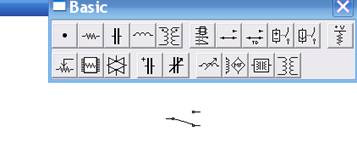

Basic - барча пассив компанентлар, шунингдек коммутация қурилмалари йиғиндиси, кутубҳона.

![]() Улаш бириктириш нуқтаси.Унга 4

тадан кўп бўлмаган ўтказгичлар уланиши мумкин.

Улаш бириктириш нуқтаси.Унга 4

тадан кўп бўлмаган ўтказгичлар уланиши мумкин.

![]()

переключател, вазифаси берилган клавиш орқали бошқарилади.

![]() П берилган вақт орқали ўзи бўлувчи

перключатель

П берилган вақт орқали ўзи бўлувчи

перключатель

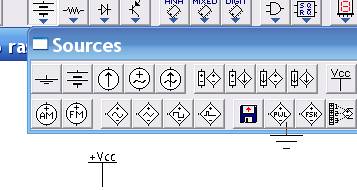

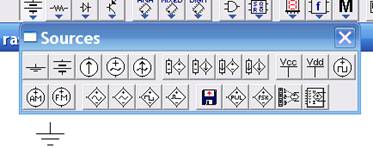

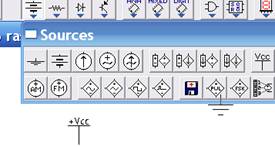

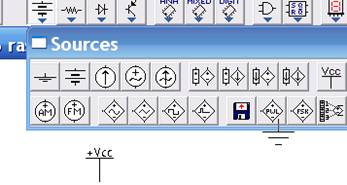

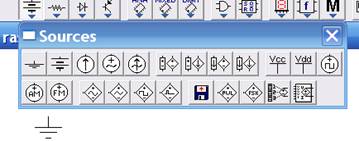

Sources - сигнал манбаалари.

Белгилаш бўйича сигнал манбаи нафақат ток манбаи, балки бошқарув манбаи ҳисобланади.

![]()

Батарея (кучланиш). Узун чизиқ мусбат клеммага уланади.

![]()

Eр билан туташтириш.

![]()

Мос равишда +5 ва 15В берувчи манбалар.

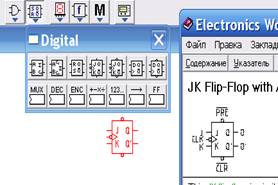

Digital ICs - рақамли микросхемалар.

![]() серияли

рақамли ИМС модели СН74 ва CД4000. Аниқ ИМС учун хх символи ўрнига

мос рақам қўйилади, мисол учун СН 7407-6 очиқ коллаекторли

буфер элементи, CД4081-4, 2И ва бошқалар.

серияли

рақамли ИМС модели СН74 ва CД4000. Аниқ ИМС учун хх символи ўрнига

мос рақам қўйилади, мисол учун СН 7407-6 очиқ коллаекторли

буфер элементи, CД4081-4, 2И ва бошқалар.

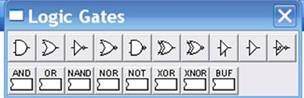

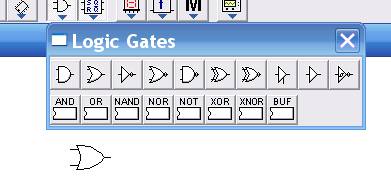

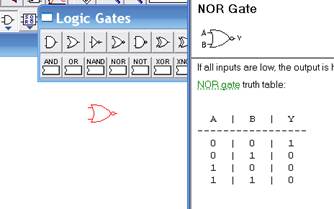

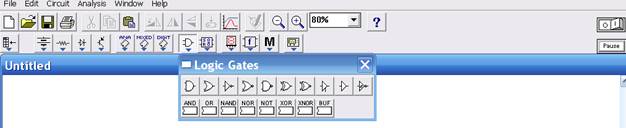

Logic Gates – мантиқий рақамли микросхемалар

![]()

![]() мантиқий элементлар ВА , ВА- ЙЎҚ

мантиқий элементлар ВА , ВА- ЙЎҚ

(чиқишлар сони). ЁКИ ЁКИ-ЙЎҚ мантиқий

элементлари (чиқишлар сони).

![]()

![]() Уч қиррали буффер (уч ҳолатли буфе) ва буфер Шмидт триггери

Уч қиррали буффер (уч ҳолатли буфе) ва буфер Шмидт триггери

ТТЛ ва КМОП серияли

рақамли

ИМС

Digital- Рақамли микросхемалар.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

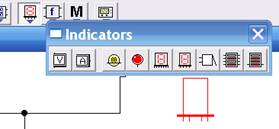

Indicators- қурилма индикатори

|

|

|

|

|

|

|

|

|

|

|

|

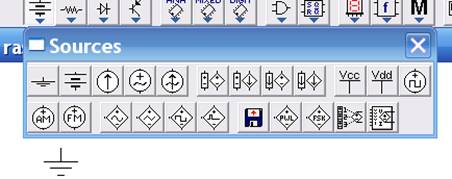

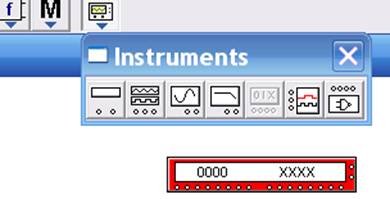

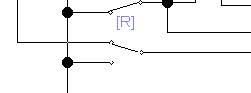

Назорат -ўлчов асбоблари.

Назорат - ўлчов асбоблари панели ишчи ойнанинг менюси остида жойлашган ва рақамли мультиметр, функционал генератор икки канални осциллограф, АЧХ ва ФЧХ ўлчагич, сўз генератори, 8 каналли мантиқий анализатор ва мантиқий ўзгартиргични ўз ичига олади. Назорат - ўлчов асбоблари кўриниш панели 2 расмда кўрсатилган. Асбоблар билан ишлаш умумий тартиби қуйидагича: керакли асбобни курсор орқали ишчи майдонга кўчирилади ва тадқиқ этилаётган схема уланади. Асбобни ишчи ҳолатда кўриш учун унинг ойнасини курсорда 2-марта босиш керак.

Расм 2. Назорат - ўлчов асбобининг панели.

Instruments – текширувчи ўлчов асбоблари .

|

|

|

|

|

|

|

|

|

|

|

|

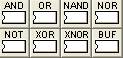

Вазифали генератор

Генераторнинг ташқи панели 3 расмда кўрсатилган. Генераторни бошқариш қуйидаги бошқарув қисми орқали амалга оширилади.

-![]() чиқиш сигналини шаклини танлаш: учбурчакли тўғрибурчакли.

чиқиш сигналини шаклини танлаш: учбурчакли тўғрибурчакли.

-![]() Чиқиш сигналининг частотасини

ўрнатиш.

Чиқиш сигналининг частотасини

ўрнатиш.

-![]() Даврий - такрорланувчи тескари вазифали катта

чиқиш сигнали амплитудасини ўрнатиш , чиқиш сигналини силжишини

ўрнатиш.

Даврий - такрорланувчи тескари вазифали катта

чиқиш сигнали амплитудасини ўрнатиш , чиқиш сигналини силжишини

ўрнатиш.

-![]() чиқиш сигнали амплитудасини

ўрнатиш.

чиқиш сигнали амплитудасини

ўрнатиш.

-![]() чиқиш сигналини силжишини

ўрнатиш.

чиқиш сигналини силжишини

ўрнатиш.

Расм 3 - вазифали генераторнинг кўриниш панели.

Оссиллограф

Оссиллографнинг ташқи кўриниш панели 4 расмда кўрсатилган. Осилограф 2та каналга эга. “А ва Б” 10 мкв/дел дан 5кВ/дел гача диапазондаги таъсирни бўлиб ростлаш билан ва вертикал бўйича силжишини ростловчилар. Кириш бўйича режимни танлаш учун қуйидаги тугмача босилади.

![]() .

АC режими фақат ўзгарувчан ток

сигналини назорат қилиш учун мўлжалланган. О режимида кириш

қисқичи эрга уланади. Д C режимида доимий

ва ўзгарувчан токларни Осилографик ўлчовларни амалгам ошириш мумкин. Бу режим

яна “очиқ ”, “кириш” режими деб номланади.

.

АC режими фақат ўзгарувчан ток

сигналини назорат қилиш учун мўлжалланган. О режимида кириш

қисқичи эрга уланади. Д C режимида доимий

ва ўзгарувчан токларни Осилографик ўлчовларни амалгам ошириш мумкин. Бу режим

яна “очиқ ”, “кириш” режими деб номланади.

Расм 4-Осилографнинг олди панели.

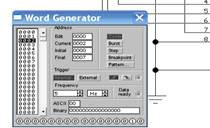

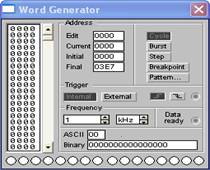

Сўз генератори.

Очиқ ҳолатдаги сўз генераторининг ташқи кўриниши 5 расмда кўрсатилган. Генератор (уни яна код генератори дейилади.) -8 разрядли иккиликдаги сўзларни 16 ликда ишлаш учун мўлжалланган, қайсики экранга фойдаланувчи томонидан киритилади. Ташқи панелнинг чап қисмида жойлашган. Иккилик комбинацияларини териш учун мос разрядга сичқончани босиш керак ва клавиатура билан ёки 1ни киритиш керак. Кейинги экран чизиғи ўрнини алмаштиришда сичқонча ёрдами билан эмас курсор бошқарув тугмасида қулай ўтказилади.

Расм 5- сўз генераторининг ташқи кўриниш панели.

Маълум бир формага эга бўлган сўз асбобининг паст қисмида жойлашган 8 та чиқиш клемма - индикаторларига берилади. Олдинги ва кейинги фронт бўйича юклашда берилган тугма фойдаланилади.

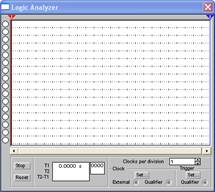

Мантиқий анализатор.

Мантиқий нализаторнинг ташқи кўриниши 6 расмда кўрсатилган. Анализатор манитор экранида 8 - разрядли ков кетма кетлигини бир вақтда схеманинг 8 нуқтасида тасвирлаш, шунингдек НEХ ойнасида 16 лик кўринишга кириш клемма индикаторларида эса иккилик сонлар кўринишида тасвирлаш учун мўлжалланган. CЛEАР тугмасини босиш орқали экранда маълумотлар тозаланади.

Расм 6 -мантиқий анализаторнинг ташқи кўриниши.

Триггер блокида мусбат ёки манфий қутбли сигналларни юклаш тугмаси ва доимий синхронизация манбаасини улаш учун клемма, масалан сўз генераторини улаш учун клемма, жойлашган. (external тугмасини босиш орқали уланади). Шунга кўра берилган иккилик комбинацияларни юклаш ва автоюклаш, кўриниб турган дарчага фойдаланувчи 1,0 ёки х ни клавиатурадан киритиш йўли билан ўрнатиши (ноаниқ ҳолатда ) учун дастлаб керакли разрядга сичқончани босиши кераклигини кўзда тутади.

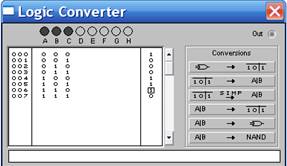

Мантиқий ўзгартиргич.

Расм 7. Мантиқий ўзгартиргичнинг ташқи кўриниши

Расм 7 да кўрсатилган. Ўзгартиргичнинг панелида А, Б…….., ва битта OUT чиқиши, текширилаётган схема чинлик жадвалини тасвирлаш учун ойна, уни бўладиган ифодаларини тасвирлаш учун (экран) ойна қатори кўрсатилган. Панелнинг ўнг қисмида ўзгартиргич амали жараёнини бошқарувчи тугма жойлашган. Ўзгартиргичнинг фойдаланиш мумкин бўлган вариантлари:

а) н киришли бир чиқишли мантиқий анализатор қурилмаси. Бу ҳолда бошқариш тугмаларидан фойдаланилади, ва текширилаётган схеманинг чинлик жадвали амалдаги қурилмага мос бўлган амали минилизацияси; чексиз турдаги мантиқий элементли қурилма схемаси; фақат И-НE матиқий элементидаги қурилма схемаси олинади.

Схема яратилишининг асосий жараёнлари.

EWB электрон моделлаш тизими билан ишлаш 3 та асосий босқични ўз ичига олади:

Схема яратиш, ўлчов асбобларини танлаш ва улаш ва оҳиргиси ҳисоблаш жараёнларини бажариш, текширилаётган қурилмага боғлиқ бўлган.

Схеманинг ажратилган қисмларини (қизил рангда тасвирланган) бураб айлантириш мумкин. (Стрл + р тугмаларини биргаликда босиш ёрдамида, контект менюдаги ускуналар панели тугмаси ёки cирcуит > ротате менюси ёрдами билан) ёки ойна вертикал менюси бўйлаб акс эттирилади, контекст менюсидаги ускуналар панели тугмаси орқали компанентлари 90 га соат стрелкаси бўйича буриш учун ҳамма буйруқлар бажарилади. Ўлчов асбоблари учун уланиш клеммалари ўзгаради.

Тайёр схемаларда мақсадга мувофиқ элементларни акс эттириш, айлантириб бураш фойдаланилади.

Схема қисмларини белгисини 2 марта босиш билан уларнинг ҳусусиятларини ўзгартириш мумкин. Очилган мулоқат ойнасига керакли параметрлар ўрнатилади. (Ўтказгич ранги, регистор қаршилиги, трансистор тури) ва ок тугмаси босиб ёки “энтер” тугмаси босиш орқали тасдиқланади. Кўп миқдордаги схема қисмлари учун ҳар ҳил турдаги мос реал элементларни параметрини танлаш мумкин, компанентлар (схема қисмлари) жойлаштирилгандан сўнг, уларнинг чиқиш ўтказгичларига боғловчилар ўтказилади. Шуни ҳисобга олиш керакки компанентларнинг чиқишига фақат битта ўтказгич улаш мумкин бўлади. Улашни бажариш учун сичқонча курсори компанент чиқишига келтирилади ва чап тугмача босилади, ва сичқонча тугмаси қўйиб юборилгандан сўнг уланиш бажарилади.

Улаш учун керак бўлган бошқа ўтказгичларга боғлаш нуқтаси банс кутубҳонасидан танланади ёки аввал ўрнатилган ўтказгичлардан кўчириб ўтказилади.

Агар бу нуқта ҳақиқатдан ўтказгич билан электрик уланса, у тўлиқ қора рангга бўялади. Агар унда кесушувчи ўтказгичлардан из кўринса, электрик боғланиш йўқ бўлади, бу нуқтани қайтадан ўрнатиш керак. Ўрнатиш мувофақиятли амалга оширилгандан сўнг уланиш нуқтасига яна 2 та ўтказгич улаш мумкин бўлади. Агар уланишни узиш зарур бўлса курсор схема компаненти чиқишларидан бирига ёки уланиш нуқтаси устига келтирилади ва пайдо бўлган майдонга чап тугма босилади, бу тугма қўйиб юборилгандан кейин ўтказгич ишчи майдоннинг бўш қисмига олиб келинади.

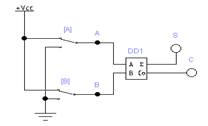

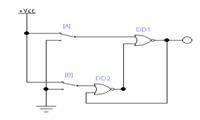

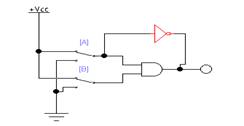

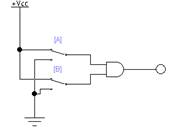

ВАРИАНТЛАР

EWB дастури ёрдамида ўзингизни схемангизни чизинг

|

Вариант рақами |

схема |

Вариант рақами |

схема |

|

|

|

1. |

|

2. |

|

|

|

|

3. |

|

4. |

|

|

|

|

5. |

|

6. |

|

|

|

|

7. |

|

8. |

|

|

|

|

9. |

|

10. |

|

|

|

|

11. |

|

12. |

|

|

|

|

13. |

|

14. |

|

||

|

15. |

|

16. |

|

||

|

17. |

|

18. |

|

||

|

19. |

|

20. |

|

||

|

21. |

|

22. |

|

||

|

23. |

|

24. |

|

||

|

25. |

|

26. |

|

|

|

|

27. |

|

28. |

|

|

|

|

29. |

|

30. |

|

|

|

Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма кетлиги

· 1-топшириқ бажарилгандан кейинги натижалар

· 2-топшириқ номи

· 2-топшириқ бажарилиш кетма кетлиги

· 2-топшириқ бажарилгандан кейинги натижалар

· Компютерда олинган Моделлаштириш натижалари

· EWB дастуридаги яратилган схемалар (web файллар).

· Иш бўйича ҳулоса

№2 Амалий машғулот

Комбинацион чизмаларнинг умумий базисдаги синтези

Ишдан мақсад

Мазкур амалий иши талабарни асосий мантиқий элементлар, уларнинг функсиялари, минимизация қилиш ва амалдаги мантиқий элементлар ёрдамида схемаларни йиғишни ўрганадилар. Комбинацион дискрет автоматлар устида тажрибавий ишлар олиб бориш, схемани йиғшни ўрганиш ҳамда уларни интеграл схема кўринишида йиғишлари мумкин.

Назарий маълумотлар

Бизга маълумки, рақамли математикани арифметика элементлари асосини 0 ва 1 сонлари ташкил этади. Бу иккилик кодларини танланиши мураккаб схемаларда, уларни бошқаришни енгиллаштириш учун оддийгина фақат иккита ҳолатга яъни уланган (ёқилган) ва узилган (ўчирилган) ҳолатларига эга бўлган калит ишлатилган. Рақамли техникада бундай калитларни мантиқий элементлар деб аташ қабул қилинган. Бу мантиқий элементлар ўзининг бажарадиган вазифасига қараб ҳар хил номга ҳамда график белгиланишга эга.

Амалий иши мантиқий элементлар мантиқий қурилмаларни қуришда ва ўрганишда бизга катта ёрдам берадиган EWB дастуридан фойдаланамиз.

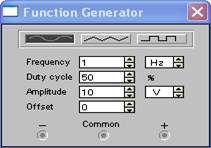

Расм 8 . EWB 5.12 дастурида қўлланиладиган асосий МE ларнинг номлари ва график белгиланишлари

|

Асосий М E ларни чапдан ўнгга қараб санаб ўтамиз: 2-Input AND Gate – 2 киришли ВА мантиқий элемент, 2-Input ОР Gate – 2 киришли ВА мантиқий элемент, NOT Gate – инвертор (ИНКОР, EМАС мантиқий элементл), 2-Input XOR Gate – 2 киришли ЁКИ - EМАС мантиқий элемент, 2-Input NAND Gate – 2 киришли ВА - EМАС мантиқий элемент, 2-Input ХОР Gate – 2 киришли ЁКИ ни инкорловчи мантиқий элемент, 2-Input ХXOR Gate – 2 киришли ЁКИ - EМАС мантиқий элемент, Тристате Буффер – уч ҳолатли чиқиш буфери, Буффер – буффер, Shmitte Trigger – Шмитт инкор триггери. |

Ишни бажариш.

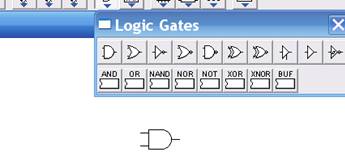

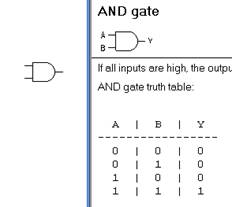

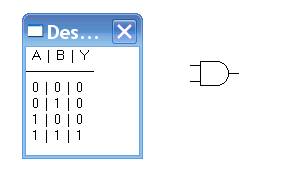

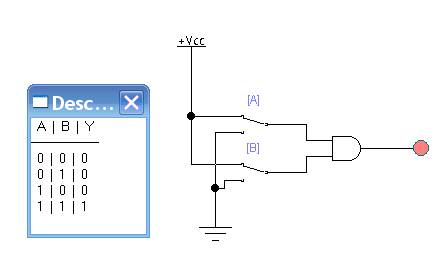

ВА (AND) мантиқий элементини моделлаштириш.

|

EWB да Logic Gateс гуруҳига кириб, 2-input AND Gate ни танлаймиз

|

|

|

2-input AND Gate ни белгилаб F1 тугмасини босамиз

|

|

|

Ёрдам да чиққан чинлик жадвалини “Description ” ойнасига кўчириб қўямиз |

|

Маслаҳат : Юқоридаги амални барча элементларни ўрганиш учун қўллаш мумкин.

|

EWB да Sources гуруҳига кириб , доимий кучланиш манбаи +5В. (+Vss Voltage Source) ни танлаймиз. |

|

|

EWB да Sources гуруҳига кириб, Ground ни танлаймиз |

|

|

Кейин 2 та переключател танлаймиз |

|

|

Мантиқий индикаторни танлаймиз |

|

Қуйидаги схемани йиғамиз:

Йиғилган схема анализи:

![]() тугмасини босиб

моделлаштиришни ишга туширамиз

тугмасини босиб

моделлаштиришни ишга туширамиз

Моделированияни ёқиб ва А, Б тугмаларини босиб, мантиқий элементлар киришига берилиши мумкин бўлган ҳамма комбинацияларни беришимиз мумкин. Уни тушишидаги индикаторни кузатиб ва ҳоларлар жадвали билан солиштириб, мантиқий элемент фақат бир ҳолдагина: А=1 ва Б=1 бўлган ҳолдагина & мантиқий элементининг чиқишида мантиқий “1” (й=1 индикатор ёнади) ҳосил бўлади.

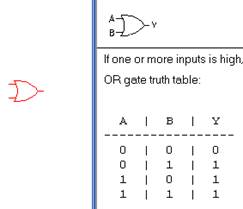

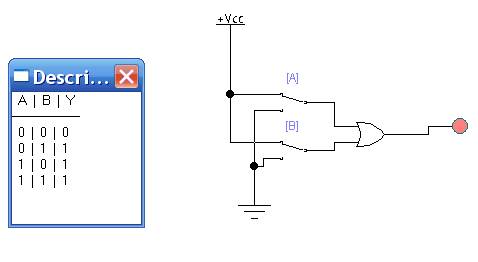

Ёки (ОР) мантиқий элементини моделлаштириш.

|

EWB да Logic Gateс гуруҳига кириб, 2-input ОР Gate ни танлаймиз

|

|

|

2-input ОР Gate ни белгилаб F1 тугмасини босамиз

|

|

|

Ёрдамда чиққан чинлик жадвалини “Description ” ойнасига кўчириб қўямиз |

|

Қуйидаги схемани йиғамиз:

Йиғилган схема анализи:

![]() тугмасини босиб

моделлаштиришни ишга туширамиз

тугмасини босиб

моделлаштиришни ишга туширамиз

Уни устида ҳам тажриба ўтқазиб, у фақат бир ҳолатда , яъни А=0 ва Б=0 ҳолатда 0 Gateнг бўлиши малум бўлади.

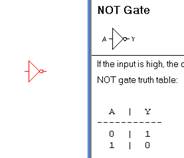

Йўқ (NOT) мантиқий элементини моделлаштириш.

|

EWB да Logic Gateс гуруҳига кириб, 2-input NOT Gate ни танлаймиз

|

|

|

2-input NOT Gate ни белгилаб F1 тугмасини босамиз

|

|

|

Ёрдамда чиққан чинлик жадвалини “Description ” ойнасига кўчириб қўямиз |

|

Қуйидаги схемани йиғамиз:

Йиғилган схема анализи:

![]() тугмасини

босиб моделлаштиришни ишга туширамиз

тугмасини

босиб моделлаштиришни ишга туширамиз

Бу мантиқий элемент фақат 1 - та кириш ва 1 - та чиқишга эга. Шунингдек, унинг чиқишида кичик ойнача қўйилган у инверс белгисидир. Унинг киришига 0 берсак чиқишида 1 ҳосил бўлади. Агар мантиқий элементни ҳеч қайси манбаага уламасдан чиқишига лампани улаб қўйсак, ёниб қолади. Чунки киришда ҳеч қандай манба бўлмаса ҳам, ҳеч нима йўқ дегани, мантиқий “0” дегани бўлиб , чиқишида мантиқий “1” ҳосил бўлади.

Вариантлар

|

№ |

1-топшириқ Схемани моделлаштириш |

2-топшириқ Йиғилган схема анализи |

|

31. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

32. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

33. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

34. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

35. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

36. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

37. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

38. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

39. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

40. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

41. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

42. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

43. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

44. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

45. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

46. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

47. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

48. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

49. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

50. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

51. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

52. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

53. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

54. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

55. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

56. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 0; Ф2= 1; |

|

57. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 0; |

|

58. |

Йўқ (NOT) мантиқий элементини моделлаштириш. |

F1= 1; |

|

59. |

Ёки (ОР) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

|

60. |

ВА (AND) мантиқий элементини моделлаштириш. |

F1= 1; Ф2= 0; |

Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма - кетлиги

· 1-топшириқ бажарилгдан кейинги натижалар

· 2-топшириқ номи

· 2-топшириқ бажарилиш кетма - кетлиги

· 2-топшириқ бажарилгдан кейинги натижалар

· Компютерда олинган Моделлаштириш натижалари

· EWB дастуридаги яратилган схемалар (web файллар)

· Иш бўйича ҳулоса

№ 3 Амалий машғулот

Комбинацион дискрет автомат автоматларни «И–НЕ», «ИЛИ-НЕ» базисларида синтези.

ВА-ЙЎҚ, ЁКИ-ЙЎҚ ва Шеффер–Пирс мантиқий қурилмасидаги инверторни синтез қилиш

Ишдан мақсад

ВА-ЙЎҚ, ЁКИ-ЙЎҚ ва Шеффер–Пирс мантиқий қурилмасидаги инверторни синтез қилиш.

Назарий маълумотлар

Eнди биз 3 та асосий мантиқий элементларга (ВА, ЁКИ, EМАС ) эга бўлиб, уларни ўзаро бирлаштириб, комбинацион мантиқий элементларни йиғиндисини ҳосил қилишимиз мумкин. Улар бунданда мураккаб мантиқий функсияларни бажариши мумкин. Бу ҳолда тескари алоқаларни ва вақтли ушланиб қолишларни ҳисобга олмасак, улардан турли ҳилдаги комбинацион қурилмаларни қуриш мумкин.

Ишда мантиқий элементлар мантиқий қурилмаларни қуришда ва ўрганишда бизга катта ёрдам берадиган EWB дастуридан фойдаланамиз.

Расм 9. EWB 5.12 дастурида қўлланиладиган асосий МE ларнинг номлари ва график белгиланишлари

Ишни бажариш.

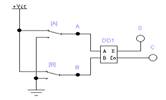

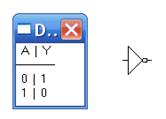

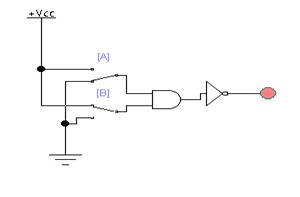

ВА-ЙЎҚ мантиқий элементини моделлаштириш.

|

ВА мантиқий элементини чиқишида EМАС мантиқий элементини EWB даги схемасини 2 та асосий мантиқий элементлар AND ва NOT ларни қуйидагича қуриш орқали амалга оширамиз.

|

|

|

Тажриба натижасида бу элемент фақат А=1 ва Б=1 ҳолдагина Y=0 бўлишини аниқлаймиз. |

|

|

Бу элементнинг инглизча NAND бўлиб, у Logic Gateс да тайёр ҳолда туради ва у пиктограммадан 2-INput NAND Gate танлаш орқали амалга оширилади. |

|

|

Расмдаги AND ва NOT элементларини NAND билан алмаштириб чиқишда расмдаги ҳолатга келамиз, тажриба қилиб расмдаги жадвал билан бир ҳил эканлигини кўрамиз. |

|

|

Уни AND мантиқий элементининг жадвали билан солиштирсак, ҳақиқатдан ҳам иккаласи бир бирига тескари қарама қарши эканлиги маълум бўлади. |

|

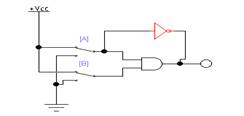

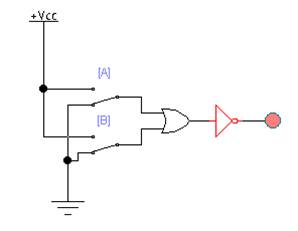

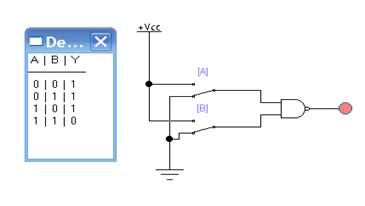

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш.

|

ЁКИ мантиқий элементини чиқишида EМАС мантиқий элементини EWB даги схемасини 2 та асосий мантиқий элементлар OR ва NOT ларни қуйидагича қуриш орқали амалга оширамиз.

|

|

|

Бу мантиқий элементнинг ҳолатлар жадвали фақат киришига “0” берилганда чиқишида “0” ҳосил бўлади. EWB дастурида NOR нинг киришига ҳеч нарса уланмаса унинг чиқишида 1 ҳосил бўлади |

|

|

Бу элементнинг инглизча NOR бўлиб, у Logic Gateс да тайёр ҳолда туради ва у пиктограммадан 2-INput NOR Gate танлаш орқали амалга оширилади. |

|

|

Расмдаги AND ва NOT элементларини NOR билан алмаштириб чиқишда расмдаги ҳолатга келамиз, тажриба қилиб расмдаги жадвал билан бир ҳил эканлигини кўрамиз. |

|

|

Уни OR мантиқий элементининг жадвали билан солиштирсак, ҳақиқатдан ҳам иккаласи бир бирига тескари қарама қарши эканлиги маълум бўлади. |

|

Кўрсатма. EWB дастурида схема йиғиш вақтида алоҳида компанентларни улаш вақтида, уларни уланганлиги тўғрисида алоҳида белги кўрсатилмайди, ва улар уланмай қолса катта ҳатоликни келтириб чиқаради. Шунинг учун улаш давомида қўшимча улаш линияларидан ёки уловчи тугунлардан фойдаланишга ҳаракат қилинг.

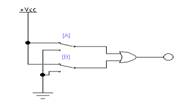

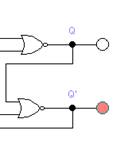

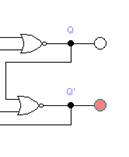

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш

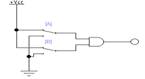

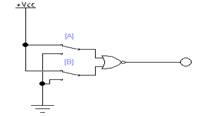

NAND ва AND мантиқий элементини яъни шеффер ва пирс элементларини кўриб чиқиш давомида шунга амин бўлдики, А=Б ҳолатда яни иккала киришга “0” ёки “1” берилган вақтда улар оддий инверторга айланиб қолишади. (Расм 10) да қуйидаги схемани йиғиб текшириб кўриш мумкин.

Расм 10. NAND ва AND

Вариантлар

|

№ |

1 - топшириқ Схемани моделлаштириш |

2 - топшириқ Йиғилган схема анализи |

|

1 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

2 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

3 |

Шеффер –Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 0; |

|

4 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

5 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

6 |

Шеффер –Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 1; |

|

7 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

8 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

9 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 0; |

|

10 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

11 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

12 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 1; |

|

13 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

14 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

15 |

Шеффер –Пирс мантиқий қурилмасидаги инверторни синтез қилиш |

F1= 0; |

|

16 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш |

F1= 1; F2= 0; |

|

17 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

18 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 1; |

|

19 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

20 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

21 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 0; |

|

22 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

23 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

24 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 1; |

|

25 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

26 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 0; F2= 1; |

|

27 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 0; |

|

28 |

ВА-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

29 |

ЁКИ-ЙЎҚ мантиқий элементини моделлаштириш. |

F1= 1; F2= 0; |

|

30 |

Шеффер – Пирс мантиқий қурилмасидаги инверторни синтез қилиш. |

F1= 1; |

7.9. Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма кетлиги.

· 1-топшириқ бажарилгандан кейинги натижалар.

· 2-топшириқ номи.

· 2-топшириқ бажарилиш кетма - кетлиги.

· 2-топшириқ бажарилгандан кейинги натижалар.

· Компютерда олинган моделлаштириш натижалари.

· EWB дастуридаги яратилган схемалар (web файллар).

· Иш бўйича ҳулоса.

№4 Амалий машғулот

Кўп тактли дискрет автоматларнинг синтези.

(Триггерлар синтези). Триггерни моделлаштириш ва текшириш

Ишдан мақсад:

EWB дастурида триггер схемасини ўрганиш.

Назарий маълумотлар

Триггерлар - бу икки барқарор ҳолатдан биттасида бўлувчи (1 ёки 0) ва ташқи сигнал таъсири остида кетма - кетлик билан алмашиниб туриш ҳолатига эга бўлган электрон қурилмаларнинг ката синфидир. Триггерлар хотирали элементлар ҳисобланади. Уларнинг холати нафақат вақт моментида киришга берилган сигналларни қўшишга боғлиқ бўлади, балки сигнал олдингисига хам таъсир кўрсатади.

Аввал кўрсатиб ўтилганидек «триггер» сўзи инглизча тепкили қурилма, тепки, туртки

деган маънони англатади. Инглиз тилидаги адабиётларда бу термин одатда «ишга туширмоқ» феъли маъносида қўлланилади. Мисол учун айнан Flip-Flop (щелчок - хлопок) атамаси баъзан инглизча адабиётларда «триггер» сўзига синоним ҳолда хизмат қилади.

Триггерлар тарихи 1918 йилда бошланган. Ўша вақтда улар электрон лампаларда ишлатилган. М.А Бонч-Бруевич узулишли ҳолатга эга бўлган катод реле схемасини тасвирлаган. Икки барқарор ҳолатга эга бўлган Амалий схема инглиз физиклари Уильямом Генри Икклзом (W Н. Eccles) ва Ф.В. Джорданом (FW Jordan) томонидан эълон қилинган.

Охирги схема Икклза - Джордана триггери деб номланади.

Ишни бажариш.

|

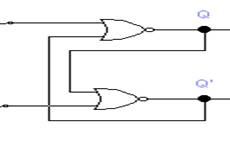

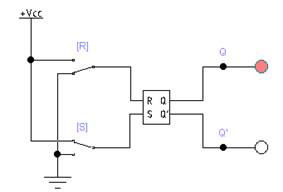

RS триггерни моделлаштириш

RS - триггер номи ўзининг киришлари номидан олинган.S кириш (Set – ўрнатиш ) Q триггер чиқишига бирлик холатни ўрнатишда қўлланилади. R кириш (Reset – тушириш) Q (Quit – чиқиш) триггер чиқишини ноллик холатга туширишда қўлланилади.

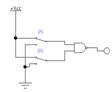

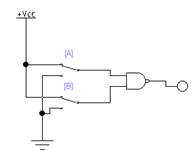

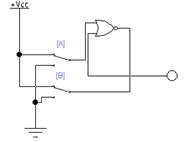

RS-триггерни амалга ошириш учун “2 И-НЕ” мантиқий элементи фойдаланилади.Унинг принципал схемаси қуйидаги расмда кўрсатилган.

Расм 11. 2 - И мантиқий элементи

11- расмда ишни тасвирловчи тўлиқ схемасини кўриб чиқамиз. R ва S киришларга бошланишда бирлик потенциаллар берилади. Агар юқори мантиқий элемент “2 И-НЕ” Q чиқишида мантиқий нол хосил бўлса, пастки “2 И-НЕ” мантиқий элемент чиқишида мантиқий бир хосил бўлади. Бу бир Q чиқишдаги мантиқий нольни тасдиқлайди. Агар юқори мантиқий элемент “2И-НЕ” Q чиқишида аввал мантиқий бир хосил бўлса, пастки “2 И-НЕ” мантиқий элемент чиқишида мантиқий ноль пайдо бўлади. Бу ноль Q чиқишдаги мантиқий бирни тасдиқлайди.

RS - триггернинг холатлар жадвали

Вариантлар

|

№ |

Е1 |

Е2 |

Qn+ı |

№ |

Е1 |

Е2 |

Qn+ı |

|

1

|

0 1 0 1 |

0 0 1 1 |

1 0 0 Qn |

15 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 Qn |

|

22 |

0 1 0 1 |

0 0 1 1 |

0 1 1 –Qn |

16 |

0 1 0 1 |

0 0 1 1 |

1 0 1 Qn |

|

3 |

0 1 0 1 |

0 0 1 1 |

0 1 0 Qn |

17 |

0 1 0 1 |

0 0 1 1 |

0 1 Qn –Qn |

|

4 |

0 1 0 1 |

0 0 1 1 |

1 1 0 –Qn |

18

|

0 1 0 1 |

0 0 1 1 |

1 –Qn 0 Qn |

|

5 |

0 1 0 1 |

0 0 1 1 |

Qn 1 0 0 |

19 |

0 1 0 1 |

0 0 1 1 |

Qn 1 –Qn 0 |

|

6 |

0 1 0 1 |

0 0 1 1 |

–Qn 1 0 1 |

20 |

0 1 0 1 |

0 0 1 1 |

Qn 0 1 1 |

|

7 |

0 1 0 1 |

0 0 1 1 |

Qn 1 1 0 |

21 |

0 1 0 1 |

0 0 1 1 |

0 Qn Qn 1 |

|

8 |

0 1 0 1 |

0 0 1 1 |

1 –Qn 1 0 |

22 |

0 1 0 1 |

0 0 1 1 |

1 –Qn Qn 0 |

|

9

|

0 1 0 1 |

0 0 1 1 |

0 Qn 1 1 |

23 |

0 1 0 1 |

0 0 1 1 |

0 0 1 1 |

|

10 |

0 1 0 1 |

0 0 1 1 |

1 –Qn 1 0 |

24 |

0 1 0 1 |

0 0 1 1 |

1 0 1 0 |

|

11 |

0 1 0 1 |

0 0 1 1 |

1 1 Qn 0 |

25 |

0 1 0 1 |

0 0 1 1 |

1 1 0 0 |

|

12 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 0 |

26 |

0 1 0 1 |

0 0 1 1 |

0 1 1 0 |

|

1 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 Qn |

27 |

0 1 0 1 |

0 0 1 1 |

1 0 0 1 |

|

14 |

0 1 0 1 |

0 0 1 1 |

1 Qn 0 –Qn |

28 |

0 1 0 1 |

0 0 1 1 |

1 0 Qn –Qn |

Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма - кетлиги.

· 1-топшириқ бажарилгандан кейинги натижалар.

· 2-топшириқ номи.

· 2-топшириқ бажарилиш кетма - кетлиги.

· 2-топшириқ бажарилгандан кейинги натижалар.

· Компютерда олинган моделлаштириш натижалари.

· EWB дастуридаги яратилган схемалар (web файллар).

· Иш бўйича ҳулоса.

№ 5,6 Амалий машғулот

Кўп тактли дискрет автоматларнинг

синтези (Бир триггер асосида иккинчи триггер синтези) ТРИГГЕРЛАР ВАҚТ ДИАГРАММАСИ

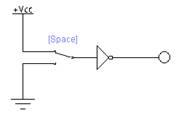

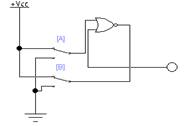

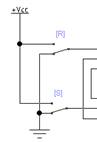

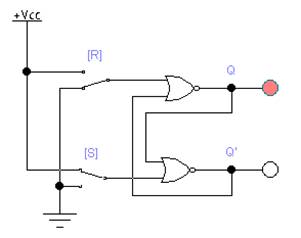

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш

Моделлаштириш бўйича ишлаш режаси

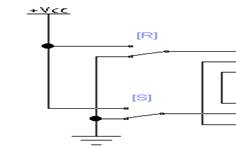

|

Sources гуруҳига кириб, +5V (+Vcc Voltage Sources) доимий кучланиш манбасини танлаймиз |

|

|

«ер (ер билан туташтириш)» (программада уланган деб хисоблаймиз) |

|

|

Кейин икки переключателни (туташтиргич) танлаймиз |

|

|

Мантиқий индикаторни танлаймиз |

|

|

«Йиғилган» мантиқий элемент мантиқий элемент блоки тўпламидаги УГО пиктограммасидан танланади: J2-lnput NOR Gate – икки киришли МЭ ИЛИ--НЕ |

|

Қуйида кўрсатилган RS триггер схемасини йиғамиз.

Схема устида ишлаш:

![]() тугмани босиб моделни ёқамиз.

тугмани босиб моделни ёқамиз.

Бизга берилган вариант бўйича R =1; S=0 кириш сигналидаги Q сакл қийматини топиш керак.

|

Бунда бизга R =1; S=0 кириш сигналидаги Q сакл қиймати керак. Биз: · R переключательни 1 ҳолатга ўрнатамиз · S переключательни 0 ҳолатга ўрнатамиз

|

|

|

Чиқиш сигналини аниқлаймиз: Агар индикатор ёнса – у 1 га тенг, ёнмаса сигнал 0 га тенг.

Бизнинг ҳолда Q` = 1; Q=0 бўлади.

|

|

|

Бизга Qсакл қиймати керак, кириш сигналларини бекор қиламиз · R переключательни 0 ҳолатга ўрнатамиз. · S переключательни 0 ҳолатга ўрнатамиз.

|

|

|

Чиқиш сигналини аниқлаймиз: Агар индикатор ёнса – у 1 га тенг, ёнмаса сигнал 0 га тенг.

Бизнинг холда Q` = 1; Q=0 бўлади.

|

|

|

Тахлил натижаси Q` = 1; Q=0 |

|

|

Барча иншоатларни Jpeg форматида сақлаймиз ва ўзимизнинг ҳисоботимизга киргизамиз.

|

|

Ягона элемент асосида RS триггерни моделлаштириш

Моделлаштириш бўйича ишлаш режаси

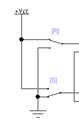

|

Digital менюсидан ишчи майдонга RS-Flip Fop ни оламиз |

|

|

Кейин юқорида кўрсатилган усулда v Indicator v +Vcc Voltage v «ер» v Переключатель (туташтиргич) элементларни ишчи майдонга жойлаштирамиз |

|

Қуйида кўрсатилган RS триггер схемасини йиғамиз

Расм 12. RS триггер схемаси

Схема устида ишлаш:

![]() тугмани босиб моделни

ёқамиз.

тугмани босиб моделни

ёқамиз.

Бизга берилган вариант бўйича R =1; S=0 кириш сигналидаги Q сакл қийматини топиш керак.

|

Бунда бизга R =1;S=0 кириш сигналидаги Q сакл қиймати керак. Биз: · R переключательни 1 ҳолатга ўрнатамиз · S переключательни 0 ҳолатга ўрнатамиз

|

|

|

Чиқиш сигналини аниқлаймиз: Агар индикатор ёнса – у 1 га тенг, ёнмаса сигнал 0 га тенг, Бизнинг ҳолда Q` = 1; Q=0 бўлади.

|

|

|

Бизга Q сакл қиймати керак, кириш сигналларини бекор қиламиз. · R переключательни 0 ҳолатга ўрнатамиз. · S переключательни 0 ҳолатга ўрнатамиз.

|

|

|

Чиқиш сигналини аниқлаймиз: Агар индикатор ёнса – у 1 га тенг, ёнмаса сигнал 0 га тенг,

Бизнинг ҳолда Q` = 1; Q=0 бўлади.

|

|

|

Таҳлил натижаси: Q` = 1; Q=0; |

|

|

Барча иншоатларни Jpeg форматида сақлаймиз ва ўзимизнинг хисоботимизга киритамиз.

|

|

Вариантлар

|

№ |

1-топшириқ Схемани моделлаштириш |

2-топшириқ Йиғилган схема анализи |

|

1. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

2. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

3. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

4. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

5. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

6. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

7. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

8. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

9. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

10. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

11. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

12. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

13. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

14. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

15. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

16. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

17. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

18. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

19. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

20. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

21. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

22. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

23. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Q сакл ни қийматини топинг. |

|

24. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=1 кирувчи сигналларда натижавий Qсакл ни қийматини топинг. |

|

25. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

26. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

27. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

28. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =1 ва S=1 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

29. |

Мантиқий элементлар блоки асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

|

30. |

Ягона элемент асосида RS триггерни моделлаштириш |

R =0 ва S=0 кирувчи сигналларда натижавий Q ни қийматини топинг. |

№7,8 Амалий машғулот.

Ҳисоблагичлар синтези (Қўшувчи ва айрувчи хисоблагичлар). Ҳисоблагичлар синтези (Ихтиёрий тартибли хисоблагичлар)

хисоблагичЛАРНИ МОДEЛЛАШТИРИШ ВА ТАДҚИҚ EТИШ.

Ишдан мақсад.

Ҳисоблагичларнинг ишлаш принципи ва вазифаси билан танишиш.

Ҳисоблагичларнинг икки тактли амалий схемаси билан танишиш ва уни тадқиқ этиш.

Назарий маълумот.

Ҳисоблагичлар – чиқишидаги сигналларни белгиланган код бўйича импульс миқдорини кўрсатадиган қурилма ҳисобланади. Т - Триггер 2 гача санайдиган оддий ҳисоблагичларга мисол бўлади.

Ҳисоблагич т - та триггер занжирларидан тузилган бўлса иккилик кодда Ксч=2м импульсни санаб ҳисоблаши мумкин. Ҳар бир триггерлардан келиб чиққан ҳисоблагичлар разряди аниқланади. Кеч миқдори ҳисоблагичлар триггер чиқишидаги ҳар ҳил ҳолатлар миқдорига тенг бўлади ва ҳисоблаш модули деб номланади. Чиқиш импульслари сони ва ҳисоблагичнинг ҳолати фақат биринчи сикл учун аниқланади, шундан кейин кириш импульслари миқдори кечгача оширилади, ҳисоблагич нольи ҳолатга қайтарилади ва шу ишлаш сикли қайтарилади.

Ҳисоблагич – бу белгиланган вақтда унга кирувчи импульслар миқдорини ҳисобловчи қурилмадир. Унинг асосий статиc ҳусусияти ҳисоблаш модели М (сиғими) ҳисобланади, ҳисоблаш модели санаши мумкин бўлган миқдор ҳолатини аниқлайди. М ҳисоблагичга сигналлар кириши бошлангандан сўнг одатда янги сикл бошланади. қайсики такрорланувчи ҳисоблагичнинг асосий динамик ҳарактеристикаси тезкорлиги ҳисобланади.

Ҳисоблагичлар: кодлаш усули ички ҳолати бўйича (иккилик жонсон ҳисоблагичи ва бошқалар), ҳисоблаш йўналиши бўйича (йиғинди олиш – тўғри ҳисобда ) тескари ҳисобни чиқариш ва реверсивлаш, ишлаш принципи бўйича (синхрон ва асинхрон) разрядли боғлиқликни амалга ошириш усули бўйича (кетма - кетлик билан параллел ва комбинацион кўчириш) каби гуруҳланади.

Ишни бажариш.

|

Синхрон ҳисоблагичларни моделлаштириш.

Импульслар миқдорини ҳисоблаш имконияти триггер қурилмасида генетикдек амалга оширулади Д триггер ўзи ишлаш принципи бўйича 2 модуль бўйича ҳисоблагич ҳисобланади. У икки ҳил ҳолатда пайдо бўлади ва 2 гача саналади: 0,1. шунга кўра энг содда, иккилик йиғинди олувчи ҳисоблагични кетме - кет ҳисобловчи Д - триггер занжирлари орқали амалга ошириш мумкин.

|

Моделлаштиришда амалга ошириладиган ишлар кетма - кетлиги

|

|

|

EWB да Sources гуруҳига кириб, доимий кучланиш манбаи +5В. (+Vss Voltage Sources) ни танлаймиз. |

|

|

EWB да Sources гуруҳига кириб, Ground ни танлаймиз. |

|

|

Кейин 2 та переключатель танлаймиз. |

|

|

Мантиқий индикаторни танлаймиз. |

|

|

Из меню Digital буксируем на рабочее поле. Д Flip-Flop >>> |

|

|

EWB да Instruments гуруҳига кириб, Word Generator ни танлаймиз.

|

|

|

Word Generator ни устига чап тугмачани 2 марта босамиз. |

|

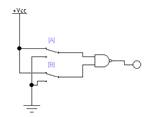

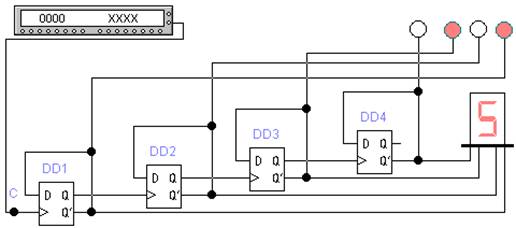

Бунга ўҳшаш ҳисоблагичлар тезкор кўчирувчи ёки асинҳрон режимда ишловчи ҳисоблагичлар деб номланади бунда бир - бири билан дарҳол уланган бир неча триггерлар ҳар бир импульсларга нисбатан кечикиш билан етиб келади. (Расм .13)

Қуйидагича схемаларни йиғинг:

Расм 13.Хисоблагич схемаси

Схемада ишлаш:

![]() тугмачани босиб

моделлашни ёқамиз.

тугмачани босиб

моделлашни ёқамиз.

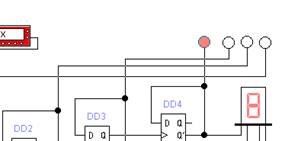

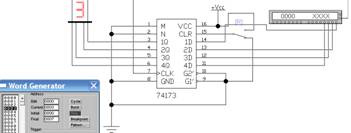

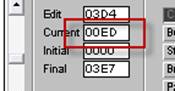

Вариант бўйича биз Word Generatorнинг чиқувчи 0100 сигналида, етти сегментли индикатор Y ни қийматини топишимиз керак;

|

· Генераторни очиб унда керакли созлашларни бажарамиз. |

|

|

Хисоб индикаторлари ишини кузатамиз.

|

|

|

Word Generatorнинг чиқувчи 0100 сигналида, етти сегментли индикатор Y ни қийматини аниқлаймиз. |

|

|

Анализ натижаси: Y=4 |

|

|

Барча иншоатларни Jpeg форматида сақланг ва ҳисоботингизга киритинг. |

|

Асинхрон ҳисоблагични моделлаштириш.

Ҳисоблагичларда кетма - кетлик билан тезкор маълумотларни кўчириш чекланган ҳисоблагич ичида маълумот вақтинча тутилиш билан кўчирилади. Такт импульслари билан келувчи ҳабар (информация ) керакли равишда юкланса, улар ҳисоблагичнинг барча триггерларида бир вақтда буйруқ бўйича синхрон силжитилади. Шунга кўра бу турдаги ҳисоблагичлар синхрон триггерлардан тузилган ва барча ҳисоблагичлардаги ушланиб қолиш битта триггердаги маълумот кечикиши орқали аниқланади. Лекин барча занжирдаги эмас ҳисоблагич структураларида триггер занжирлари схемотехник жиҳатдан маълумот сигналларини узатиш учун қўйилади, лекин унга яна қўшимча комбинацион мантиқий ҳам пайдо бўлади.

Синхрон ҳисоблагич схемаларида синхронлаштирувчи киришлар паралел уланади ва уларга кетма - кет такт импульслари бир вақтда берилади.

ДД1 триггерни чиқишидан кўчиб ДД2 триггерга киради. Кейинги разрядни ДД3 га кўчиришда ЛE ДД5 НАНД ташкил. Ҳисоблагични ишлаш натижаси 165б; 166б; расмда кўрсатилган графикда тасвирланган.

Синхрон иккилик – ўнлик ҳисоблагич схемаси 13 расмда кўрсатилган .

1010 сонига мос келувчи сигнал кириши вақтида ҳисоблагичга тушишини бошқариш учун бу ерда МE ДД7 туридаги 4та ИНПУТ НАНД, унинг 2 кириши ДД1 ва ДД4 триггерлари тўғри чиқишлари билан уланган ва 2 бошқа кириши ДД2 ва ДД3 тескари чиқишларига уланган. Ҳисоблаш кўриниши мантиқий анализатор экранида тасвирланган. (13 расм )

Синхрон ҳисоблагич бир тури бўлиб силжитувчи регистр базасида ишловчи ҳалқасимон ҳисоблагичлар ҳисобланади. Eнг содда ҳалқасимон ҳисоблагичларда регистрнинг тўғри чиқиши уни киришига туташтирилади.

Тўрт разрядли ҳисоблагич регистр учун биринчи тактда киришга берилган код бирлиги ҳисоблагич барча разрядларидан ўтади, кейин унинг киришига қайтадан 4 та такт берилади ва шу тартибда жараён такрорланади .

Бундай қурилмалар дастурли – вақт қурилмаларида белгиланган киришга улаб бериш учун кенг ҳолда қўлланилади.

|

Моделлаштиришда амалга ошириладиган ишлар кетма - кетлиги

|

|

|

Мантиқий индикаторни танлаймиз. |

|

|

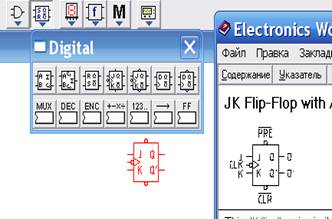

Из меню Digital буксируем на рабочее поле JK Flip-Flop >>>. |

|

|

EWB да Instruments гуруҳига кириб, Word Generator ни танлаймиз.

|

|

|

Из меню Indicators буксируем на рабочее поле Seven Segment Indicator. |

|

Қуйидаги схемани йиғамиз:

Йиғилган схема анализи:

![]() тугмасини босиб

моделлаштиришни ишга туширамиз.

тугмасини босиб

моделлаштиришни ишга туширамиз.

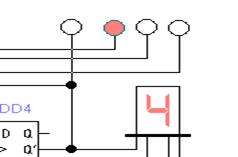

Вариантимиз бўйича биз Word Generatorнинг чиқувчи 0005 сигналида, етти сегментли индикатор Y ни қийматини топишимиз керак;

|

· Генераторни очиб унда керакли созлашларни бажарамиз. |

|

|

Ҳисоб индикаторлари ишини кузатамиз.

|

|

|

· Current эътиборимизни каратамиз. |

|

|

Word Generatorнинг чиқувчи 0005 сигналида, етти сегментли индикатор Y ни қийматини аниқлаймиз |

|

|

Анализ натижаси: Y=8 |

|

|

Барча иншоатларни Jpeg форматида сақланг ва ҳисоботингизга киритинг. |

|

Вариантлар

|

№ |

1-топшириқ Схемани моделлаштириш |

2-топшириқ Йиғилган схема анализи |

|

1 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

2 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

3 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 01E5 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

4 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 01E5 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

5 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

6 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

7 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

8 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

9 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

10 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

11 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

12 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

13 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 01E5 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

14 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 01E5 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

15 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

16 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

17 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

18 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

19 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

20 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

21 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

22 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

23 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чикувчи 01E5 сигналида, етти сегментли индикатор ни киймати Y=? |

|

24 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 01E5 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

25 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

26 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

27 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0A15 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

28 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

29 |

Синхрон ҳисоблагичларни моделлаштириш |

Word Generatorнинг чиқувчи 0B25 сигналида, етти сегментли индикатор ни қиймати Y=? |

|

30 |

Асинхрон ҳисоблагични моделлаштириш |

Word Generatorнинг чиқувчи 0105 сигналида, етти сегментли индикатор ни қиймати Y=? |

Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма - кетлиги.

· 1-топшириқ бажарилгандан кейинги натижалар.

· 2-топшириқ номи.

· 2-топшириқ бажарилиш кетма – кетлиги.

· 2-топшириқ бажарилгандан кейинги натижалар.

· Компютерда олинган моделлаштириш натижалари.

· EWB дастуридаги яратилган схемалар (web файллар).

· Иш бўйича ҳулоса.

№9 Амалий машғулот.

Регистрлар синтези. Регистрларни текшириш ва моделлаштириш.

Ишдан мақсад

EWB дастурида Регистр схемасини ўрганиш.

Назарий маълумот

Регистрлар рақамли электроникада ва техникада кўп разрядли иккилик кодли кўринишида берилган маълумотлар устида амаллар бажарувчи тугунлар ва қурилмалар қуришга ишлатилади бу операцияларга қуйидагилар киради: қабул қилгич, сақлаш, разряд бўйича суриш, разряд ости мантиқий операциялар ва рақамли сўзларни белгиланган кодга тақдим этиш. Регистрни битта функциясини ўзиёқ уни энг кенг тарқалган рақамли қурилмалар тугуни эканлигини кўрсатади.

Регистрлар триггерлар ва мантиқий элементлари бўлган схемалардан ташкил топади. Регистрларни узатиш линиясига қараб бир фазали ва пара фазали (икки фазали), синхронизация тузилишига қараб бир тактли ва 2 тактли ва кўп тактлига бўлиши мумкин. Аммо рефистрларни асосий классификацион белгиси албатта маълумотларни қабул қилиш ва кузатиш ҳисобланади. Бу йўналиш бўйича улар параллел (статик), кетма-кет, (сурулувчи) ва параллел кетма-кет регистрлар.

Ишни бажариш.

|

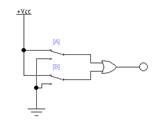

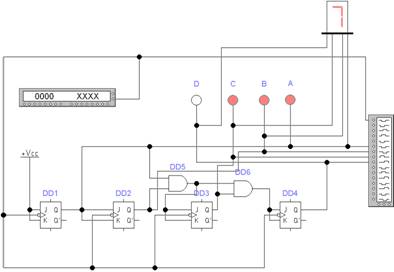

Параллел силжитиш регистрларини моделлаштириш

Параллел регистрларда маълумотлар разрядма разряд қабул қилинади ва узатилади. Тактли сигналларни сўзларини киритиш ва чиқаришда разряд сеткаси бўлиб сурилгани учун у сурувчи регистрлар деб аталади. Сурувчи регистр реверсивмас (битта юналишда сурулувчи) ва реверсив (иккита юналишда сурулувчи) бўлиши мумкин.

|

EWБ дастурида 4 разрядли параллел халқасимон силжитиш регистрини кўрамиз. Бунинг учун JK триггердан фойдаланамиз (146-расм). Бу схемани алоҳида томони АБCД параллел маълумотларни киритиш тескари алоқани амалга оширишдир: ДД4 триггерини Қ чиқиши ДД1 триггерини 1Ж киришига ва ДД4 триггерини Қъ чиқиши ДД1 триггерни 1К киришига уланади. (146-расм). |

|

|

Sources гурухига кириб, +5V (+Vcc Voltage Sources) доимий кучланиш манбасини танлаймиз |

|

|

«ер (ер билан туташтириш)» (программада уланган деб хисоблаймиз) |

|

|

Кейин икки переключателни (туташтиргич) танлаймиз |

|

|

Мантиқий индикаторни танлаймиз |

|

|

Бу менюдан Digital иш майдонига юналтирамиз JK Flip Fop >>> |

|

14 расм. Регистр схемаси

Схема устида ишлаш:

Моделлаштиришни учун бу

кнопка босилади. ![]()

Вариант бўйича бизга Y ни топиш керак булади, кириш сигналлари орқали A=1; B=0; C=1; D=0;

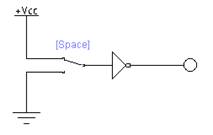

Манбани ёқилиши билан чиқишда 1111 комбинацияси пайдо бўлиши мумкин. Регистрни тозалаш (чиқишда 0000 ҳосил қилиш) R киришига мантиқий 0 бериш билан амалга оширилади. Маълуимотларни киритиш С инверс кириши орқали амалга оширилса киришларга қисқа вақтни мантиқий 0 ни берилиши натижасида, мос киришларга мантиқий 1 берилади (14-расм). [Спаcе] кнопкаси ёрдамида маълумотларни халқасимон айланишини бошловчи тактли импулсларни улаймиз. Тескари алоқа контурини узиш халқасимон регистрни оддий силжитувчи регистрга айлантириб қуяди.

|

Y ни топамиз , кириш сигналлари орқали A=1; B=0; C=1; D=0; биз: · А ни 1 га қуямиз. · B ни 0 га қуямиз. · C ни 1 га қуямиз. · B ни 0 га қуямиз.

|

|

|||

|

· R ни 1 га қуямиз

|

|

|||

|

Кириш сигналларини аниқлаймиз: Агар индиcатор ёқилса – 1 га тенг булади, акс ҳолда 0 га тенг булади. Индикатор сигналини иккиликка ўтказамиз. |

F = 1010 |

|||

|

Тахлил натижаси : F= 1010 |

||||

|

Барча сикриншотларни Jpeg форматда сақлаб ҳисоботингизга қушинг. |

||||

Вариантлар

|

№ |

1-топшириқ Схемани моделлаштириш |

2-топшириқ Йиғилган схема анализи |

|

1 |

Параллел силжитиш регистрларини моделлаштириш

Параллел силжитиш регистрларини моделлаштириш

|

A=1; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

2 |

A=0; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

3 |

A=1; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

4 |

A=1; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

5 |

A=1; B=1; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

6 |

A=0; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

7 |

A=1; B=0; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

8 |

A=1; B=1; C=0; D=0; кириш сигналлари орқали Y ни топиш |

|

|

9 |

A=1; B=0; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

10 |

A=0; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

11 |

A=0 B=1; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

12 |

A=1; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

13 |

A=0; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

14 |

A=1; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

15 |

A=1; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

16 |

A=1; B=1; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

17 |

A=0; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

18 |

A=1; B=0; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

19 |

A=1; B=1; C=0; D=0; кириш сигналлари орқали Y ни топиш |

|

|

20 |

A=1; B=0; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

21 |

A=0; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

22 |

A=0 B=1; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

23 |

A=1; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

24 |

A=0; B=1; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

25 |

A=1; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

26 |

A=1; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

27 |

A=1; B=1; C=1; D=0; кириш сигналлари орқали Y ни топиш |

|

|

28 |

A=0; B=0; C=1; D=1; кириш сигналлари орқали Y ни топиш |

|

|

29 |

A=1; B=0; C=0; D=1; кириш сигналлари орқали Y ни топиш |

|

|

30 |

A=1; B=1; C=0; D=0; кириш сигналлари орқали Y ни топиш |

|

|

31. |

A=1; B=1; C=0; D=1; кириш сигналлари орқали Y ни топиш |

Ҳисобот тузиш тартиби.

Ҳисобот қуйидагиларни ўз ичига олиши керак:

· Ишнинг номи.

· Ишдан мақсад.

· 1-топшириқ номи.

· 1-топшириқ бажарилиш кетма – кетлиги.

· 1-топшириқ бажарилгандан кейинги натижалар.

· 2-топшириқ номи.

· 2-топшириқ бажарилиш кетма - кетлиги.

· 2-топшириқ бажарилгандан кейинги натижалар.

· Компютерда олинган Моделлаштириш натижалари.

· EWB дастуридаги яратилган схемалар (web файллар).

· Иш бўйича ҳулоса.

Адабиётлар.

1. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш.шк., 1991, 526 с.

2. Угрюмов Е.П. Цифровая схемотехника. Учеб. пособие для вузов.ғ 2- изд.

перераб. и доп.-СПб. БХВ – Петербург. 2005.-800 с.:ил.

3. Калабеков Б.А. Цифровые устройства и микропроцессорные системы. Учебник.-М.:Горачая линия- Телеком.,2003 г.-336.

4. Суворов В.И., Юнусов Д.Ю. Методическое руководство по лабораторно-практическим занятиям по курсу «Основы цифровой техники и микропроцессоры» (№ 47). ТЭИС, 1984, 118 с.

5. Хокинс Г. Цифровая электроника для начинающих: Пер. с англ. М.: Мир, 1986, 232 с.

6. Гольденберг Л.М. и др. Цифровые устройства и микропроцессорные системы. Задачи и упражнения: Учеб. пособие для вузов. М.: Радио и связь, 1992, 256с.

7. Абдурахманов Р.П., Баширов Р.В., Амирсаидов У.Б. Задания к контрольной работе и методические указания к их выполнению по курсу «Цифровая и вычислительная техника». ТЭИС, 1995, 30 с.

8. Ж.Ю.Юнусов., Х.Ю.Аббосхонова Касб хунар колледжлари учун ўқув қўлланма

Тошкент «Иқтисод молия» 2010-215в

9. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. – М.: Высш.шк., 1991. – 526 с.

10. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ . – М.: Высш.шк., 1987. – 318 с.

11. Суворов В.И., Юнусов Д.Ю. Методическое руководство по лабораторно-практическим занятиям по курсу «Основы цифровой техники и микропроцессоры» (№ 47). – ТЭИС, 1984. – 118 с.

12. Гольденберг Л.М. Цифровые устройства и микропроцессорные системы.

Задачи и упражнения.: Учеб. Пособие для вузов. М.: Радио и связь, 1992.

13. Гольденберг Л.М. Цифровые устройства на интегральных схемах в связи.

М.: Радио и связь, 1979, 232 с.

14. Абдурахманов Р.П., Баширов Р.В., Амирсаидов У.Б. Задания к контрольной работе и методические указания к их выполнению по курсу «Цифровая и вычислительная техника». – ТЭИС, 1995. – 30 с.

16. Безуглов Д.А., Калиенко И.В. Цифровые устройства и микропроцессоры., Ростов-на-Дону, 2006 г.

17. Каган Б.М. Электронные вычислительные машины и системы. М. Энергоатомиздат, 1991.

МУНДАРИЖА

|

КИРИШ....................................................................................................... |

3 |

|

№1Амалий машғулот. Мантиқий элементларнинг оддий модели ва тизим параметрларнинг чиқиш қийматлари. Electronics Workbench (EWB) дастури билан танишиш........................................................... |

4 |

|

№2 Амалий машғулот.Комбинацион чизмаларнинг умумий базисдаги синтези................. |

17 |

|

№ 3 Амалий машғулот. Комбинацион дискрет автомат автоматларни «И–НЕ», «ИЛИ-НЕ» базисларида синтези. ВА-ЙЎҚ, ЁКИ-ЙЎҚ ва Шеффер–Пирс мантиқий қурилмасидаги инверторни синтез қилиш.............. |

27 |

|

№4 Амалий машғулот. Кўп тактли дискрет автоматларнинг синтези. (Триггерлар синтези).Триггерни моделлаштириш ва текшириш............................................................................................. |

34 |

|

№5,6 Амалий машғулот. Кўп тактли дискрет автоматларнинг синтези (Бир триггер асосида иккинчи триггер синтези. ТРИГГЕРЛАР ВАҚТ ДИАГРАММАСИ................................................................................... |

40 |

|

№7,8 Амалий машғулот. Ҳисоблагичлар синтези (Қўшувчи ва айрувчи хисоблагичлар). Ҳисоблагичлар синтези(Ихтиёрий тартибли хисоблагичлар) хисоблагичЛАРНИ МОДEЛЛАШТИРИШ ВА ТАДҚИҚ ЭТИШ........................................................................................................ |

49 |

|

№9 Амалий машғулот. Регистрлар синтези.,текшириш ва моделлаштириш....................... |

62 |

|

АДАБИЁТЛАР............................................................................................ |

71 |