ЎЗБЕКИСТОН РЕСПУБЛИКАСИ ОЛИЙ ВА ЎРТА

МАХСУС ТАЪЛИМ ВАЗИРЛИГИ

ТОШКЕНТ АХБОРОТ ТЕХНОЛОГИЯЛАРИ УНИВЕРСИТЕТИ

МУТваТ КАФЕДРАСИ

РАКАМЛИ ТЕХНИКА

фанидан маърузалар

Билим соҳаси 500 000 Мухандислик,ишлов бериш ва

курилиш тармоклари

Таълим йўналиши 5522200-“Телекоммуникация”

бакалаврият таълим йуналиши учун

Тошкент 2010

Фаннинг ўқув дастури Олий ва ўрта махсус,касб-ҳунар

таълими ўқув методик бирлашмалари фаолиятини мувофиқ-

лаштирувчи кенгашнинг 2010 йил “__”_____даги”___”-сон мажлис баёни билан маъқулланган.

Фаннинг ўқув дастури Тошкент ахборот технологиялари университетида ишлаб чиқилди

Тузувчилар:

Абдурахмонов Р.П.. - «Маълумот узатиш ва тармоклари ва тизимлари» кафедраси доценти,т.ф.н

Амирсаидов У.Б. - «Маълумот узатиш ва тармоклари ва тизимлари» кафедраси доценти,т.ф.н

Абасхонова Х.Ю. -« Маълумот узатиш ва тармоклари ва тизимлари» кафедраси катта ўқитувчи

МУНДАРИЖА

1. Рақамли техникада арифметик ва мантиқий амалларни бажарувчи қурилмани қуриш принциплари.

2. Рақамли техникада бошқариш қурилмаларнинг қуриш асослари. бошқариш қурилмаларни мантиқий схемалар ва микродастурлаш асосида қуриш ва лойхалаш (ЭХМнинг) умумий схема стрктуралари... ЭҲМ архитектураси ЭҲМнинг асосий қисимлари.

3. Микропроцессорлар, микропроцессорли тизимлар ва микро ЭХМнинг структура схемаси. МП асосий қисмлари. Маълумотларни шиналар орқали узатишни ташкил этиш

4. МП буйруқлар тизими. буйруқ, дастур, буйруқ формалари, операция коди, буйруқларни адреслаш, буйруқ турлари буйруқлар тизими тушунчалари.

5. Ассембрлаш. хисоблаш машиналари тизимига асосланган ассемблер-тили. Машина кодлари асосида ассемблер тилида тўгри чизиқли дастурлар тузиш. бир кристаллик аниқ тизимли.

6. Ассембрлер дастурлаш тилида массифлар билан ишлаш асослари ва дастурлаш жараёнлари.

7. Маълумотлар алмашиш усуллари. МП ва хотира ўртасида маълумотлар алмашиш усуллари.

8. Микро ЭХМ ва МП тизимларини ташкил этиш жараёнлари.

9. Интерфейс микросхемалари. ГТИ, буфер ригистрлар шина ташкил этувчилар.

10. Маълумотларни киритиш чиқаришни ташкил этиш. Параллел интерфейсни ташкил этиш.Умумий ва алохида шинали интерфейс тизимлари.

11. Маълумотларни ташқи қурилмаларга чиқариш интефейсларни ташктл қилиш. Маълумотларни ташқи қурилмаларга параллел узатиш режимига мослаштирувчи интерфейсни созлаш асослари.

12. МП комплекслари улар хақида тушинча. ишлаб чиқарилаётган замонавий МПК ва уларнинг қўлланилиши.

13. МК структураси. Хотира ва ташқи қурилмалар билан бошқариш жараёнларини ташкил этиш.

14. Сигнал процессорлари.

15. Микропроцессор тизимларини алоқа ва бошқариш қурилмаларида қўлланилиш жараёнлари.

16. Рақамли техникада микропроцессор тизимлари асосида қурилмаларни лойхалашнинг асосий этаплари. Талабларни баён этиш ва уни танлаш алгоритми билан боғлаш. Элемент базасини танлаш. Қурилма-структурасини ишлаб чиқиш.

1-маъруза.

Рақамли техникада арифметик ва мантиқий амалларни бажарувчи қурилмани қуриш принциплари.

АМК процессорнинг асосий элементларидан бири хисобланади. АМК 2-кисмдан иборат:

1.Сумматор

2.Логик амалларни бажарувчи курилма

Сумматор арифметик амалларни бажаради.Сумматорнинг нечта киришдан иборат булиши билан куйидаги турларга булинади:

А)Ярим сумматор(2-та кириши бор).

В)Бир разрядли сумматор(3-та кириши бор)

С) Куп разрядли сумматор( киришлар сони куп)

Сумматорларни санок системасида ишлатиш буйича 2-турга булинади.

1.2-лик Сумматор

2.Декадли Сумматор

Утиш разрядни узатиш услуби буйича сумматорлар 2 га булинади.

А)Кетма-кет узатиш

В)Паралел узатиш

Ярим сумматор ва унинг ишлаш таблицаси.

|

аi |

вi |

Si |

Рi |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Si= аi+ вi бу ерда

Аi –1-чи кушилувчи , Вi-2 чи -кушилувчи, Si-суммаси, Рi-утиш разряди.

![]()

![]() Si= аi вi + аi вi

Рi= аi вi

Si= аi вi + аi вi

Рi= аi вi

аi вi ![]()

|

|

|||||||

|

||||||||

|

![]()

![]()

![]() Si

Si

|

|||||||

|

|||||||

Рi

![]()

![]()

![]()

Бир разрядли сумматорнинг ишлаш таблицаси.

Бир разрядли сумматорда кушиш амалидан олдини утиш разряди хисобга олинади.

Кириш чикиш

|

№ |

аi |

вi |

Рi-1 |

Si |

Рi |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

2 |

0 |

1 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

1 |

0 |

|

5 |

1 |

0 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

0 |

1 |

|

7 |

1 |

1 |

1 |

1 |

1 |

Si= аi вi + Рi-1 Вi Карно Карта

Рi-1

![]()

![]()

|

0 |

1 |

0 |

1 |

|

|

0 |

1 |

0 |

аi

![]()

![]()

![]()

![]() Si= Рi-1

*аi * вi + Рi-1 *аi * вi+ Рi-1 *аi *

вi+ Рi-1 *аi * вi

Si= Рi-1

*аi * вi + Рi-1 *аi * вi+ Рi-1 *аi *

вi+ Рi-1 *аi * вi

Карно картаси.

Вi

Рi-1

![]()

|

|

0 |

1 |

0 |

|

|

1 |

1 |

1 |

аi

2 1 3

Рi= Рi-1*вi + Рi-1 аi +аi*вi

аi вi Рi-1

|

![]()

![]() Si

Si

![]()

![]()

![]()

![]() аi

вi Рi-1

аi

вi Рi-1

|

![]() Рi

Рi

![]()

![]()

Ярим сумматорнинг схемаси.

|

2-та ярим сумматорни куйидагича улаб сумматорни тузиш мумкин.

Si

S Р А В S Р HS А В

Аi

вi

|

|

||||

1![]()

Рi

![]()

![]()

![]() Рi-1

Рi-1

Cумматорни бир бири билан боглаб,куп разрядли сумматорларни тузиш мумкин.

Мисол: 4-разрядли сумматор схемаси куйидагича.

![]()

![]()

![]()

![]()

А В р SM 2 S Р А В р S Р SM 3 S Р SM 1 А В р S Р А В Рi- SM 0

А0

А1 А2 А3

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Р1 р2 р3

Ушбу схема утказиш разрядлари (Р) кетма-кет узатилади.Агар разрядлар сони катта булса,утиш вакти ошиб кетади ва сумматорнинг ишлаш тезлиги камаяди.Шунинг учун утиш вактини камайтириш учун турли усуллар кулланилади.Ушбу усулларда утиш разрядлари паралел холда узатилади.Шунинг учун утиш вакти разрядлар сонига боглик эмас.Кетма-кет утишнинг асосий камчилиги шуки жуда куп киришли комбинацион схемаларни тузишга тугри келади.Шунинг учун ушбу усулни разрядлар сони катта булмаган сумматорлар учун ишлатиш мумкин.

Декадли сумматор.

Декадли сумматорлар –лик сонининг хар бир разряди алохида 2-лик куринишида тасвирланади.Мисол учун: 345

0011 0100 0101

3 4 5

2-лик арифметикасида хар бир 10-лик разряднинг 2-ликдаги куриниши «ТЕТРАД»дейилади. Декадли сумматорда тетраднинг киймати 9-дан ошса унда тетраднинг кийматини 10-тага камайтириш керак.

Декадли сумматорнинг схемаси.

S0

S0 S1 S2 А0 В0 А1 В1 А2 В2 Р SM S0 S1 S2 S3 Рi А0 В0 А1 В1 А2 В2 А3 В3 SM![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() S1

S1

![]()

![]() S2

S2

|

![]() «0”

«0”

|

|||

|

|||

![]()

![]()

![]()

![]() Рi

Рi

Логик курилма.

Куйидаги мантикий амалларни бажарувчи курилмани тузиш.

1)ИЛИ F=аVв

2)И F=а^в

![]()

![]() 3)ИЛИ-НЕ F=а+в

3)ИЛИ-НЕ F=а+в

4)И-НЕ F=а*в

|

S1 |

S0 |

№ |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

2 |

|

1 |

1 |

3 |

Ушбу логик курилманинг схемаси.

& 1 & 1 0 1 2 3 S0 S1 MC![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

ИЛИ а

в

И

F

ИЛИ-НЕ

ИЛИ-НЕ

И-НЕ

S0

S1

Тузилган арифметик ва логик курилмаларни бирлаштириб арифметик логик курилма хосил киламиз.(АЛК).Амалларни бир-биридан фарклаш учун яна битта бошкарув сигналини киритамиз.

Арифметик амал бажариш.

![]()

![]() М

М

Логик амални бажариш.

Ушбу амални бажариш учун 2-та кириш мулътплексоридан фойдалинамиз,ушбу холда АЛК схемаси куйидагича булади.

ЛК

АК

0

1

S

MC

А

S

|

ЛК |

|

АК |

|

0

1

S |

|

MC |

![]()

![]()

![]()

![]() в

в

|

F

F

|

|||

М

Бажариладиган амал сони ошиши билан бошкарув сигналлари элементлари сони ошиб боради.1-чиккан протцессорларда факат оддий арифметик амал бажарилган.Купайтириш ва булиш амаллари булмаган.Ушбу амалларни дастур тузиш йули билан бажарилган.Шунинг учун протцессор бир неча 10.000 транзисторлардан ташкил топган.Хозир протцессорларда барча арифметик логик амаллар аппарат усулида бажарилади,транзисторларни сони бир неча 1.000.000 ни ташкил этади.

![]() 2-лик модулида кушувчи логик элемент.

2-лик модулида кушувчи логик элемент.

1)У=Х1 Х2

|

Х2 |

Х1 |

У |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

У=Х1* Х2 + Х1*Х2= Х1 Х2

У=Х1* Х2 + Х1*Х2= Х1 Х2

М2

Х1

У

У

Х2

Х2

2)Эквивалентли логик схема тнг булмаганда “0”га,тенг булганда “1”га тенг.

У=Х1* Х2 + Х1*Х2= Х1

У=Х1* Х2 + Х1*Х2= Х1

|

Х2 |

Х1 |

У |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

![]() Инвертор.

Инвертор.

А) У=Х

НЕ

1 1

Х

Y

Y

|

|

У=Х |

|

0 |

1 |

|

1 |

0 |

В) У=Х1+Х2=Х1VХ2

X1

Y

X1

Y

ИЛИ

ИЛИ

X2

|

Х1 |

Х2 |

У |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

С) У=Х1*Х2=Х1^Х2

X1

![]()

&

![]() X2 И

X2 И

|

Х1 |

Х2 |

У |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

![]()

![]()

![]() Г) У=Х1+Х2 = Х1VХ2 =Х1 Х2

Г) У=Х1+Х2 = Х1VХ2 =Х1 Х2

ИЛИ-НЕ

1

Х1

|

1 |

![]()

![]()

X2

X2

|

Х1 |

Х2 |

У |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

![]()

Д) ) У=Х1*Х2 = Х1^Х2 =Х1 / Х2

И-НЕ

&

Х1

|

& |

![]()

![]()

![]()

![]()

X2 У

|

Х1 |

Х2 |

У |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

![]() Е)

У=Х1 Х2

Е)

У=Х1 Х2

М2

Х1

|

М2 |

![]()

![]()

X2

X2

|

Х1 |

Х2 |

У |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

=

X1

![]() Y

Y

![]()

![]() X2

X2

![]()

![]()

![]()

![]() Д)

) У=Х1 Х2

Д)

) У=Х1 Х2

|

Х1 |

Х2 |

У |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

2-маъруза.

Рақамли техникада бошқариш қурилмаларнинг қуриш асослари. бошқариш қурилмаларни мантиқий схемалар ва микродастурлаш асосида қуриш ва лойхалаш (ЭХМнинг) умумий схема структуралари... ЭҲМ архитектураси ЭҲМнинг асосий қисимлари.

Хотира курилмаси ички ва ташки булиши мумкин.Ташки хотира деб магнит ёки оптик дискларида ва ленталаридаги хотирага айтилади. Ички хотира асосан микросхемаларда бажарилади.Ички ва асосий хотиралар икки типга булинади. Аператив хотира курилмаси. (ОХ+). Ёки ихтиёрий танланган Х+ (ИТХ+) ва доимий Х+(ДХ+).ОХ+ бундан ташкари RAM (Random Access Memory), ДХ+ эса ROM (Rеаd Only Memory ) деб хам белгиланади. Узида хам ОХ+ Хам ДХ+ хусусиятларини олган хотира. Флеш (Flash ) ва манбага боглик булмаган хотира NV (Nonvolative)лар хам кенг таркалган.Охирги ном шартли чунки ДХ+ ва Флеш хотира хам манбага боглик булмаган хотиралардир. ОХ+да кодлар бажарилаётган вазифаларга караб доим узгариб туради ва манба учирилиши билан бутунлай йуколади. ДХ+ да ЭХМ ишини бошкарадиган стандарт дастурлар, константалар, белгилар жадвали ва бошка ахборотлар сакланади ва улар камьютер учирилганда хам сакланиб колади.ОХ+ статик (SRAM), динамик (DRAM) регистрли (RG) хотирага булинади. ДХ+: никобли- ишлаб чикарувчи завод томонидан дастурланган (ROM), истеъмолчи томонидан бир бора дастурланадиган (PROM ёки ОТР), истеъмолчи томонидан кун бора дастурланадиган ва ультра бинафша нур билан учириладиган (EPROM)` ёки электр билан учириладиган (ЕЕPROM, Flash) булиши мумкун. Бундан ташкари истеьмолчига бир кристалда мантикий элементлар ва курилмаларнинг барчасини уз ичига олган дастурланадиган матрицалар ва курилмалар (РLM,PML, PLA,PAL,PLD,FPGA ва х.к.) чикарилган. Х+ типига боглик равишда хотира элементи (ХЭ) триггер, конденсатор,”Сузувчи затворли” транзисторлар, мурт уланиш (ёки унинг йуклиги) булиши мумкин. ХЭларнинг тартибли тизими хотира ячейкасини (ха) пайдо килади. ХЯда ХЭлар сони (суз узунлиги) 2n (1,2,4,8,6,32,64...)га тенг булиб, бу курсатгич 8дан ошгач ХЭларини гурухлаш амалга оширилади. ХЯ даги ХЭ ларининг сони суз узунлиги дейилади. Хотира микросхемаларнинг асосий тавсифлари информацион сигим, тезлик, кувват истемолчидир. Х+ сигими кушимча 210=1024=1k га тенглаштирилади. Бу бирлик битга тенг булган суз узунлиги учун килабит (Кв), байтга (8битга) тенг булган суз узунлиги учун килобайт (КВ) дейилади.

Хар бир иккининг “п” даражали хотира ячейкасига ХЯ нинг адреси деб айналиши «п» да режал иккилик сон тугри келади. Масалан, 511- хотира ячейкасининг адреси 11111 1111 (ВIN)-511(DEK)-1 F F (AEХ) булади. Дастурларда адреслар 16-лик форматда берилади. Х+ сигими купинча 2 n*m куринишида берилади, бундан 2 n-хотира ячейкалари сони, m-эса ячейка суз узурлиги. Масалан,8к*8 (м с 537 РУ17), яъни 8192 –бит ячейка улчамини билдиради.Ленин баъзи манбаларда бу микросхема 64 к бит деб берилади.Ушбу сигимни 16к*4, 64*1,32*2 куринишида ташкиллаштирилган микросхемаларда хам учратиш мумкун.

Статик типдаги ОХК.

Хотира элементи сифатида оддий Д-триггер ишлатилади. Бу микросхемада (537 РУ10) хар бир ХЯ саккиз триггердан тузилган булиб, улар кристаллда тугри бурчакли матрица куринишида танланади.

Расмда келтирилган белгилар: n-та адрес киришлари(А О...А n), DIO-икки томонли саккиз даражали маълумотлар шина С,S-микросхема танлаш кириш(бош=ача белгиси WR RD, яъни, сигналнинг юкори курсаткичида киришда байтни укиш руй беради.), ЕО,DI ,WR- бошкарув блоки чикараётган укиш ёзиш саклаш ички сигналлари. Ихтиёрий ХR:га уланиш иккита оддий дешифратордан йигилган тугри бурчакли дешифратор ёрдамида бажарилади,шифратор ёрдамида бажарилади, бунда К-адрес йуллари ДС ц устунлар дешифраторига киритилади, колган n-k Йуллар ДС с сатрлар дешифраторига киритилган.Бундан чикди, устунлар ва сатрлар сони плюс равишда 2 к ва 2 н-к га тенг булади,яъни хизмат курсатилаётган ХЯ ларининг умумий сони 2 к* 2 n-к -2 n га тенг.

Куйидаги расмда микросхемаларнинг асосий ишчи холатларини назорат килишимиз мумкун булганини куришимиз мумкун. Шу ерда микросхеманинг шартли белгилари хам берилади.

Чизмада берилган ОК ва Z белгилари мос равишда очик каллектор ва учинчи холатлари билдиради. Нукталар билан L -чи ХЯ нииг саккизта элементидан бири (J-чи) курсатилган .Lракамли :ВА: чизмаси (r* 2 к* с) r-ракамли сатр ва с-ракамли устунга эга булган матрицада курилган, 2 n чикиш тузининг бири булган тугрибурчакли дешифратордир (с) hiр (S) еlеct- СS инвер кириши учрайдиган барча микросхемаларда чизмани ишчи холатга ушбу киришга сигналнинг паст катламини бериш йули билан келтиришга хизмат килади.

Агар –СS-1(пассив катлами)булса микрасхема танланмаган ва у билан амаллар бажариш мумкун эмас.Расмдан куриниб турибдики, бу холда Д-триггернинг L-киришида-ноль, ёзиш мумкун эмас, тригер аввалги ёзилган битни саклаб колади. Чикиш коди Q ни укиш хам мумкун эмас, чунки чикишни рухсат этувчи ЕО тугри чикишда таъкикловчи ноль сигналли ва DIO: киришининг чикиши учинчи холатдадир.

NCS-O булиши билан ЁКИ-ЭМАС чизмаси ишга тушади ва шу пайтдан бошлаб бутун чизма иши –WE ва –ОЕ чизмаларга боглик булади.

Ёзиш холатида –WE-O га тенг. Шунинг учун киришдаги - ОЕ сигналининг кийматидан катъий назар,Еоички сигнал хам О га - тенг, ва маълумотларни укиш мумкун эмас. Ва : элементининг юкори чикишида-бир булса ва адресли киришларда код А n-1, А n -2, ..., А I,А О (ВIN)-L (DEC) булса, у холда Y r ва Y c йулларда сигнал хам 1 га тенг ,ва LJ триггер DIIJ кириш ахборатни ёзиш учун очик.

- Укиш холатида WE-1, -ОЕ-О ва Y r-Y c-1 былиб, -Q чикши сигнал В а L J элементида инверсиялангандан сунг DIO: чикишига утади. Шунга алохида эътибор каратиш лозимки, барча 2 n i-чи хотира элемертлари DIO j-чикишига уланиши лозим

- Бундай уланишига чизмали ёки пайвандли Ва (ЁКи) йули билан эришиш мумкуин. Пайвандли Ва (Ёки) уланиш кушимча чизма талаб килмайди ва очик коллекторли ёки учинчи холатли элементларда бажарилиши мумкун. Курилаётган чизма ХЭ ларнинг j-чи чикишлари Rj умумий резисторида бирлашган, бу резистор очик коллекторли Ва-ЭМАС L j элементи учун юклама булиб хизмат килади. Ахборот сигимини ошириш максадида, алохида микросхемалар банкларга гурухланади ва уларнинг чикишлари бирлаштирилиши лозим

Шу боисдан хотира микросхемаларининг барча киришлари хам очик коллекторли ёки учинчи холатли килиб бажарилади.

- ЭХМ ларда статик ОХК тезкор Саsh-хотирада ишлатилади.

Динамик типдаги ОХК.

- Хотира элементи сифатида улчаши статик хотирали Д-триггеридан анча кичик булган интеграл бажарилган микроканденсатор ишлатилади.Шу боисдан кристаллнинг бир хил улчамида бажарилган DRAМ ахборот сигими SRAМ га караганда анча юкоридир. Ахборот кириши ва хажми ошишига йул куймаслик учун микросхема ичидаги адрес йуллари икки гурухга булинади , Масалан юкори ва пастки булаклар.Икки хил К-йуллари «1 да 2» ички К-демизлтиплексорининг икки чишига уланади , унинг киришлари эса микросхеманинг К-адресли киришига уланади . Бунда адрес киришлари сони икки баравар камаяди , лекин микросхемага адресни узатиш ; - Биринчидан, узатиш икки былиб бажарилгани учун, иккинчидан кушимча ташки адрес мултиплексари ишлатилгани учун секинлашади. Бит саклаш жараёнида канденсатор кувватсизланади. Бунга йул куймаслик учун кувватни саклаб туриш керак.

Динамик ОХК статик ОХКдан фарки: - 1) адрес киришини мултиплекслаш билан - 2) сакланаётган ахборотни регенерациялаш лозимлиги билан - 3) ортирилган сигими билан (бир неча мбит гача) - 4) бир мунча кийин бошкарув чизмаси билан. - Куйидаги расмда сигими 256К*1 (2*18К) булган 565 РУ7 м/с шартли белгиси ва 9-та “1 да 2” мультиплексори ёрдамида 9 адрес киришларини 18та адрес йулига улаш усули берилган. - (расмда мисол килиб 1533 КП16 типдаги учта турга булинган селектор-мультиплексор олинган)

Хотира элементлари кристалда 512*512=2*9 * 2*9, матрицаси куринишида жойлашган булиб, у хар бири 9 адресли киришга эга сатр ва устун чизикли дешифраторлари ёрдамида бошкарилади. Агар –R/C сатр ва устун сигнали (S-мультиплексорини танлаш киришда) нолга тенг булса у холда А(О. . . 8)=Y(О. . . 8)га тенг ва микросхемага сатр адреси узатилади. Бу адрес –RAS сатр адреси стройининг манфий фронти билан кайт этилади. –R/S=1да мультиплексор чикишига устун адреси А(9. . . 17) узатилади, у эса уз вактида –САS устун адреси стройининг манфий фронти билан ёпилади. –WE кириши ёзиш укишни бошкаради. Персонал ЭХМ аператив хотираси –(SIMM,EDO,SDRAM)лар динамик хотирага талуклидурлар. Уларга мурожаат килиш вакти 10 нс дан кам булиб, сигими 1 корпусда 256М гача етади.

Репрограммаланадиган ДХК.

РДХК микросхемалари истемолчининг иш жойида юз минггача рапрограммаланадиган куп марталик м/с лар турига киради. Бу хусусият “сузувчи затворли” МОП транзисторларида ХЭ ларни куриш билан амалга оширилади.”Сузувчи затвор” изоляциясининг эни 200 ангстремга тенг. Агар ХЭ нинг барча чикишларида сигналнинг юкори катлами булса ахборот учирилган хисобланади. Дастурлашда берилган адрес шинаси буйича танланган, ноль ёзиш керак булган ХЭ га импульс юборилади. Учириш эса ультробинафша (EPROM) нурланиш билан ёки электр нури билан (ЕЕРRОМ)бажарилади

Бунда барча ячейкалар «1» холатга утади. Ёзилган ахборот бир неча йил сакланади . Бу типдаги М С ларининг бири ЕРRОМ 573 РФ 2 былиб , у тристабил (2 к*8) чикишига эга, Flash-хотирада изоляция эни 100 ангстремга тенг ва кайта дастурлашда туннел эфекти кулланилади.

Бир бора кайта дастурланадиган ДХК(РОRМ,ОТР)

Хотира элементлари сифатида ток импулслари билан куйдириладиган мурт туташувлардан фойдаланилади. Куйидаги расмда ДХК (РRОМ) чизмаси келтирилган

Адрес сигналининг хар бир киймати учун «L» дешифраторининг хеч булмаса битта чикишида Y L-1,колганларида ноль булади. J-транзисторининг бази киймати факат ti туташув бор ёки йуклигига бокликдир.Агар туташув булса (t;-1), ва базада сигналнинг юкори киймати булган холда транзистор очик, чикиш сигнали Doj-O.Агар туташув йук (ti- О) булса, Doj-1 тенг ушбу туташувларни эритиш йули билан барча j-битли адрес М С ларга :ВА ЁКИ: маълумотлар ёзилади. - Yi-miдешифраттор чикши сигнали, унда m i-AO...А n-1 кириш узгарувчиларининг минтерми.:Тугунли: транзисторлар. - ЁКИ-ЭМАС ролини бажаради, шунинг учун - 2 n-1 - -Doi-ЁКИ (ti*mi), бу ерда mi-Ва (IAк) - i-о к-0

2^n-1 n-1 ~DOi =ИЛИ(fi * mi), где mi = И(/Ak). i=0 k=0

- у холда !Ак—А к,-1.Бу формулалар МНДФ (12) формулаларга мос келади, шунинг учун n-адресли кириш,m-чикишли ДХК ёрдамида n-узгарувчили (сигналнинг инверсиясини чикши каскадида кузда тушган холда) ихтиёрий m-мантикий функцияни амалга ошириш мумкун .

Манбага боглик булмаган хотира (NVSRAM)

Маълумотларни манбаси учирилгандан кейин хам саклайдиган барча хотирани : манбага боглик булмаган (Non Volftile Memory) деб хисоблаш мумкун, бирок бу ибора факат статик аператив хотиранинг ушбу турлари учун тасдик топган:

· Ичига урнатилган катта хажмли литий батарейкали микросхемалар учун:

· Шу кристаллда жойлашган кушимча ЕЕРROM учун, бинобарин, SRAM ва EEPROM уртасида маълумот алмашиниш дастурий ёки кучланиш пасайган тикланган пайтда автоматик тарзда юз беради.

Хотира ячейкаси (суз) даражасининг ортиши.

Агар n- бит улчамли маълумотни саклаш керак булса ва хотира ячейкасининг суз узунлигининг оширилишига харакат килинади. Бу n!m-микросхемаларининг гурухларга булиш йули билан амалга оширилади, бунда ахборот киришларидан ташкари барча ухшаш киришлар бирлаштирилади. Масалан,агар 256 к сигимга тенг динамик хотира ва суз узунлиги байтга тенг хотира талаб килинса,у холда 8!1-8 пга 565 РУ 7 типли микросхемани куйдаги расмдагидек бирлаштирилади:

Расмда туккизта адрес йуллари шиналар куринишида, яъни функционал хоссалар буйича бирлаштирилган гурухлар куринишида берилган.

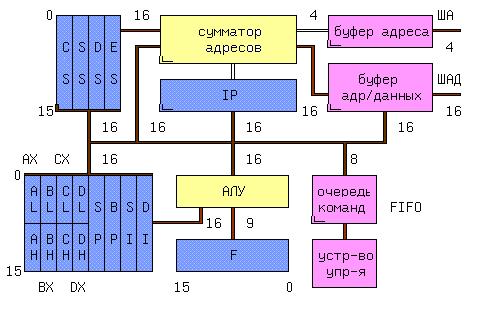

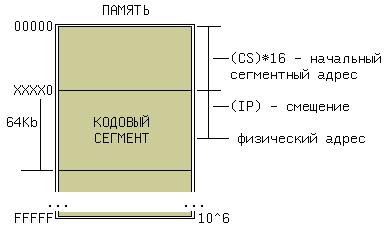

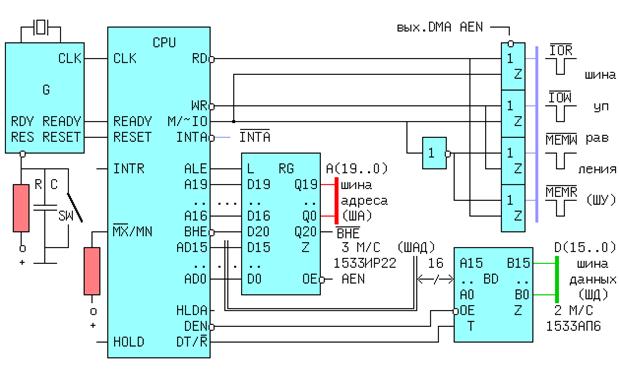

3-маъруза

Микропроцессорлар, микропроцессорли тизимлар ва микро ЭХМнинг структура схемаси. МП асосий қисмлари. Маълумотларни шиналар орқали узатишни ташкил этиш.

Агар n- бит улчамли маълумотни саклаш керак булса ва хотира ячейкасининг суз узунлигининг оширилишига харакат килинади. Бу n!m-микросхемаларининг гурухларга булиш йули билан амалга оширилади, бунда ахборот киришларидан ташкари барча ухшаш киришлар бирлаштирилади. Масалан,агар 256 к сигимга тенг динамик хотира ва суз узунлиги байтга тенг хотира талаб килинса,у холда 8!1-8 пга 565 РУ 7 типли микросхемани куйдаги расмдагидек бирлаштирилади:

Расмда туккизта адрес йуллари шиналар куринишида, яъни функционал хоссалар буйича бирлаштирилган гурухлар куринишида берилган.

Хотира ячейкаси сонларини ошириш

Х К адрес майдонини 2 к баровар ошириш учун, мавжут А n –к –1,. . .А n-оj Аn-1, Аn-2. . .А 1, АО.»n» йулларига « К» кушимча йулларини улаш билан бажарилади. Аn-к-1. . .Аn-о кушимча адрес майдонини хар бир длохида берилган М! Снинг хотира хажми ичидаги 2 к бир бирини копламайдиган интерволга булади. Бу масалани ечиш учун 2 к да К кушимча дешифратор талаб килинади. Масалан, хажми 2 к*4 булган ДХК блоки керак булса ,S41 РТI типли 256*4 хажмли 8-та микросхема ва : 8 да 3 : дешифратори куйидаги расмда курсатилганидек уланади .

Очик коллекторли микросхеманинг бир хил j-чикишлари умумий Rj юкланиш резистори билан уланган. Адреснинг учта юкори кушимча А 10, А9, А8 битлари 8 микросхемадан бирини танлайди, адреснинг 8-та кичик битлари 256 та хотира ячейкасидан бирининг таркибини маълумотлар шинасига чикаради. Дейлик, адрес шинасига (АШ) АIО... АО- 11000011010-61 код келиб тушади. Дешифраторнинг олтинчи (А 10 А 8 –110-6) чикишидан бошка барча чикишларида юкори сатх кузатилади.Нолъ сатхи –Y6-0, яъни олтинчи м!с нинг –ОЕI киришдаги нолъ ёзилган ахборотни чикишга утишига рухсат беради, А7 АО адрес киришларидаги 11010-IA (НЕХ)-26(ДЕС)коди 26-ХЯ таркибни турттала шинасига жойлаштиради .

Ушбу метиднинг хусусияти М!С ухшаш чикишларини ЁКИ (Ва) буйича бирлаштириш лозимлигидадир Бунга ухшаш чикишларни хар бир даража учун 2 n киришли ЁКИ (Ва) чизмасига улаш билан ёки очик коллекторли ёкиучинчи холатли ЁКИ(ВА) Чизма буйича хотира М!С ларининг чикиш структураларини бажариш билан эришиш мумкин (иккинчиси максадга мувофикрокдир) Шу боисдан барча хотира М!С лари шундай чикишли килиб бажарилади.

Дастурланадиган ракамли интеграл чизмалар

Замонавий ракамли курилмаларни лойхалаштириш дастурланадиган ракамли интеграл чизмаларсиз (ДРИУ)мумкин эмас Улар дискрет элементларидан куйидагилар билан устун туради. 1). Курилма улчамларининг кичиклиги билан , 2). Тезлигининг ортгани билан, 3). Мустахкамлиги билан, 4) Ишлаб чикиш натижаларининг кучириб олинишидан химояси билан, 5). Лоиханинг ишлаб чикилиши ва модификациялашининг мисли куйилмаган тезлиги. 6). Курилманинг ишлаб чикилиши ва модификациялашини истеъмолчи иш урнида бажарилиши мумкинлиги билан.

Куичилик ДРИЧ ларнинг чизма хусусиятлари ВА, ЁКИ,ЁКИ-ЭМАС,ва инвертор каби элементлар ёрдамида амалга оширилган нормал дизълонктив форма (НДФ) да муомалага киритилади. ДРИЧ таркибига триггерлар, мултиплексорлар,буфер канфигурациялар (тыгри, инверсли,тристабил )ва дастурланадиган симлар Истеъмолчи томонидан ишлаб чикилган чизманинг истеъмол хусусиятлари, шундай килиб, ишлаб чикувчи(истеъмолчи)нинг чизма хусусиятларидан келиб чиккан холда заводда амалга оширилган каттик тапологияга асосланади. ДРИЧ асосини ВА ЁКИ матрицалар ва триггер, киришнинг чикиш буферлари, бошкариш элементлари ва тескари алокаларни уз ичига оладиган макроячейкалар йигиндиси ташкил этади. ДРИЧ нинг йириклаштирилган структура чизмаси куйидаги расмда берилган:

«ВА матрицасининг « ВА элементи киришини (ГОСТ быйича эмас) куйида гапда берилгандек белгилаш кабул килинган. Уртада Гост буйича.

Дастурланмаган холда симлар жойидалигича колади.Программатор ёрдамида олиб тамилаш йули билан (унгдаги расмда Х белгиси) кириш узгарувчиларининг ихтиёрий купайтмасини (терм) олиш мумкин.Расмда ХI йулидан «ВА киришига келган сим олиб ташланган.Оддий холларда »ВА матрицаси киришига узгарувчиларнинг нафакат тугри, балки инверсия киймати хам киритилади. » ВА матрицаси чикиши ДНФ да кузда тутилгандек « ЁКИ элементларига уланади.Куйидаги расмни диккат билан урганиб чикинг, айникса уланишли ва уланишсиз туташувларга алохида эътибор беринг.

«ЁКИ элементининг чикиши бошкарувчи инверторнинг кайтаргич оркали биринчидан триггер киришига, иккинчидан MUХ1 мултиплексор ва бошкарувчи тристабил буфер оркали чикишга уланган.

Агар буфер Е сигнали ёрдамида учинчи холатга утказилган былса, М!С нинг « ташки киришнинг чикиши» кириш булиб хизмат килиш мумкин. MИХГ оркали, шунингдек триггер чикишидан тескари алока сигнали киритилиши мумкин.F (use)1 ва F(use)2 дан сигналлар хар бир МUХнинг ягона чикишини иккидан бир киришига улашни таъминлайдиган «2- 1» мултиплексорларнинг бошкарувчи киришларига келиб тушади. ДРИН ни конкрет вазифа учун дастурлаш САПР бошкаруви ёрдамида симларни куп маротаба конфигурациялаш имконини беради.

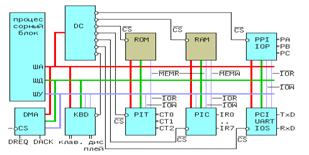

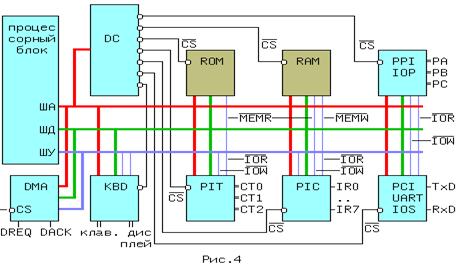

ПБга уланувчи барча курилмалар ишини DС дешифратор бошкаради ва унинг киришларига АШ нинг линиялари уланади. Одатда Дешифраторлар бир неча булади.Агар хотира ва ТК учун адрес сохаси тула ишлатмаса дешифраторга адрес линияларини барчаси унаниши шарт эмас, куп холарда АШ нинг катта разрядларини бир нечасини уланади. Масалан, агар ДС 4 линия А-19...А-18 уланса, у холда адрес соха 2*20/2*4=64 кб копланмайдиган блокларга булинади ва уларнинг хар бирига шиналарга уланган 16 та ТК ва ХК лари тегилини булади. Уларнинг бир кисми бутун ажратилган адрес сохасини ишлатилиши мумкун, масалан ПЗУ ва ОЗУ, айримлари эса факат бир неча адресларни.

Схемада келтирилган МПС куйидагилардан иборат:

дастурловчи периферия интерфейс микросхемаси ДПИ (ППИ (РРI ёки IОР)унга учта 8 битли мустакил канал РА, РВ ва РС оркали периферия, курилмаларини улаш мумкин; масалан, принтерни клавиатурани, 8 сегментли дисплейни ёки АЦП ва ЦАП, ДПИ (ППИ) оркали бошка МПС ёки ЭХСлар орасида маълумот алмашиши мумкин.

Клавиатура киритиш ва дисплейга чикариш махсус микросхемалар ёрдамида амалга ошириш мумкин.

Узоклашган курилмалар ёки абонент тормоги билан алока килиш универсал асинхрон кетма-кет узатишлар кабул килгич УА К УК (УСАПП-VART) дастурли алока интерфейси ДАИ (ПСИ-PCI ёки IOS) ёрдамида амалга оширилади. RxD- кабул килгич ва TxD- узатгич чикишларига алока линияси оркали бошка абонент ёки курилма узатгич ва кабул килгичи уланади.

Агар алока модем оркали амалга оширилса хохлаган тормокка уланиш имкони булади. Сигналларни частотаси ва давомийлиги буйича шу каторда товушли диапозони аник ва хар хил шакллантириши учун дастурловчи ораликли таймер ДОТ (ПИТ-PI) кулланилади ва у 3 мустакил 16 разрядли иккилик хисоблагичга эга хар бир хисоблагичнинг чикиш сигналини тутишни давомийлиги ёки частотаси кириш сигналини 3......65535 даврига каррали.

Агар тизимда МП ни аралашишини талаб килувчи ТКлар томанидан асосий дастур бажаришида узилиш тартиби кулланилса дастурли узилишлар контроллери ДУК(ПКП-PIC) (ТК дан IRi киришларига хизмат килиш учун мурожаатларни йигувчи курилма) куланилиши мумкин. МП ва ХК ёки ТК лардан бири орасида маълумотлар алмашинувчи ДС демифраторининг чикишида ~СS=0 сигнали хосил булгандагина амалга ошиши мумкин ва бу сигнал маълумот байтини укувчи ёки ёзувчи курилмага келиб тушади. Колган курилмалар суст холатда булади ва уларнинг сигнали~CS=1.

МП да маълумот байти ТК,ХК ёки МП дан катъий чекланган вакт оралигида хотирадан ёки хотирага (~МЕМР~MEMW) укишлар ёзиш бошкарищ сигналларидан бири таъсри пайтида ёки ТК лардан чикариш (~IOR~IOW) бошкариш сигналларидан бири таъсири пайтида укилади. Маълумотлар тез алмашинуви хотирага тугридан-тугри мурожат курилмаси ХТМ ёрдамида амалга оширилади.

4-5-6- маъруза.

МП буйруқлар тизими. буйруқ, дастур, буйруқ формалари, операция коди, буйруқларни адреслаш, буйруқ турлари буйруқлар тизими тушунчалари.

Ассембрлаш. хисоблаш машиналари тизимига асосланган ассемблер-тили. Машина кодлари асосида ассемблер тилида тўгри чизиқли дастурлар тузиш. бир кристаллик аниқ тизимли.

Ассембрлер дастурлаш тилида массифлар билан ишлаш асослари ва дастурлаш жараёнлари.

Микропроцессорнинг алоҳида "яқинлигини" кўпрок хисобга олувчи ва машина буйруқларининг мнемоник белгилашишга эга дастурлаш тили-Ассемблер деб номланади. Ассемблерда ёзилган дастур дастлабки деб аталади. Қуйида Турбо-Ассемблер номли версиясига тухталиб чикамиз.

Ассемблерда яратилган дастур қуйидаги босқичлардан ташкил топади:

- Алгоритмини блок схема ёки тузилишини тасвирлаш кўринишида тузиш;

- ЭХМга матн редактори ёрдамида дастлабки дастур PROG.ASM нинг матнини киритиш. PROG номи истаганга бўлиб, кенгайтириш албатта ASM-бўлиши керак;

- Дастлабки дастурни машина кодига TASM. EXE транслятор ёрдамида таржима (трансляция ёки ассемблерлаш) қилиш. Бу босқичда оралиқ махсулотни PROG. OBJ (объект коди) пайдо бўлади. Шу билан аниқланган синтаксис ва орфаграфик хатолар 2 чи ва 3 чи пунктларнинг такрорлашиши билан кузатилади;

- TLINK. EXE дастур ёрдамида PROG.OBJ объект кодини бажарувчи PROG. EXE ёки PROG.COM кодига айлантириш;

- Агар мантиқий хатолар учраса, дастурни бошланиши ва созланиши 1-пунктдан бошланиши.

Ассемблер дастурининг матни қуйидаги операциялардан иборат:

- буйруқлар ёки курсатмалар;

- директивлар ёки псевдооператорлар;

- операторлар;

- олдиндан аниқланган номлар.

б,в,г, пунктларида келтирилган операциялар томонидан шартланган ҳаракатлар трансляция босқичида бажарилади, яъни ассемблер буйруқлари деб хисобланади. Буйруқлар ёки курсатмалар деб номланадиган операциялар дастур бажарилиш вақтида амалга ошади, яъни микропроцессорнинг буйруқлари бўлиб хисобланади.

Буйруқлар формати ва уларнинг таснифлари.

Курсатма алоҳида қаторда ёзилади ва 4 қисмни ўз ичига олади, асосий эмаслари эса [ ] билан белгиланади:

|

[метка:] |

мнемоника_командалар |

[операндалар] |

[изоҳ] |

Метка (белги) ёки символик адрес - харф, сон ва белгилар ?@._$.-дан таркиб топган 31 та символга эга. Шунинг билан бирга сон биринчи бўлиб туриши мумкин эмас, нуқта эса, агар бўлса биринчи бўлиши шарт.

Мнемоника-код операцияси (КОП) буйруғини қисқартириб белгиланиши. Масалан, ADD мнемоника қўшишни (addition) билдиради.

Операндлар-аниқ ёки ноаниқ берилаётган иккилик тўпламлари устидан бажарилаётган операциялар бўлиши мумкин. Операндлар 4 та саноқ системаларидан бирида келтирилади ва 2,8,10 ёки 16-лик санок системаси учун в (В), о (О), d (D), h (H) символлар билан тугаши керак. Агар 16-лик сон харф билан бошланса, унга чап томонидан ноль қўшилади.

Буйруқлар системаси уч асосий белгилар билан тасвирланиши мумкин:

- буйруқ узунлиги ёки унинг томонидан байтларни эгаллаш сони,

- функционал вазифаси ва

- адреслаш усули

МП 1810ВМ86 (8086) учун буйруқлар бирдан 6 гача байтни эгаллайди. Биринчи байт буйруғи ҳар доим код операцияси ҳобланади, масалан INT XXh нинг код буйруғи CD (HEX) га тенг.

Функционал белгиси буйруғига курсатмаларни 5 та катта гуруҳларга бўлиш мумкин:

- маълумотларни узатиш буйруқлари;

- арифметик буйруқлар;

- мантиrий буйруқлар;

- eчиш буйруқлари ва

- бошқарув буйруқлари.

Адреслашнинг 5 та асосий усули мавжуд:

- регистрли;

- бевосита;

- туғри;

- билвосита;

- стекли.

Адреслашнинг қолган бошқа кўпгина усуллари юқорида санаб ўтилган усулларнинг комбинациялари ёки уларнинг кўриниши ўзгарганлиги бўлиб ҳисобланади.

Биринчи қоида операндлар МПнинг регистрларида жойлашган масалан, MOV AX, CX, буйруғи орқали СХ даги маълумот АХга узатилади.

Бевосита адреслашда операнд ҳотирадаги КОП да бевоита жойлашган, масалан. MOV AL, of5h кўрсатма 245 (15)ни AL регистрига ёзади.

Тўғри адреслаш ҳолатида КОП дан кейин операнданинг ўзи эмас, балки хотира ячейкаси ёки ташқи қурилма адреси келади, масалан, IN AL 40h адресли ташқи қурилмадан маълумотлар байтларини киритади.

Буйруқ буйича al аккумляторига ВХ регистрида сақланувчи хотира ячейкасидаги адресли сон ёзилади.

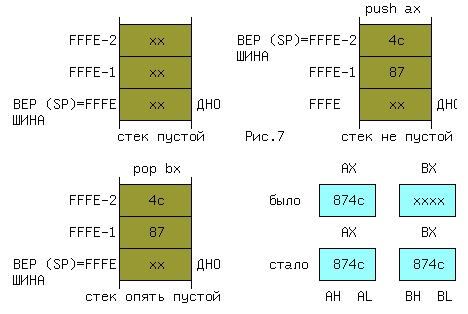

Стекли адреслаш-стек деб номланувчи хотира сохасида жойлашган операндлар бажарилади.Адреслашнинг одий схемали хотира сохаси, унга МП «/-келди-/-чикди». (LIFO) усули буйича мурижат килади. Дастурлар байти аператив хотрада усиб борувчи адресда кетма-кет жойлашган. Стек кетма-кет камайиб борувчи адреслар билан тулдирилади, хотирани 2 сохасининг олиш беркилиб колишини олдин олган холда стек одатда катта адресларда жойлашади стекнинг бош адреси адрес туби (bottom) деб аталади ва у SP регистрида MOVSP,OSFS EH буйруги билан ёзилади. SP регисторидаги галдаги киймат чукки адреси деб (top) деб юради стекнинг келса стек быт деб хиссобланади pusnax ва popbx буйруклар мисолида стекда маълумотларнинг жойлади ёки уларнинг олиш механизимининг куриб чикамиз. АХ акумляторнинг бошлонгич киймати 87 и с булсин

PUSH буйруги 4 боскичда бажарилади. SP да адрес 1 га копаяди: (SP)*<--(SP)-1

- Шу адрес быйича 87 катта байт жайлашади: ((SP))<--(AH).

- SP даги киймат яна 1 га камаяди: (SP)<--(SP)-1)

- Олинган адрес буйича 4 с кичик байт юкланади: ((SP))<--(AL)

POP буюруги хам юкори келтирилгандек химоя килинади лекин тескари тартибда,

- (BL) <- ((SP)),

- (SP) <- (SP) + 1,

- (BH) <- ((SP)),

- (SP) <- (SP) + 1.

Стекга байтлар катта байт катта адрес буйича коидаси билан жойланади, 7-Расмда PUSHAX буйруги бажарилгунга кадар бйт стек ва у бажарилганидан кейинги холатни 8-расда эса РОРВХ буйругини бажарилгандан кейинги холати курсатилган. Стекнинг афзал томони шундаки, дастурнинг узгарувчилар адреси абсалют киймати тугрисида хам схемаса хам булади, лекин бу нарса хаводам томонга эга агар дастурнинг эхтиёркор булмаса стекнинг курсаткичидаги киймат йуколиши мумкин ва бу холда каммпютернинг бошкариб булмайди, бу холнинг одатда котиб колди даб аталади.

Дастурларда стек куйидагилар учун ишлатилади

1) Хотирада саклаш ва ассамблер тилининг CALL ва RET (IRET) буйруклари ёрдамида кисм дастуридан кайтариш адресини олишда

2) Локал узгарувчиларнинг хотирасида саклаш

3) Кисим дастурларига фактик параметрларининг узатишда (юкори даражали дастурлаш тилларининг транслятарлари билан)

4) Фонли дастур узилганда регисторларидаги маълумотнинг вактинчалик саклашда.

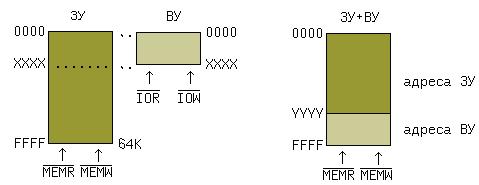

ТК учун адресли жой ажратилади, ва у ХК таркибига кирмаган еки унинг булаги булиши мумкин. Дастурли к-ч 2турда булиши мумкин Киритиш (IN) ва чикиш (OUT) ассемблер буйруклари ёрдамида.

- (MOV,LOPSB-) ассемблернинг узатиш буйрукларининг барчаси ёрдамида

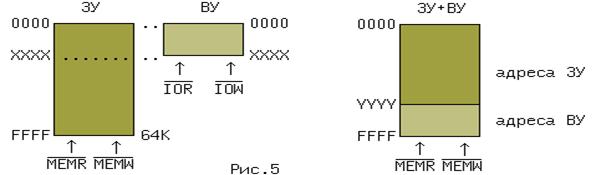

- 1. хол учун 64 к блок оралигида хотирани таксимлаш картаси 5-расмда берилган

0 0 0 0 , , , , х х х х чегара оралигида ТК ва ХК ларнинг адреслари кесишади. Шунинг учун хотра ячейкалари ёки ТК 1 кийматли мурожаат килишда процессорли блокда суриш билан башкарилувчи ни ~ IOR ~ IOW импульслар ТК га маълумотларнинг кучириш учун ~ MEMR ~ MEMW хотирасига ёзиш ёки укиш импульслари шакилланади. ХК маълумотлар ва дастурнинг жойлаш учун хажми кичраяди. 2-холатлар учун хотирали таксимлаш картаси 5-расмда курсатилган. В ХК га ХК сидан адрес сохасидан бир кисм ажратиб беради ХК хажми ТК учун ажратилган адреслар микдорида кичраяди 2-усул ТК хотира билан аперация олиб борувчи барча буйруклар ёрдамида адреслашга имкон беради. Дастурлик К-Ч нинг авзаллиги оддийлигида, лекин киритиш бажарилганда масалан клавиатурадан МП бошка фойдали иш бажармай 99,99 ....% вактнинг кутишга сарф килади. Бу камчиликнинг бартараф килишга К-Ч узулишлар буича к-ч имконият яратади.

1. $-дастурий ҳисоблагич. Бу символ жорий сегментда жорий адресни белгилайди. Байтлар ва қаторлар занжирининг узунлигини аниқлашда фойдалидир.

text DB 'This string has NN letters'

NN = $ - text; NN = длине строки text (количеству байтовв этой строке). Не путать часть строки '..NN..' и константу NN!

2. 2. @ data-маълумотлар сегментининг бош адреси.

....

mov ax,@data

mov ds,ax;

DS сегмент регистрида энди, мълумотлар сегментининг адреси.

3. ??date, ??tiem, ??filename-бу номер трансляция пайтида мос равишдаги сана; ASCII форматида файлнинг номи ва вактига алмаштирилади.

Операторлар

1. () қавслар ҳисоблаш тартибини аниқлайди.

2. [] масалан, [BX] хотира ячейкасида жойлашган вх адресли регистрни билдиради. Билвосита адреслашнинг аломати.

3. +, -, *, / - кушиш. Айириш. Купайтириш ва булиш операторлари.

mov ax, (2 * 3 + 8 / 2) - 2; ax регистрида 8 сони жойлашади.

4. МOD-модул бўйича бўлиш. Қолдиқни беради.

5. SHL, SHR-операндни чапга, унга суриш..

6. NOT - бит бўйича инверсия.

7. AND, OR, XOR - "И", "ИЛИ", "ИСК", "ИЛИ" операциялари. mov de (10d OR 5d) XOR 7d; (de)-8 га тенг бўлади.

8. : -сегментнинг қайта тайинланиши.

mov de [es : bx]; es сегментидан маълумотлар байтини ва унинг бошидан (вх) байтга ортда қолувчи (силжишни) de га жойлаштириш.

9.OFFSET-сегмент бошига нисбатан адресни суриш оператори (яъни сегмент бошидан адрес идентификаторигача бўлган байтлар сони).

mov bx, OFFSET table.

Директивлар (псевдооператорлар).

1. Яқин меткани аниқлайди (сегмент оралиғида).

jmp lbl .... ....

lbl: ....

2 . = - символик номга ифода кўринишини беради.

videoram=OB800h; videoram га OBOOOh номини беради.

3. .CODE - код сегментининг бошини аниқлайди, яъни дастур кодлари жойлашган сегментдир.

4. .DATA - маълумотлар сегментининг бошини аниқлайди.

5. DB, DW - бир ёки бир неча байтларни резервлаш директивлари: DB ёки бир ёки бир неча сўзлар DW.

.....DATA

fibs DB 1,1,2,3,5,8,13

rus DB 'Турбо Ассемблер'

buf DB 80 DUP(0);резервируется 80 байтов,каждый обнуляетсяint DW 65535;в двух байтах располагается число FFFFh.Array DW 100 DUP (0);резервируется 100 слов

6. END - датурнинг якунини билдиради.

.... .CODEMyPROG:....; точка входа (начало программы). ....; команды программы .... END MyPROG

7. ENDM - блок ёки макроаниқликнинг якуни.

8.ENDP - қисм дастурининг якунини билдиради.

9. EQU - символик ном ёки қаторга ифода қийматини беради.

BlkSize EQU 512BufBlks EQU 4BufSize EQU BlkSize * BufBlks

10. LABEL - мос турдаги меткани аниқлайди.

.... .DATAm_byte LABEL BYTE;метка m_byte типа BYTE позволяет теперьm_word DW 0;иметь доступ отдельно к каждому байту данных.CODE;m_word типа WORD

....mov [m_word],0204h

add [m_byte],'0';теперь в m_word хранится код add [m_byte+1],'0';3234h,ASCII код '0' равен 30h

11.LOCAL - макроаниқликларнинг ичида меткаларни локал аниқлайди ва хар бир макрокенгайтиришда улар ўрнига ассемблер уникал меткаларни киритади: ?? ХХХХ, ХХХХ=(0000 . . . ////) h га тенг. Нима учун ??ХХХХ? Чунки ҳеч кимга символик номни?? Билан бошлашни ҳаёлига келтириши мумкин эмас ва трансметор ўҳшашликдан қўрқмасдан меткаларни генерациялашиши мумкин.

12. MACRO - макроаниқлик киритади.

Swap MACRO a,b; a,b -макронинг параметрлари (хотира mov ax, b; ячейкалари) берилган макроаниклик хотира mov bx, a; ячейкалари орасида маълумотлар билан mov a, ax; алмашади, xchg буйру\идан ташкари;mov b, bx; mov a, b мумкин эмас.

ENDM

Буйруқ макросни чакириб олиш эмас - Swap m,n буйруги оркали бажарилади.

13. . MODEL - Маълумотлар ва дастур кодлари учун хотира улчамини аниқлайди.

. MODEL tiny ; қисм дастур, маълумотлар ва стек учун битта умумий сегмент (64 Kb) ажратади.

14. PROG - қисм дастурнинг бошини аниқлайди.

Print PROC NEAR; бу ерда кисм дастури буйруклари

Print ENDP ....call Print;кисм дастурини чакириш.

15. .STACK – стекнинг ўлчамини аниқлайди.

.STACK 200h; 512 байтни стек учун ажратади.

16. . RADIX base - саноқ системасини аниқлайди base -саноқ системасининг асоси: 2,8,10,16.

.RADIX 8oct =77; oct = 63 d га тенг

17. ; изохнинг боши.

Узатиш буйруқлари.

1. MOV DST, SRC; (SRC) ни (DST) га узатиш. Шу ерда ва келажакда регистр ичидагиси, масалан AL регистри (AL) ёки (al) кўринишида белгиланади изоҳни узатиш эса ‹-- белги билан белгиланади.

mov al ch; ‹--(ch)mov cx, dx ;mov bn, [mems]; mems символик адресли хотира ячейкаси ичидагиси ВН регистрга узатиш. Куйидагича килиш хам мумкин: mov bh, mems.mov al, [bx]; ВХ регистрида жойлашган адресли хотира ячейкасини аккумляторга узатиш. mov bx, OFFSET src; жорий сегментда SRC хотира ячейкаси адресининиг силжишини BX га жойлаштириш. Mov al, table [bx]; байтлар жадвалининг символик адресли table бирлиги элементни ва бу элементдан (bx) байтга кечикаётган элементни акумляторга жойлаштириш Бошка вариантлар: mov al, [table+bx] ёки

mov al, table+bx. mov al,table + bx.

|

Команда бажарилишидан олдин mov al,[table + bx] |

Регистр BX |

Регистр AL |

Адрес |

Код |

|

0010 |

XX |

0800 (table) |

8с |

|

|

08xx |

xx |

|||

|

0810 |

58 |

|

Команда бажарилишидан сўнг mov al,[table + bx] |

Регистр BX |

Регистр AL |

Адрес |

Код |

|

0010 |

58 |

0800 (table) |

8с |

|

|

08xx |

xx |

|||

|

0810 |

58 |

2. PUSHRP ; жуфтлик регистридан маълумотни стекнинг юқорисига жойлаштириш (масалан, push bx).

3. POPRP ; стек юқорисидан 2 байт олиб уни RP жуфтликка жойлаштириш (масалан, pop ax).

4. XCHG DST, SRC ; (DST) ва (SRC)лар ичидагиларини жойларини алмаштириш. Икка операнд бир вақтда хотира ячейкасидаги маълумот бўла олмайди.

5. XLAT SRC; жадвал бошидан (AL) сонига тенг маълумотлар байти SRC бошланғич адресли жадвалдан олиб, уни AL га жойлаштириш. SRC адрес BX регистрида жойлашган бўлиши керак. Бошқа вариант: XLATB.

....

.DATAsrc DB 15d,10h,00110101b,'A','B',166d.CODE

.... mov al,2; в результате выполнения этих трех команд mov bx,OFFSET src; в регистр AL будет загружен кодxlatb; 00110101b = 35h = 53d = ASCII'5'

6.IN ACCUM, PORT; AL ёки AX байтини ёки PORT адресли портдан сўзни акумуляторга жойлаштириш. Агар порт адреси ‹= FF бўлса, порт адреси бевосита кўрсатилиши мумкин, агар порт адреси ›FF бўлса, порт адреси ВЧ регистри ифодаси орқали билвосита кур сотилади (POH махсус функцияси).

OUT PORT, ACCUM; AL аккумуляторидан ёки AX байтидан ёки сўзни PORT символик адресни ТК га узатиш.

7. OUTOUT PORT, ACCUM; AL аккумуляторидан ёки AX байтидан ёки сўзни PORT символик адресни ТК га узатиш.

out 0ffh,al;

....mov dx,37Ah;маълумотлар сўшзини AX дан ВУ га узатиш адрес-

out dx,ax; порт сом 37Ah

8. LET RP,M ; М символик адресли хотира ячейкасини эффектив адресини (силжишини) RP регистрга юклаш

lea di, rus; бу команданинг аналог кўриниши - mov di, OFFSET rus.

Арифметик буйруқлар

1. ADDADD DST, SRC; SRC ва DST

add al, [mem_bute]; mem_bute-бир байти хотира ячейкаси

add [mem_word], dx; mem_word-икки байтли хотира ячейкаси

add ch,10001010b;

2. INC DST; (DST) ни 1тага купайтириш (инкремент (DST)).

inc si; (SI) <-- (SI) + 1. inc count; (count) <-- (count) + 1.

3. SUB DST, SRC ; (SRC) ни (DST)дан айириш ва натижани DST га жойлаштириш.

4. DEC DST; декремент (DST)Г

5.5. CMP DST, SRC ; DST ва SRC ни ичидагисини солиштириш. Бу буйруқ (SRC) дан (DST)ни айиришни бажаради, лекин фарқини DST га жойлаштирмайди ва операция натижасини натижаси буйича байрокларга таъсир курсатади.

шарт байроқлар OF SF ZF CFDST > SRC 0/1 0 0 0

DST = SRC 0 0 1 0 DST < SRC 0/1 1 0 1

0/1 - операциянинг қийматига қараб байроқни 0 ёки 1 га тенглигини билдиради. OF ва SF, байроқ белгили сонли операцияларда маънога эга, CF байроғи эса 1 га қўйилади, агар қўшиш ёки айириш операцияси натижасида қолдик қийматини катта иккилик разрядига ўтказганда ва шу катта иккилик разрядидаги билан мос келганда бошқа аниқлашда OF 1 қийматини қабул қилади, агар натижа берилган оралиқ мос равишдаги сонлар оралиғидан ошиб кетса. DST › SRC ва иккаласи ҳам бир байтли сонлар бўлса, унда:

DST: 1. (+127) 2. (+127)

SRC: - (+2) - (-2)

------- -------(+125) (OF)=0 (+129)? (OF)=1

Иккинчи мисолда натижа оралиқдан ошиб кетаяпти: -128‹=х‹=+127 SF белгиланган байроқ "1" га қўйилади, агар операция натижасининг катта бити 1га тенг бўлса, яъни масофий натижада. Тескари бўлганда тушириб кетилади. ZF ноль байроғи (!) нолли натижада "1" га қуйилади аксида тушириб қолдирилади. Узатиш байроғга CF=1 тенг, агар қўшишида катта разряддан узатиш ёки айиришда кичик рязраддан қолдиқ олиш бўлса. Акс ҳолда байроқ тушириб қолдирилади. Биринчи мисол учун SF=ZF=CF=0, иккинчиси учун: SF=1, ZF=CF=0.

Мантикий ва суриш буйруклари

1. AND DST, SRC; разряд бўйича "И".

mov dh, 10101100b;

and dh, 0f0h;

шу икки буйруқни бажарилиши натижасида DH нинг ичидагиси 10100000b га тенг бўлиб қолади.

2. OR DST, SRC; разряд бўйича мантиқий элемент "ИЛИ".

or bx,dx;если (BX)=5F0Fh,(DX)=7777h бўлса операциядан сўнг;(BX)=7F7Fh.

|

BX |

0101 1111 0000 1111 = 5F0F |

|

DX |

0111 0111 0111 0111 = 7777 |

|

BX (натижа) |

0111 1111 0111 1111 = 7F7F |

3. XOR DTS, SRC; разряд бўйича матиқий "искл. ИЛИ"

xor al,55h;агар бўлса (AL)=5ah, операциядан сўнг (AL)=0fh.

4. NOT DST; қабул қилувчи ҳамма битларни инверсияси.

5. TEST TEST DST, SRC; AND операциясини бажаради, аммо фақат байроқларга операцияларни ўзгартирмасдан таъсир кўрсатади.

6. SHR DST, CNT; мантикий унга суришгандан быш колаётган битлар ноллар билан тылдирилади, унг томондаги четки бит СF байрогига чикариб юборилади. DST операнди хотира ячейкаси булиши мумкин.

mov bl,10110010b;(CF) = x

shr bl,1;(BL) = 01011001,(CF) = 0

|

до сдвига |

|

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

|

(CF)=X |

|

после сдвига |

0---> |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

------> |

(CF)=0 |

mov cl,4;

shr bl,cl;(BL) = 00000101,(CF) = 1.

7. SHL DST, CNT ; матикий чапга суриш

8. RLC RLC DST, CNT; колидикниутказиш оркали чапга циклик суриш

9. RRC RRC DST, CNT; колидикли утказиш оркали унга циклик суриш

10. ROR ROR DST, CNT; чапга циклик суриш

11. ROL ROL DST, CNT; унга циклик суриш

Бошқаришни узатиш буйруқлари

1. CALL CALL SUB R ; SUBR адресли кисм дастурини чакириш

call delay; mov ....

2. RET CALL га бевосита қисм дастуридан кейинги операторга қайтариш, яъни юқорида келтирилган мисолдаги MOV га .

3. JMP NAME ; NAME символик адресли буйруқга шартсиз ўтиш

jmp short name;переход к метке name, отстоящей не более

чем на -128 или +127 байтов.

jmp near name;переход к метке name, отстоящей не более

чем на 65535 байтов, в одном сегменте.jmp name;аналогично jmp near name;

4. JA NAME ёки JNBE NAME : шартли ўтиш, агар масалан: CMР DST, SRC солиштириш натижасида қабул қилувчи (приёмник) берувчидан (источник) абсолют катталик бўйича катта бўлса, name меткага ўтиш керак.

5.5. JB NAME ёки JNAE NAME: шартли ўтиш агар масалан, CMР DST, SRC солиштириш натижасида қабул қилувчи манбадан абсолют катталик бўйича кичик бўлса, унда name меткага ўтиш керак (4n ва 5n, буйруқлари белгисиз сонли операциларни бажариш натижалари устида бажарилади).

6. JZ NAME ёки JE NAME : ўтиш, агар нолинчи байроқга таъсир қилувчи операция натижаси - ноль бўлса ("ноль" бўйича ўтиш).

7. JNZ NAME : ёки JNE NAME; "ноль эмас" бўйича ўтиш (6п ва 7п буйруқлари, белгили сонли операциялари бажарилиш натижалари устида бажарилади).

Циклларни бошкариш буйруклари

1. LOOP NAME: бу буйруқ (СX)ни 1 га ноаниқ камайтиради ва яқин меткага ўтишни бажаради, агар (СХ)?0 га тенг бўлмаса

.... mov cx,64h; syc меткадан loop syc гача опкраторлар блоки syc: ....; 100 марта бажарилади. .... loop syc

2. LOOPZ NAME ёки LOOPE NAME : бундан ташқари ZF байроғининг текширишни ҳам бажаради. Шунинг учун цикл (CX)=0 ёки (ZF)=0 ёки у ҳам бу ҳам биргаликда бўлгандаги шарт билан тугайди. Шунинг билан бу буйруқ биринчи нол эмас бўлган натижани аниқлаш учун хизмат қилади.

3. LOOP NZ, LOOP NE - "нол" бўйича циклдан чиқиш

.... mov cx,1000d; цикл эртпроқ тугаши мумкин 1000next: .... ;ўтишлар, агар аккумулятор хотираси .... ;129 га тенг бўлса,яъни ASCII кодга тенг бўлса cmp al,'Б';Б харфлари. loopnz next

Қаторлар устида ишлаш буйруқлари (байт занжирлари)

1. LOD.SB: lodsb буйруғи маълумотлар сегментидан ST региср орқали адресланган байтни юклайди ва ST ни 1га купайтиради, агар бундан олдин CLD буйруғи киритилган бўлса (DF йўналиш байроғини тозалаш) ва St ни 1га камайтиради, агар STD буйруги ишлатилган бўлса (йўналиш байроғи ўрнатилиши) .

....

.DATA

string DB 'abcdefg'

.CODE

....

cld;после выполнения этих команд в AL будет

mov si,OFFSET [string+2]; загружен ASCII код 'с'

lodsb;причем содержимое SI будет указывать на 'd'.

2. MOVSB: бу буйруқ SI регистридаги хотира ячейкаси адресидан бир байтни DI регистрдаги хотира ячейкаси адресига ўтказади ва (SI) ва (DI) ни 1 га қўпайтиради. SI нинг қиймати DS маълумотлар сегментида ҳам қўшимча ES сегментида жойлашиши мумкин. DI нинг қиймати фақат ES қўшимча сегментда жойлашиши мумкин.

.... .DATA msg DB 'Всё O.K.'LEN = $ - msg;LEN равно 8

.CODE .... cldlea si,msg;в SI манба адреси

mov ax,0b800h; видео хотира сигмент хажми

mov es,ax;қўшимча сигментга ўтказишlea di,es:(0a0h * 3); юқоридан 4-сатр

mov cx,LEN;LEN – чиқиш символлар сониrp: movsb; экраннинг жорий позициясига символни юбориш

inc di;атрибут позициясидан сакраб ўтиш

loop rp; тугагунча давом эттириш (CX)

....;строка 'Всё O.K.' дисплей юқорисидан

;4- сатрга чиқарилади.

3. REP: буйруқни кайтариш префикси. Масалан, олдинги дастурнинг тугаши қуйидагича ёзилиши мумкин:

....

mov cx,LEN;несмотря на то,что массив'Всё O.K.'будетrep movsb;скопирован в область памяти B800:(A0 * 3), на ;экран дисплея будет выведено: ВёOK. Почему?

4. CMPSB; (ST) адресни берувчининг қатор байтини, (DT) адресли қабул қилувчининг қатор байтини солиштиришни бажаради: яъни ((ST))-((DI)) айиришни бажаради. CMP DST, SRC буйруғи билан янгилишмаслик керак, қайсики қабул қилувчидан берувчини айриш бажарилади. CMPSB буйруғи (CX)ни 1 га ноаниқ камайтиради ва (SI) ва (DI) ни 1 га купайтиради, агар (DF)=0 булса.

5. REPZ ёки REPE: қайтариш префикси. Агар (CX)=0 ёки (ZF)=0 бўлса, буйруқни бажариш тамомланади.

....

.DATAsrc DB 'To be, or not to be'dst DB 'To be ,or not to be'len = $ - dst;len равно 19

.CODE ....cld; (DF) = 0

push ds;совместить адреса pop es;сегментов ds и es mov cx,len;длину строки dst переслать в cx lea di,dst;загрузить адрес(смещение) строки dst в DI lea si,srcrepe cmpsb;сравнивать побайтно je equal;если все байты совпали, то перейти к метке not cx;если нет - вычислить номер несовпадающих байтadd cx,len;

jmp notequal;equal: .... ....notequal: ....

Шу масала охирида мос келмайдиган биринчи номери байт (CX)=5 га тенг.

Миропроцессорни бошқариш буйруқлари

1. CLC: ўтказиш байроғини тушириб юбориш (CF)=0. .

2. STC: ўтказиш байроғини ўрнатиш (СF)=1.

3. CMC: йуналиш байроғини инверслаш.

4. CLD: йуналиш байроғини тозалаш(DF)=0, бундай ҳолатда қатор(байт занжирлари устида операциялар) кичик адресдан катта адресгача бажарилади.

5. STD: йуналиш байроғини ырнатиш (DF)=1, байтлар занжирлари устида ишлаш катта адресдан кичигигача бажарилади.

6. STT: урилиш байрогини ўрнатиш (IF)=1, ташки қурилмалардан узилишни руҳсат бериш.

7.CLT: узилиш байроғини тозалаш

8. MOP: маҳфий операция

Узилиш буйруклари

1. INT INUM : бу команда дастурли узилишни чақиради, яъни тўртача байтдан сақланаётган адресни INUM *4 адресидан бошлаб, бу ерда INUM=(0...25) га тенг хотира ячейкасига ўтиш. Бу 4 байтли сон берилган узилишнинг қисм дастури қайта ишловчининг курсаткичи бўлади ва у бошқача номи узилиш вектори деб аталади.

Дастурли узилишлар ёрдамида вужудга келадиган операциялар АН регистридаги код орқали аниқланади, масалан,

....mov ah,14d;дисплейга символлврни чиқариш

mov al,31h;курсорни битта ўнгга суриш.

int 10h;экранга '1' символни чиқариш(ASCII код 31h).

....

.DATAprivet DB 'Хайрли тонг!','$';

.CODE ....lea dx,privet;DX регисторнинг махсус функцияси

mov ah,9;9 – дисплейга чиқриш int 21h;саломлашиш чиқарилади ....

Байроқларга буйруқларнинг таъсири

Жадвалга факат байрокларга таъсир киладиган курсатмалар киритилган.

7- маъруза.

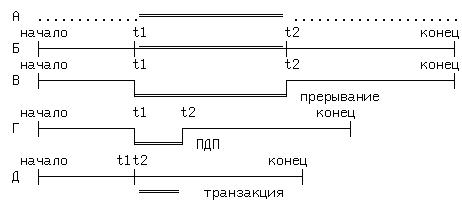

Маълумотлар алмашиш усуллари. МП ва хотира ўртасида маълумотлар алмашиш усуллари.

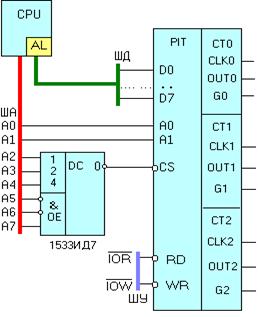

Дастурли

периферия интерфейси (ДПИ)нинг шартли белгиланиш ва уни микропроцессор тизимига

уланишнинг былиши мумкин булган схемалардан бирининг схемаси кырсатилган. PPI ташки курилмалар билан икки томонлама 8 битли 3 та

алока каналига эга. Улар-РА, РВ, РС портлар деб аталади. РС порти колганларидан

шуниси билан фарк каладики, уни иккита мустакил 4 битли портларга былиш мумкин,

яъни D7. . . . D4 катта ярмига ва D3. . . . D0 гача булган кичик яримига.  Паралел интерфейс

(IOP) деб номланадиган, ДПИ икки томонлама D7. . . .D0 тристобил чикишлар

ёрдамида маълумотлар шиносига уланади. А1, А0 киришлар маълумотлар алмашиш

туртта каналдан бирини танлашни бажаради: РА,РВ,.РС учта портдан ёки бошкаришлар

холатини ички регистрида (БГХР ёки CSR-Control and Status Register).

Паралел интерфейс

(IOP) деб номланадиган, ДПИ икки томонлама D7. . . .D0 тристобил чикишлар

ёрдамида маълумотлар шиносига уланади. А1, А0 киришлар маълумотлар алмашиш

туртта каналдан бирини танлашни бажаради: РА,РВ,.РС учта портдан ёки бошкаришлар

холатини ички регистрида (БГХР ёки CSR-Control and Status Register).

|

A1 |

A0 |

КАНАЛ |

|

0 |

0 |

PA |

|

0 |

1 |

PB |

|

1 |

0 |

PC |

|

1 |

1 |

CSR |

PPI «микросхема танлаш» дешифратор адресининг чикишидаги ечилиши инверс киришдаги актив сигналнинг ёрдамида иш холатига келтиради. (Chip, Selekt, Crystall Selekt, CS)~СSК0 (расмда тулик былмаган N-HE элементининг чикишида мантикий ноль пайдо былади, агар унинг ХАММА кириш сигналлари ‘1’ га тенг былса (А7=А6=А5=А4=1). Адреслар шиносига (АШ) юкоридаги киришлар каби уланган А, А0 киришлар ёрдамида чунончи у ёки бу канални танлаш мумкин булса, унда АШга дешифратор киришларни хисобга олган холда куйидаги камбинациялар мавжуд:

|

АДРЕС ШИНАЛАРИ ЛИНИЯСИ |

КАНАЛ/ПОРТ |

АДРЕС (HEX) |

|||||||

|

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

||

|

1 |

1 |

1 |

1 |

x |

x |

0 |

0 |

PA |

F0 |

|

1 |

1 |

1 |

1 |

x |

x |

0 |

1 |

PB |

F1 |

|

1 |

1 |

1 |

1 |

x |

x |

1 |

0 |

PC |

F2 |

|

1 |

1 |

1 |

1 |

x |

x |

1 |

1 |

CSR |

F3 |

Адреслар шинасининг А3, А2 линиялари схемада ишлатилмаган, шунинг учун уларнинг киймати жадвалда Х (х Don’t Care Bits) белгиланган. 16-чи адресни хисоблашда дастурчи бит кийматлар сифатида хохлаган кийматларни, юкорида келтирилган жадвалдагидек, ноллар хам куйиб чикиш мумкин. Масалан, РВ порти учун иккилик коди 1111хХ01=11110001(BTN)=К1 (NEX).

РРI портларига уланган МП (СРИ)ни ва ташки курилмалар (ТК) орасида маълумотлар байтлари билан алмашинуви ассемблер IN. . . . ва OUT . . . . буйруклар ёрдамида бажарилади, масалан: in al, XX ва out XX, al.

IN ва OUT буйрукларининг бажарилиши икки этапда бажарилади (микропроцессорнинг конкрет архитектурасига боглик, тактларни ва циклларни хисобга олмаган холда). Мисол: IN AL, OF1h ва OUT OF1h, AL курсатманинг бажарилиши.

· 1 этап). АШ сига МП адресни (масалан Г1) жойлаштиради ва у дешифрацияланади (бизнинг мисолда И-НЕ элементи). Дишефратор чикишда актив боскич (0) ~ CS инверс киришга келади ва PPI ни иш холатига утказади.

· 2 этап) а) OUT буйруги. Кейинги вакт пайтида МП AL регистрида жойлашган байтни маълумотлар шишасига жойлаштиради ва бир вактда ~ бошкариш киришига келаётган ~IOW строб ёзувини ишлаб чикаради. ~IOW импульси мос равишдаги портнинг чикиш регистридаги маълумотлар байтини илиб куяди (бизнинг мисолда РВ порти) б) IN буйруги. МП~RD куйиш бошкарув киришга AL акумуляторига маълумотлар шинаси (МШ) оркали РВ портидан маълумотлар байтини укиш учун ~IOR - строб укишни юборади

PPI бажараётган операцияларнинг тури (ишлаш режими) унинг бошкарув регистрига ёзиб куйилган ахборотига боглик. Бу ахборот бошкарув байти ёки буйрук деб номланади. Бундай режим быйича ахборот масалан маълумотномада: микропроцессорлар ва микро ЭХМ, Х вох С.Т. мухаррири остида. Куйида куп ишлатиладиган режимлардан бири “0”- режимида D6, D5, D2-битлардан ноллардан куришиб турган, бошкарув байтининг формати келтирилган.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

1 |

0 |

0 |

PA |

PCh |

0 |

PB |

PCl |

PA,PB,PCh, PC1 битлари портлари оркали маълумотлар узатишнинг йуналишини аниклайди (агар порт масалан, чикишга мулжалланган булса, IN буйруги ёрдамида МП га маълумотларни у оркали киритиб булмайди).

Агар санаб утилган битлардан бири урнатилган (унга 1 ёзилган), булса, унда мос равишдаги (МП --> Т.К), агар бит тушириб колинса (унга “0” ёзилган), унда порт чикиш учун мулжалланган (МП--> Т.+).

8- маъруза.

Микро ЭХМ ва МП тизимларини ташкил этиш жараёнлари.

РАУ ва

АРУ ташки курилма сифатида PPI га улаш мисоли куйидаги расмда келтирилган .  Аналог-ракамли

ызгартиргичнинг кетма-кетлик якинлашиши (МП ларда кенг таракалган) РА портининг

ракамли чикишига уланган (бошка портщам былиши мумкин). R таш.г ёкиш кириши РС

портининг линияларидан бирига уланган узгартиргичнинг тайёрлик чикиши РС7

линияси билан уланган.

Аналог-ракамли

ызгартиргичнинг кетма-кетлик якинлашиши (МП ларда кенг таракалган) РА портининг

ракамли чикишига уланган (бошка портщам былиши мумкин). R таш.г ёкиш кириши РС

портининг линияларидан бирига уланган узгартиргичнинг тайёрлик чикиши РС7

линияси билан уланган.

Расмдан куриниб турибдики, РА порти кодни кириши Икир кучланишига тугри пропорционал булган кодни киритишга, РВ порти эса-кодни чикаришга созланган былиши керак. Шунинг учун бошкарув байтининг D4 (РА) бити урнатилган D1 (PB) бити эса тушириб колдирилган булиши керак.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

1 |

0 |

0 |

1 |

PCh |

0 |

0 |

PCl |

Кейинчалик шунга эътибор киламизки РС0 линияси у билан бирга хамма РС1нинг кичик ярим кисми чикишга, РС7 (РСh)линяси-эса киришга созланган булиши керак, шунинг учун келтирилган вариантни АРУ ва РАУ га улаш учун охирги бошкарув байти куйидагича куринишга эга булади:

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

HEX код |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

98 |

Энди АРУ нинг вакт диограммасини хисобга олган холда. РАУ нинг ишлашини бошкариш дастурининг намунавий фрагментларини келтирамиз.

R=1 импульсининг келиши билан узгартиргич актив холатга келади (регистр нолланиши руй беради). R сигнали манфий камайиши билан узгартириш жараёни ишга туширилади ва Тузгар вактидан кейин узгартиргичнинг чикишларида янги код хосил булади. Шу пайтда АРУнинг чикиш тайёрлигида ~ RDY=0 сигнали щосил булади, бу шуни англатадики, навбатдаги узгартириш циклининг якунини англатади.

; ++++++++ PPI ни ишга тайёрлаш ++++++++ mov al,98h ; бошкарувчи байтни ёзиш 98out 0f3h,al; F3 адресли регистрга

........... ; ++++++++ АРУ ни ишга тушириш хисоблаш ++++++++ mov al,01 ; PC0 линияда out 0f2h,al; (R = 1) импульсни шакиллантиришmov al,00 ;

out 0f2h,al; (R = 0) w: in al,0f2h ; PC портдан аккумуляторга байтларни киритиш

test al,80h; PC7 тайёрлик битини селетциялаш (маска 80h),

jnz w ; нолга тенг булмаса киритишни кайта бажариш

in al,0f0h ; агар АРУ тайёр булса PA портдан кодни киритиш ...........; F0 адресли (АРУ чикиши) аккумуляторга.; энди кучланиш кодини , мисол учун, дисплейга чикариш мумкин; ++++++++ РАУ га кдни чикариш ++++++++ mov al,XXh ; талаб этилаётган ХХ кийматни аккумуляторга киритиш out 0f1h,al; ва уни F1 адресли РВ порт оркали РАУ га узатиш. ...........

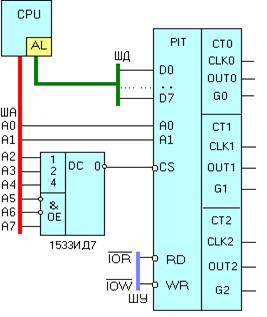

3та унолтиразрядли сиихрон

оширувчи кодни синхрон юклайдиган СТ: мустакил хисобланишга эга. Куйидаги

расмда МП системасига дастурланувчи интервал таймернинг шунинга хос схеманинг

уланиши келирилган. Схеманинг чап кисми дастурланувчи интервал таймерига

уланиши схемаси олдинигисига айнан бир хил булиб, лекин шуниси билан фарк

киладики дешифратор сифатида мазхур булган ИD7микросхема ишлатилган.

Хисоблалич чикишларининг вазифалари: CLK;-такт частотаси сигналининг куриши. С(АТЕ)i-Хисоблашга бошкаришни бош/тук кириши. Оит;-сигнал чидиши.

А1,АО киришлар 3та хисоблагичдан ёки бошкарув регистридан бирини танлашни бажаради.

|

A1 |

A0 |

БОШКАРУВЧИ СЧЕТЧИК / РЕГИСТР |

|

0 |

0 |

CT0 |

|

0 |

1 |

CT1 |

|

1 |

0 |

CT2 |

|

1 |

1 |

CSR |

Колган чикишлар шу комлекдаги бошка микросхемалар функциялирга ухшаш вазифани бажарадилар.

Келтирилган конкрент схемада Chip selekt кириш дешифратор адресининг о-чи чикиши билан уланган. CPU PII га мурожат килганда DC нинг ишлаш мантикига мос булган бошкарув ОЕ киришларда актив даражалар булиши керак: А7=I. A6=A5=0. Дешифраторнинг адресли киришларида о-чи чикишни актив холатга келтириш учун А4=A2=A1=0 иккилик коди жойланиши керак. Илгари келтирилган А1,АО битларни хисобга олган холда тайёр куйдаги адресларга эга:

|

АДРЕСА ШИНА ЛИНИЯСИ |

БОШКАРУВЧИ СЧЕТЧИК / РЕГИСТР |

АДРЕС (HEX) |

|||||||

|

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

||

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

CT0 |

80 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

CT1 |

81 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

CT2 |

82 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

CSR |

83 |

Хар бир щисоблаличнинг ишлаш режими бошкарув байтини ва Ni булиш коэффициентининг бошлангич кийматини (хисоблош модули) ёзиш йули билан дастур ёрдамида урнатилади. Бошкарув байтининг формати куйида келтирилган.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

|

D7 |

D6 |

Счетчика номери |

|

Ni ни счетчикга юклаш усуллари |

D5 |

D4 |

|

0 |

0 |

Счетчик 0 (CT0) |

Ni Фиксацияси |

0 |

0 |

|

|

0 |

1 |

Счетчик 1 (CT1) |

Ni ни битта кичик байт билан юклаш |

0 |

1 |

|

|

1 |

0 |

Счетчик 2 (CT2) |

Ni ни битта катта байт билан юклаш |

1 |

0 |

|

|

1 |

1 |

Запрет |

Ni ни иккита билан юклаш |

1 |

1 |

|

D3 |

D2 |

D1 |

|

|

Формат записи Ni в счетчик |

D0 |

|

0 |

0 |

0 |

Режим 0 |

Запись Ni двоичным кодом |

0 |

|

|

0 |

0 |

1 |

Режим 1 |

Запись Ni двоично-десятичным кодом |

1 |

|

|

x |

1 |

0 |

Режим 2 |

|

||

|

x |

1 |

1 |

Режим 3 |

|||

|

1 |

0 |

0 |

Режим 4 |

|||

|

1 |

0 |

1 |

Режим 5 |

|||

Бошкарув байтининг 2та катта D7,D6, битлари мос булган хисоблашчининг бошкарув регистрининг номерини аниклайди.

Ni хисоблаш модулини ёзиш усулини i-чи хисоблашчининг D5,D4, битларида беради.

· Агар 3<= Ni <=255, <=Ni <=255 6улса унда i чи хисоблашининг булиш коэффициентини битта кичик байт ёрдамида дастурли юклаш МУМКИН «0» га тенг булган катта байтнинг киймати эса тайиёр ёрдамида хисоблашига автоматик равишда ёзиб куйилади (D5=0, D4=1)

· Агар 256<= Ni <216 <= Ni<2,16 ва 256 га каррали булса унда i-чи хисоблашчининг булиш коэффициенти битта катта байт ёрдамида дастурий юклаш мумкин 0-га тенг булган кичик байтнинг киймати эса таймер ёрдамида хисоблашга автоматик равишда ёзиб куйилади (D5=1, D4=0).>

· Ва якунда, агар 256<= Ni <=256,<Ni<2,16 ва 256га каррали булмаса, унда i-чи хисоблошчининг булиш коэффициэнтини иккала байт ёрдамида юклаш керак (D5=1, D4=1). >

D3,D2,D1 битлар чикиш сигналининг формасини аниклайди.GATE=1 былганда 0,2,3,4 режимларида хисоблаш рухсат берилади ва GATE=0 булганда акси булади. 1 ва 5 режимларда хисобни бошлаш учун GATE киришига мусбат сакраш (перепад) бериш зарурдир.

· О-чи режим. Дастурий вактда кечикиш OUTi чикишида мусбат сакраш (перпепад) Тчик=Ткир *(Ni+1) вактдан кеийн шаклланади. Ткир-CLK; киришидан импульснинг кайтарилиш даври

· 1-чи режим. Берилган давомийлик якка импульс генератори. Манфий импульснинг давомийлиги куйидан нисбат ёрдамида аникланади. Тчик= Ткир*Ni

· 2-чи режим Q>2 скважностли импульслар кетла-кетлигининг даврий равишдаги гинератори. Хисобланинг чикишидаги импульсларнинг келиб чикиш частотаси ; Fчик= Fкир / Ni. F чик =1/Т чик ва F кир =1/ Т кир. Скважность кайтариш даврининг импульс давомийилига нисбатидир (Т чик / Ти)

· 3-режим Q=2 скважности импульслар кетма - кетлигининг даврий равишдаги генератори. Хисоблаш чикишидаги импульсларининг келиб чикиш частотаси, иккинчи режимдагидек булади.

· 4-чи ва 5-чи режимлар. Дастурий ва аппаратли бошкарув строб-импульси. Туртинчи режимда Тчик= Ткир *(N+1) кечикишли давомийлиги Т кир булган калта импульс шаклланади. 5-чи режимда эса. Ткир=Тчик *N кечикишли худди шундай импульс шакланади.

Д0 бит хисоблагичга Ni кодини форматини ёзишни регламентлаштиради. Агар Dо = 0 булса, юкламаётган код хисоблагич томонидан иккилик деб аслида эса - иккилик - унлик деб ташкил килинади.

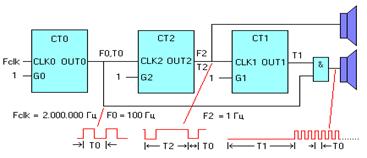

.1PIT ни ишлатиш мисоли

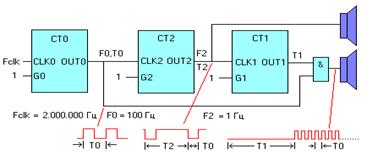

Куйидаги расмда Т1 вакт интервал давомийли дастурли ва Т2 даврда кайд килинган товуш ва F0 частотада Т1 вактдан кейин сигнализация берилган DИТ ни куллаш купгина схемаларидан бири таймер сифатида келтирилган.

Лойихалаш учун бошлангич маълумотлар;

· 1.Т1=15сек вактда кечикиш интервали давомийлиги

· 2. Кириш сигналининг частотаси Fcek=2 МГц

· 3. Кайд килинган товуш частотаси F2=1Гц

· 4. Сигналининг частотаси FO=100Гц

Хар бир хисоблаши учун Ni- булиш коэффициентини ва бошкарув байтларини хисоблаб чикиш керак.

· СТО хисоблагич. СТО хисоблагич учун бошкарув байтининг битлари частотали сигналнинг шакланиши учун 2-чи ва 3-чи режимлар мос келади. Аммо 2-чи режимлар (импульсларининг скважностлиги юкори булгани учун импульсларнинг давомийлиги кайтариши даврига нисбати кичик) Q/2 марта сигналнинг =увватини камайтиради. Шунинг учун 3-чи режимни танлаймиз ва D3,D2,D1= x11=(011 ёки 111) битлар булади. СТО нинг булиш коэффициэнти 3-чи режимда №=2000000Гц/100 Гц=20000(DЕС)=4F20(HEX) булади. N0(20000) < 2^16 ва 256 га булинмаганлиги учун N0 кодини хисоблашига юкланиши иккита 4Е ва 20 байтлар ёрдамида божарилиш керак. Шундан келиб чикадики битлар D5,D4=11тенг DO битининг кийматини аниклаш колди.No=20000 (бешта унлик сонни) иккилик-унлик кодининг киймати билан ун олтилик битлик хисоблашка (туртта ерим байт-турта унлик сони) юклаш мумкун эмас, шунинг учун D0=O (N0 ни иккилик кодида юклаш) Шу билан СТО учун бошкарув байти 36 (3Е) га тенг булади;

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

HEX код |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

36 |

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

3E |

· СТ2 хисоблашгич. СТ2 хисоблашчининг бошкарув байтининг битлари D7, D6=10. Унинг чикишида 1Гц частотали сигналнинг шакллантириш учун, 2-чи ва 3-чи режимлар мос келади.Аммо 3-чи режимда Q=2 скваженост булганда, юкори динамиканинг пьезонерамик пластиналари СТ2 нинг чикишида хар бир сакрашда (перепад) товуш чикаради, яльи кайд килинган вакт иккилик частотаси билан товуш чикаради бу эса табиий равишда режага, номувофикдир. Шунинг учун икинчи режимини танлаймиз ва бошкарув байтининг битлари D3, D2, D1=x10=(010ёки110) га тенг. СТ2 хисоблагичнинг N2 модул хисоблаши F0/F2=100(DEC)=64(HEX) га тенг ва3<=N2<=255 ораликда жойлашган. Бундан келиб чикадики N2 ни хисоблашга битта кичик байт билан ёзиш мумкин, яьни битлар D5, D4=01га теникдир. N2 нинг бир байтли киймати учта унлик сонини жойлаштириш мумкин булмаган иккита тетрадага эга, шунинг учун N2нинг ёзилиши иккилик-уйлик кодида эмас, балки иккилик ва DO=O битда божарилиши керак. Айтилганлари кушиб СТ2ни бошкарув байтининг 2та булиши мумкин булган кийматини оламиз.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

HEX код |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

94 |

|

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

9C |

· СТ1 хисоблагичи. СТ2 хисоблагич бошкарув байтининг битлари D7,D6 га тенг. Унинг чикишидан вактда кечикиш О-чи ёки 1чи режимлардан маклантирилиши мумкун 1чи режимда GATE киришида мусбат сакраш билан хисоблагични ишга тушириш талаб килинади. О-чи режимда хисоблигнинг ишлаши учун, шу киришда сигнал GATE 1=1 D3,D2,D1 битлари эса-000 га тенг булиши керак 0-чи режимда булиш коэффициенти N1=(Т1/Т2) -1=15/1-1=14(DEC)=E(HEX). Бу сон СТ1 га битта кичик байт ёрдамида юкланиши мумкин, шунинг учун байтлар D5,D4=1 га тенг. N1=14 хисоблаш модулини DE(10000 1110) ун олтилик коди билан ёки 14 (00010100ВСD) иккилик - унлик коди билан ёзиш мумкин. Бу сон (вактда кечикиш) шундай параметр булиб хисоблашадики, у таймерга фойдоланувчи томонидан киритилади ва ун олтилик санок системасини билиш унинг мажбурият доирасидаги кирмайди. Шунинг учун таймерни яратувчига (ишлаб чикарувчига) мос равишда бошкарув байтининг бити D0=1 булган N1 сонини унлик сонларида урнитишни олдиндан булиши максадга мувофик булади. СТ1 учун бошкарув байтининг охирги натижаси куйидагича булади.

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

HEX код |

|

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

51 |

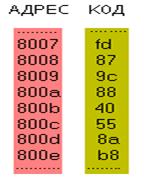

Келтирилган тайлер схемасининг ишга тушириш дастури:

;#### танланган режимда таймер

хисоблашгларини ишга туширишга тайёрлаш

mov al,51h; CT1 бошкарув байтини юклаш

out 83h,al; 83-адрес буйича

mov al,9ch ; СТ2 бошкарув байтини юклаш

out 83h,al; 83 адрес буйича

mov al,3eh ; СТО бошкарув байтини юклаш

out 83h,al; 83- адрес буйича

;#### хисоблагичларга Ni булиш коэффициэнтини ёзиш

;#### 0,2,3, режимларда хисоблагичларга охирги

;#### (ягона) Ni байтини ёзганда CL Ko импулслар хисоб бошлайди

mov al,14h ; СТ1 хисоблашига N1=14(ВСD!) ни ёзиш

out 81h,al; 81 адрес буйича

mov al,64h ; СТ2 хисоблашчга n2=100(DEC) ли ёзиш

out 82h,al; 81 адрес буйича

mov al,20h ;№=20000 (DEC)=4e20(HEX) кичик байтни ёзиш

out 80h,al; СТО хисоблагичга 80 адрес буйича

mov al,4eh ; энди булса -№ катта байтини

out 80h,al; уша адрес буйича

;#### таймер вактни санашни бошлади.

9- маъруза.

Интерфейс микросхемалари. ГТИ, буфер ригистрлар шина ташкил этувчилар.

Дастурли богланиш интерфейс ёки универсал (синхром) асинхром кабул килувчи узатувги (У(С)АПП ёки И (S)ART)МП ва кетма- кетлик форматидаги узок масофада жойлашган ташки курилмалар (Т.К.) орасида маълуматлр билан алмашишни ташкил килиш учун ишлатилади. Шу сабабли, УСАПП яна кетма-кетлик интефейси (IOS) деб хам аталади. УСАПП узатувги сифатида паралелл кодни кетма-кет кодга айлантиради ва уни алока линиясига узатади, кабул килувчи сифатида булса, тескари айлантиришни юзага келтиради. УСАПП узок масофада жойлашган курилмалар билан симпикс (мамуълотлар бир тамонлама харакат килади), полудуплекс (мамулотлар галма-галдан икки томонга узатиб, кабул килинади) ва дуплекс (бир вактида иккала тамонга мамулотлар алмашини) режимларда маълумотлар билан алмашиниш мумкин.

Расимда УСАПП нинг соддалаштирилган шартли белгиланиш, унинг микропроцесор системасига уланиш схемаси ва асинхрон режиимда ишлаётган кабул килувчининг кириш ёки узатувчининг чикишидаги типик битлар кетма-кетлиги келтирилган схемада МП курсатилмаган таймернинг СТО хисоблагичи (бошка булиши хам мумкин)маълумотлар алмашиши учун керак булган тезликни таъминлаб беради. Чикишлар вазифалари ; TXD- узатувчининг чикиши RXD-кабул килувчининг кириши, CLK-синхронизация частотасининг кириши, RxC -кабул килувчининг синхросигнал кириш ~CTS-кабул килувчи терминалнинг (узок масофадаги курилма ёки модем) тайёрлик инверс кириши. Оддий алока системаларида ~CTS киришни «ер билан» каттик равишда боглаш мумкин, узатувчига кабул килувчи «хар доим тайёр» деб хабар бериб куйиши керак, аммо унинг хакикатдан хам тайёрлигини аниклаш-дастурловчининг ишидир! Агар стандарт алока протоколи ишлатилса, масалан, RS-232 C. унда~ CTS кириш нолинги симдан узиб ташланиши керак. C/~D- «бошкарув маълумотлар» функционал кириш. Агар C/~D=0 булса, унда МП ва УСАПП маълумотлар байти билан алмашишади, агар C/~D=1 булса, унда бошкарув байтининг ёзиш ёки холатлар байтини укиш бажарилади. PCI нинг колган чикишларининг вазифалари PPI чикишларининг вазифаларига мос равишда ухшайди. Расимда келтирилган чикишлар унга узок булмаган масофатда жойлашган объектлар билан алока килиши учун етарлидир масалан компьютер билан ёки бошка МПлар билан.

Келтирилган расимда РСI адресларини хисоблаб тониш кийин эмас. Таймернинг ”микросхемани танлаш” киришига уланган дешифраторнинг нолинчи чикишидаги адреслар олиндан топилган. А4,А3,А2=111 (BIN) =7 (DEC) сигналлари ва дешифраторни ишга туширувчи А7,А6,А5,=100 (BIN) сигналларини бериш ёрдамида УСАПП нинг инверс кириши ~CS активлашади. Жадвалда турта булиши мумкин булган адреслардан иккитаси келтирилган PCI(A1=0)

|

АДРЕС ШИНА ЛИНИЯСИ |