ЎЗБЕКИСТОН АЛОҚА ВА АХБОРОТЛАШТИРИШ АГЕНТЛИГИ

ТОШКЕНТ АХБОРОТ ТЕХНОЛОГИЯЛАРИ УНИВЕРСИТЕТИ

Телекоммуникация технологиялари факультети

Рақамли СХЕМОтехника

5522000–Радиотехника йўналиши талабалари учун

лаборатория ишларини бажариш бўйича услубий қўлланма

Тошкент 2008

Муаллифлар:Ж. Ю. Юнусов, Р. П. Абдурахманов, Абасхонова Х.Ю..

«Рақамли СХЕМОтехника». / ТАТУ. 73 бет.Тошкент, 2008.

Рақамли схемотехника курсининг мақсади рақамли қурилмаларнинг тузилиш тамойиллари ва турли функционал қийинликдаги, яъни рақамли мантиқий элементлардан (МЭ) тортиб то микропроцессорларгача (МП) бўлган рақамли қурилмаларнинг ишлатилишини ўрганишдан иборатдир.

Ушбу лаборатория ишларини бажариш бўйича услубий қўлланма асосида талабалар рақамли схемотехника элементлари асосида турли қурилмаларни яратиш жараёнини ўрганадилар.

Услубий қўлланма “Телекоммуникация технологиялари” факультетининг илмий-услубий кенгашида кўриб чиқилиб, босмага тавсия этилган (“ 16 ” “ 09 ” “ 2008 ” йил № 64 сонли баённома)

Тақризчилар:

ЎзААА

РРТ бўлими бошлиғи

т.ф.н., доцент __________ Ю. К. Камолов

ТАТУ, «Телекоммуникация

узатиш тизимлари» кафедраси

мудири, т.ф.н., доцент __________ Р.И.Исаев

Муҳаррир: __________ К. А. Гаюбова

© ТОШКЕНТ АХБОРОТ ТЕХНОЛОГИЯЛАРИ УНИВЕРСИТЕТИ, 2008

КИРИШ

Рақамли схемотехника курсининг мақсади рақамли қурилмаларнинг тузилиш тамойиллари ва турли функционал қийинликдаги яъни рақамли мантиқий элементлардан (МЭ) тартиб то микропроцессорларгача (МП) бўлган рақамли қурилмаларнинг ишлатилишини ўрганишдан ташкил топади.

Рақамли схемотехника фани дастурга мос равишда назарий материаллар, назорат иши ва амалий ишларини ўз ичига олади. Назарий материалларнинг ўзлаштирилишни осонлаштириш учун ушбу ишда услубий кўрсатмалар, адабиётларга мурожаат, айрим холларда эса саволни кенгроқ ёритилиши ҳамда талабага жойларда мавжуд бўлган адабиётлардан бирини танлаб олиш имконини бериш учун бир нечта адабиёт номи кўрсатиб ўтилган.

Рақамли схемотехника курси икки қисмга бўлинган. Биринчи қисмда асосий диққатни унча қийин бўлмаган рақамли қурилмаларнинг структураси ва қуриш тамойилларига қаратилади. Биринчи қисмдан олинган билимларни бириктириш учун талабларга 3 саволдан иборат бўлган назорат иши берилади. Иккинчи қисмда эса юқори қийинликка эга бўлган МП ва МПТ (микропроцессор тизимлари)ни қуриш тамойиллари ва уларни ишлатилиш қоидалари кўриб чиқилади.

Мазкур услубий қўлланма ЭҲМда дастурлаштириш бўйича амалий малака ошириш учун ҳам мўлжалланган.

1 ва 2 – Лаборатория ишлари

МАНТИҚИЙ ЭЛЕМЕНТЛАРНИНГ ОДДИЙ МОДЕЛИ ВА ТИЗИМ ПАРАМЕТРЛАРИ

РАҚАМЛИ ЭЛЕМЕНТЛАРНИНГ ЧИҚИШ ҚИЙМАТЛАРИ

КОМБИНАЦИОН ЧИЗМАЛАРНИНГ СИНТЕЗИ

Ишдан мақсад: мантиқий элементларнинг оддий моделлари ва тизим параметрларини, ўлчов бирликларини, ва истеъмол қилиш қувватини, рақамли элементларнинг чиқиш қийматларини, комбинацион чизмаларнинг потенциал элементлар тизимидаги синтезини кўриб чиқиш ва уларнинг ишлаши хақида амалий тасаввурга ва малакавий билимларга эга бўлиш.

назариядан қисқача маълумотлар

Ҳар бир дискрет қурилманинг ҳатти-ҳаракати унга таъсир қилаётган 3-хил физик катталиклар билан аниқланади. Ушбу фанда кўриб чиқилаётган қурилмалар учун бу катталиклар қурилма киришидаги, чикишидаги ва унинг ичидаги кутблар потенциалидир.

Дискрет қурилмалар ишлашининг асосий хусусиятлари шундан иборатки, аниқ ажратилган вақт оралиқларида ушбу кириш, чиқиш ва ички ҳолат катталиклари доимий бўлади.

Ушбу вақт оралиқлари дискрет қурилманинг ишлаш тактлари дейилади. Ўзгарувчилар қиймати дискрет автоматларнинг ишлаши ва тузилиши билан фарқланади.

Дискрет автомат вақти деб 0 дан К гача оралиққа тактларнинг кетма-кет жойлаштирилишига айтилади. Шундай қилиб, ҳар бир вақт оралиғида автоматнинг кириш, чиқиш ва ички ўзгарувчилари турғун қийматга эга бўлар экан. Бу қийматларни автоматнинг кириш, чиқиш ва ички ҳолатлари дейилади.

Мантиқ илми (логика) тафаккур қонунлари ва фикрлаш формалари ҳақидаги фандир. Бу фаннинг математик шакли мантиқий алгебра бўлиб, у фикрлаш қонунлари асосида фикрлар орасидаги мантиқий боғланишларни ўргатади. Ҳар қандай айтилган фикрда ҳақиқат борлиги ёки йўқлиги (сохталик)ни аниқлаш масласи мантиқий алгебранинг ўргатиш соҳаси ҳисобланади.

Мантиқий алгебранинг амаллари факат иккита қиймат 0 ва 1 мавжудлигига асосланади. Айтилган фикр ёки берилган сигнал бор ва ҳақиқий бўлса, бундай сигналнинг қиймати 1 га тенг, агар айтилган фикр сохта ёки сигнал берилмаган бўлса, бундай сигнални қиймати 0 га тенг деб қабул қилинади.

Ишлаб чиқариш жараёнларини мантиқий бошқариш тизимларини тузишда бундай сигналлар ишчи ахборотлар деб юритилади.

Ишчи ахборотларнинг аргументлари ва уларнинг ўзаро боғланиш амалларини кўрсатувчи ифодалар мантиқий функциялар деб аталади.

Ахборотларнинг ўзаро боғланиш оддий ва мураккаб бўлганидек, мантиқий функциялар ҳам оддий ва мураккаб бўлади.

Мантиқий алгебранинг асосини оддий функциялар: мантиқий қўшув, кўпайтирув ва инверсия (инкор қилув) амаллари бажариш ташкил килади. қолган мураккаб функцияларнинг ҳаммаси шу учта оддий функциялар ва уларнинг комбинациялари асосида тузилади.

Мантиқий функцилар Y бир қатор мантиқий аргументлар X1 X2 Х3...Хn нинг ўзгариши ва ўзаро боғланишлари билан боғлиқ бўлади. Аргументлар фақат икки қиймати 0 ва 1 га эга бўлади.

Мантиқий функциялар тузишда қуйидаги мантиқий алгебра қонунларидан фойдаланилади. Ахборот ёки миқдор ва унинг инверсиясининг йиғиндиси 1 га тенг бўлади;

Х

= Х = 1 (1)

Х

= Х = 1 (1)

Дискрет автоматларнинг умумий модели деб қуйидаги талабларга жавоб жавоб берувчи мавхум автоматга айтилади.

-барча кириш ҳолатлар тўплами X={x1, x2… xn},

бу ерда n-автоматнинг киришлар сони;

-барча чиқиш ҳолатлар тўплами Z={z1, z2… zm}

бу ерда m-автоматнинг чиқишлар сони;

-барча ички ҳолатлар тўплами S= {s1, s2… s k}

-ўтиш функцияси δ, S (t=1)=қ δ [S (t), X (t)]

-чиқиш функцияси λ, Z (t)= λ [S (t), X (t)]

-автоматнинг бошланғич ҳолати S1 Є S

Агар δ ва λ функциялари Х ва S нинг бутун узунлиги бўйича аниқ бўлса, бундай автомат тўлиқ берилган автомат дейилади, акс ҳолда тўлиқ эмас.

Автоматнинг тасвиралниши учун унинг фаолият қоидаларига ва ички структурасига эга бўлиш керак. Ушбу тасвирлаш усуллари бир қанча ва уларнинг барчаси ўз имкониятларига ва фаолият чегараларига эгадир. Тасвирлаш усулларини танлаш биринчи навбатда автоматнинг тузилишига ва ишлашига боғлиқ.

Автоматнинг мураккаблиги унинг ички тузилишида ҳотира элементларининг, яъни ички ҳолатини сақлаб турувчи элементларнинг мавжудлиги билан ифожаланади. Комбинацион автоматларда бундай ҳотира элементларининг йўқлиги уларнинг фаолиятини ва таркибинитасвирлаш масаласини осонлаштиради. Автоматни тасвирлаш учун унинг кириш ва чиқиш ҳолатлари тўпламининг мутаносиблигини ҳисобга олиш керак ҳолос.

Агар автомат n-та кириш ва m-та чиқишга эга бўлса, у ҳолда n-та аргументга эга m-та боғлиқлик функциясини кўрсатсак бас:

Z1=λ1 (Х1, Х2… Хn)

Z2=λ2 (Х1, Х2… Хn) (2)

…

Zm=λm (Х1, Х2… Хn)

Ушбу m-та функциядан таркиб топган тизим аргумент ва функциялари иҳтиёрий қиймат қабул қиладиган автоматларни қуришда ишлатилади. Мисол учун аргументлари ва функциялари иккидан ошмаган автоматни кўриб чиқамиз, яъни:

Xi0=, 1 i=1, n учун (3)

Zi=0, 1, j=1, m учун (4)

Дискрет автоматларини ўрганиш ўзаро боғлиқ бўлган анализ ва синтез масалаларидан ташкил топади. КДА анализи 2 босқичда бажарилади. Аввал туркумдан чизманинг ишлаш мантиқиқига таъсир кўрсатмайдиган, мувофиқлаштириш ва ташкиллаштириш вазифаларини бажарувчи барча ёрдамчи элементларни чиқариб ташланади. Сўнг Z1… Zm функция туркумига бўйсунувчи мантиқий элементлар солиштирилади.

Синтез вазифаси анализнинг тескариси бўлиб, у ўз олдига мавжуд қоидалар асосида автоматнинг реал чизмасини қуриш масаласини қўяди. Умумий ҳолда КДА (n, m) қутбли қурилма кўринишида тасвирланади. Ушбу қурилма 2 ҳил усул билан тасвирланиши мумкин: ҳар бир функцияни бир чиқишли қурилма кўринишида қабул қилиш, яъни m (n, 1) қутбий қурилма кўринишида ва бутун тизимни кўп чиқишли қурилма кўринишида тасвирлаш.

Анализ ва синтез масалаларини ечиш КДАни ўзаро бирлашган элементлар туркумиданташкил топган қурилма кўринишида тасвирлашсиз тасаввур қилиб бўлмайди. Барча ҳолларда автомат ташкил топган элементлар туркумини аниқлаб олиш керак. Ундан ташқари КДАнинг ишлаш жараёнида юз берадиган математик ҳодисаларни аниқлаб олиш керак.

КДА ишлаш жараёнини тасвирлаш учун Буль функциясидан фойдаланилади. Икки ўзгарувчидан ташкил топган функция Буль функцияси дейилади. Унда функция ва унинг аргументлари 0 ва 1 қийматларига эга бўлади. Буль функцияси ҳолатлар жадвали, Карно картаси ва ҳоказолар ёрдамида тасвирланиши мумкин. Табиийки, суперпозиция усули ёрдамида исталган Буль функциясини ҳосил қила оладиган функциялар тўплами борми деган савол туғилади. Математик мантиқда исбот қилинганки, агар Буль функциялар тизими қуйидаги функцияларни ўз ичига олса, у ҳолда тизим функционал тўлиқ дейилади:

I. f1= x1* x2; f1=x 1 x2; fg = x;

II. f2 =x1* x2; (5)

III.fg=x1 v x2.

Буль функциясининг техник кўриниши, шу функция асосида маълумотни чиқариб берадиган комбинацион қурилма ҳизмат қилади. қурилмада 0 ва 1 сигналларига мос келадиган ток ва кучланишлар сатҳи функциядаги 0 ва 1 константаларининг техник кўринишига мос келади. Оддий мантиқий амаллар мантиқий элементлар ёрдамида бажарилиши мумкин.

Мантиқий элементлар турларини аргументлар сонига тенглаштириш мумкин.

Мантиқий элементлардан ташқари Буль функциялари реле-контакт қурилмаларида ҳам бажарилиши мумкин. Бу ҳолда функция аргументлари вазифасини ушбу реле контактлари бажаради. Мантиқий амаллар эса контактларнинг уланиш қоидаларидан келиб чиқади. Контактларнинг параллел уланиши дизъюнкция амалига, кетма-кет уланиши эса конъюнкция амалига мос келади.

Бир чиқишли КДА синтези

Бир чиқишли КДА синтезининг вазифаси (n, 1) қутбий қурилма синтези вазифасига мос келади. Аввал, y=f (x1,x2,…,xn) Буль функцияси олиниб, унинг тўлиқ формаси олинади. Сўнг бирор бир усул билан минималлаштирилади (қисқартирилади). Шундан сўнг, чиқишда керакли функцияни берувчи, «И-НЕ» базисга ўтказилган қурилма чизмасини тузишга киришилади.

Кўп чиқишли КДА синтези

Кўп чиқишли КДА синтези – бу (n, m) қутбий қурилма синтезидир, ва у m функциялар тизими билан тасвирланади. Агар ушбу функциялар синтези масаласини ҳар бир функция синтези масаласига алмаштирсак, (n, m) қурилма синтези (n, 1) қурилма синтезидан асло фарқ қилмайди. (n, m) қурилма синтезининг бир қанча усуллари мавжуд, лекин улар оптимал қарорга олиб келмайди. Барча усуллар асосида бутун бир функцияни ёки унинг бир қисмини иккинчи функция яратиш учун ишлатиш қонуни ётади. Масалан қуйидаги функциялар берилган бўлсин:

f1=![]() ;

(6)

;

(6)

f2= ![]() ; (7)

; (7)

f3=![]()

![]() .

(8)

.

(8)

Табиийки, функцияни қуйидаги усулга келтириш мумкин:

f2=

f1![]()

![]() (9)

(9)

f3=

f2![]() (10)

(10)

Бу эса қурилмани анча ихчамлашишига олиб келади. Кўп чиқишли КДА лар синтезида Карно картасининг ишлатилиши қулай ва мақсадга мувофиқдир.

f1=![]() (11)

(11)

f2=![]() (12)

(12)

f3=![]() (13)

(13)

лаборатория ишини бажариш учун вариантлар

Қуйидаги 1.1-жадвалда лаборатория ишини бажариш учун вариантлар келтирилган.

1.1-жадвал.

|

Вариант |

f 1 |

f2 |

f3 |

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 |

0,1,3,5,(7,12,13) 1,2,6,7,11,(12,13) 2,3,5,8,(10,13,14) 3,4,5,6,(7,8,9) 4,5,6,(7,8,9,10) 5,6,7,8,9,10,(11) 6,7,8,9,(10,11,12) 7,8,9,10,11,(12,13) 8,9,10,(11,12,13,14) 7,8,9,10,11,12,(13,14) 2,3,4,(5,6,7,8) 1,2,3,(4,5,6,7,8) 0,1,2,3,(4,5,6) 0,2,4,6,8,(10,12) 2,4,6,8,(10,12,14) 1,3,5(7,9,11,14) 3,5,7,9,11,(15) 0,1,2,3,11,(12,13) 0,1,2,3,(4,5,6) 0,1,2,(3,7,8,9) 0,1,2,3,8,(9,10) 0,1,3,(9,10,11) 0,1,2,3,10,11,(12) 0,1,2,3,(12,13,14) 0,1,3,13,(14,15) 2,4,6,8,9,(10,11) 2,4,6,(8,10,11) 2,4,(8,12,13) 2,4,(6,8,12,13,14) 1,3,5,7,(9,11,13) |

6,7,8,9,10,(11) 10,11,12,(13,14,15) 9,10,(11,12,13,14) 8,9,(10,11,12,13) 7,8,9,10,(11,12) 6,7,(8,9 ,10,11) 5,6,(7,8,9,10) 4,5,6,7,(8,9) 3,4,5,(6,7,8) 2,3,4,5,6,(7) 1,2,3,(4,5,6) 0,1,(2,3,4,5) 0,1,2,(3,4,6) 1,2,3,4,(5,6) 2,3,4,(5,6,7) 3,4,5,6,(7,8) 4,5,7,(8,9) 5,6,7,(8,9,10) 6,7,8,9,(10,11) 7,8,9,10,(11,12) 8,9,(10,11,12,13) 9,10,11,12,(13,14) 10,11,12,(13,14,15) 0,2,4,6,(8,10) 2,4,(6,8,10,12) 4,6,8,(10,12,14) 1,3,5,6,(9,11) 3,5,7,(9,11,14) 5,7,9,11,(12,15) 0,2,(5,8,12,15) |

2,4,6,(7,8) 0,1,2,3.(4) 0,1,2,(3,5) 2,3,4,(5,6) 3,4,5,(6,7) 4,5,(6,7,8) 5,6,7,(8,9) 6,7,8,9,(10) 7,8,(9,10,11) 8,9,10,11(12) 9,10,11,(12,13) 10,11,(12,13,14) 11,12,13,(14,15) 0,2,4,6,(8) 2,4,6,(8,10) 4,6,(8,10,12) 6,8,10,(12,14) 1,3,(5,7,9) 3,5,7,9,(11) 5,7,(9,11,13) 7,9,11,(13,15) 0,1,(3,5,6) 0,1,4,(5,8) 1,2,7,(8,9) 1,2,8,(9,10) 1,2,(9,10,11) 1,2,10,(11,12) 1,2,11,(12,13) 1,2,(12,13,14) 3,5,(7,8,10) |

Мисол тариқасида 1.1-жадвалининг 30-вариантини ишлаб чиқамиз.

f1 = 1,3,5,7,(9,11,13); f2 =0,2,(5,8,12,15); f3 = 3,5,(7,8,10).

1) Ҳолатлар жадвали

2) СНДФ

1.2-жадвал

|

№ |

X3 |

x2 |

x1 |

x0 |

f1 |

f2 |

f3 |

|

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

0000111100001111 |

0011001100110011 |

0101010101010101 |

010101010~0~0~00 |

10100~00~000~00~ |

0001010~~0~00000 |

f1 = x0x1x2x3Vx0x1x2x3Vx0x1x2x3V

Vx0x1x2x3V x0x1x2x3Vx0x1x2x3Vx0x1x2x (14)

0 0 0

f2 = x0x1x2x3Vx0x1x2x3V

Vx0x1x2x3Vx0x1x2x3Vx0x1x2x3Vx0x1x2x3 (15)

0 0 0 0

f3 = x0x1x2x3Vx0x1x2x3V Vx0x1x2x3Vx0x1x2x3Vx0x1x2x (16)

0 0 0

3) Вақт диаграммаси

х0![]()

![]()

__x1____________________________________________________

![]()

![]()

__x2____________________________________________________

![]()

![]()

![]() __x3____________________________________________________

__x3____________________________________________________

![]() __f1____________________________~___~___~_______________

__f1____________________________~___~___~_______________

![]() __f2_________________~________~_______~____________~____

__f2_________________~________~_______~____________~____

![]() __f3_______________________~_~___~______________________

__f3_______________________~_~___~______________________

4) Карно картаси

X1________

X0________

|

|

|

1 |

1 |

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

X2 X3 f1=

X0X3

![]()

![]()

|

f2 =X0X2

X3 X2 X3 |

|

|

1 |

||||

|

|

~ |

|

|

||||

|

|

|

~ |

|

||||

|

~ |

|

|

|

1.1-расм. КДА синтезининг босқичлари.

Ҳисобот қуйидагилардан ташкил топган бўлиши керак:

1. Берилган функцияларнинг синтези.

2. Бир ва кўп чиқишли КДА чизмаси, дешифратора и мультиплексора, чизмалари.

3. Берилган чизманинг вақт диаграммаси ва сигналлар қийматлари.

4. Эксперемент ёрдамида топилган қийматлар.

5. Ҳулосалар.

Назорат саволлари

1. Буль функциялари деб қандай функцияларга айтилади?

2. Функционал тўлиқ функция деб қандай функцияларга айтилади?

3. Дискрет қурилмалар (КДА) лар анализи ва синтези мақсади нималардан иборат?

4. Тўлиқ берилган автомат деб нимага айтилади?

5. Минимизация асосида қандай мантиқий амал бажарилади?

6. Синхрон ва асинхрон автомат деб қандай автоматларга айтилади?

7. КДА ҳолатлар сони қандай топилади?

8. КДА ни нима учун синтез қилиш вазифаси қўйилган?

3 ва 4 – Лаборатория ишлари

Комбинацион дискрет автоматларнинг «И – НЕ», «ИЛИ-НЕ» базисларидаги синтези

Ишдан мақсад: Комбинацион дискрет автомат схемаларини «И – НЕ», «ИЛИ-НЕ»базисларидаги синтезини кўриб чиқиш ва уларнинг ишлаши хақида амалий тасаввурга ва малакавий билимларга эга бўлиш.

назариядан қисқача маълумотлар

Комбинацион дискрет автомат схемаларини И, ИЛИ, НЕ базисдан бир турдаги «И-НЕ» ёки «ИЛИ-НЕ» мантиқий элементлар базисда қуриш асосий мақсадни амалга оширишдан иборатдир. Ушбу жараённи амалга ошириш учун «И-НЕ» базисга ўтказиш кетма-кетлигини кўриб чиқиш лозимдир. Қуйидаги функцияларни «И-НЕ» базисга ўтказиш мисолида амалга оширилади.

функцияни «И – НЕ» базисига ўгириш

![]() ,

,

![]() ,

,

![]() (17)

(17)

Маьлумки, Шеффер функцияси учун қуйидаги тенгликлар мос келади:

Ш ![]() (18)

(18)

Ш ![]() (19)

(19)

Ш ![]() (20)

(20)

Ш ![]() (21)

(21)

Функцияни «И-НЕ» базисига ўгириш учун Де Морган қоидаси:

Ш ![]() (22)

(22)

![]() (23)

(23)

![]() (24)

(24)

![]() (25)

(25)

![]() (26)

(26)

![]() (27)

(27)

функцияни «ИЛИ – НЕ» базисига ўгириш

![]() ,

,

![]() ,

,

![]() (17)

(17)

П ![]() (28)

(28)

П ![]() (29)

(29)

П ![]() (30)

(30)

П ![]() (31)

(31)

![]() (32)

(32)

![]() (33)

(33)

![]() (34)

(34)

![]() (35)

(35)

![]() (36)

(36)

![]() (37)

(37)

Ҳисобот қуйидагилардан ташкил топиши керак:

1. Берилган вариант бўйича умумий базисда бажарилган КДА синтези (1-иш вариантини қаранг).

2. КДА ни «И- НЕ», «ИЛИ-НЕ» базисларига ўтказиш.

3. КДА нинг «И-НЕ», «ИЛИ-НЕ» базисларидаги чизмалари.

4. Ҳулосалар.

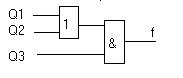

2.1-расм. КДАнинг «И-НЕ» ва «ИЛИ-НЕ» базисидаги схемаси

Назорат саволлари:

1. Буль алгебрасининг функция ва амаллари.

2. Буль алгебрасининг қонун ва қоидалари.

3. Мантиқий чизмаларнинг тасвирланиш усуллари.

4. «И-НЕ» базисига ўгириш қоидаси.

5. «ИЛИ–НЕ» базисига ўгириш қоидаси.

5, 6, 7 – Лаборатория ишлари

дешифраторлар ва мультиплексорлар синтези

ишдан мақсад: Дешифраторлар, шифраторлар ва демультиплексор мультиплексорлар каби комбинацион дискрет автоматларнинг ишлаш тамойиллари, уларни қуриш ва ишга тушириш масалалари ҳақида амалий кўникма ва малакавий билимлар орттириш.

Назариядан қисқача маълумотлар

дешифраторлар синтези

Дешифратор киришдаги иккилик кодни чиқишнинг шундай актив сигналига айлантиради-ки, унинг номери киришдаги иккилик коднинг ўнлик эквивалентига тенг бўлади. Тўлик дешифраторда чиқишлар сони m=2n га ўнлик дешифраторда эса m<2m. Тўлиқ дешифратор аниқлашига 2i чиқиш мантиқий функцияларни ишлаб чиқариб, улар n кириш ўзгарувчиларининг ҳаммасида аниқлангандир. n=2 ва m=4 га тенг дешифраторни кўриб чиқамиз. Бундай дешифратор "2 дан 4" уни ОЕ чиқишларига рухсат бериш кириши билан тўлғизамиз. Тўғри киришлар киришлардаги актив сигналга 1 сатх, 0-эса инверсияларга таълуқлидир. Ушбу аниқликка асосан холатлар жадвалини тўлдирамиз, бу ерда Х иҳтиёрий қийматга тенгдир.

5.1-расм. Дешифратор кириш ва чиқишларининг белгиланиши.

Карно картаси у-0 чиқиш ва 3 та кириш ўзгарувчиларига асоси қуйидаги кўринишга эгадир. Келтирилган чиқиш учун фақат бир жойда 1 бўлганлигидан, у0 чиқиш мантиқий функция қуйидаги кўринишга эгадир.

5.2-расм. Дешифратор ҳолатларининг Карно картаси.

У0=ОЕ~a1*~a0. Қолган учта тенглама ҳам юқоридагига ўхшаб аниқланади. Аниқланган уi тенгламалр икки марта инверсиялаш аксиомасига асосан И-НЕ базисига ўтказилади. Y0= ~~(OE*~a1*a0). Аниқланганга 5.3-расмдаги схема мос келади.

5.3-расм. Дешифратор синтезининг босқичлари.

Дешифратор ишининг вақт диаграммалари асосида (Е) схема учун тушунтирамиз. ~OE=1схема учун мавжуд даврида расмдаги И-НЕ (0,3) бўлади, ва а0 ва а1лар боғлиқ бўлмаган холда чиқиш қийматлари ~yj=1, yj=0, улар 5.3-расмда аниқ кўрсатилган. T0,t1, ва t2,t3 вақт оралиғида чиқишлар "таъқиқланган", яъни yi тўғри чиқишларида пассив сатх "0", инверсия чиқишларида эса пассив "1"га тенг. t1,t2 интервалда ~OE=0(OB=1) сигнали ва унинг yi қиймати фақат а1,а0 ўзгарувчиларга боғлиқ. Агарда киришда А1,А0=10 код бўлса, унга ўнлик икки мос келади ва иккинчи И-НЕ элемент киришларида мантиқий "1" у2 диаграмма кўриниб турибди. ОЕ инвентор ишлатилиши мумкин. Бу ерда ОЕ=1 га тенг, қачонки, ~OE1=~OE2=0 ва ОЕ3=1. Бундай схема "3 ва 8" 1533ND7 (555ND7) турдаги дешифраторларда қўлланилади, уларнинг шартли белгиланиши 14 ва 15 расмларда келтирилган.

5.4-расм.

Дешифраторнинг схематик кўриниши.

Дешифраторлар ҳисоблаш техникасида кенг қўлланиб келинади. Улар бир неча ташқи қурилмаларни танлаш, маълумотларни улар ва микропроцессорлар орасида алмашиши ташкил қилади. Бу учун хам ai киришларга ташқи қурилмалар адреси берилади, киришлар эса адрес киришлар дейилади.

Шифраторлар синтези

Шифратор мавқеъсиз бўлади, агарда фақат битта хақиқий сигнал узатишга рухсат этилса, ва мавқеълик бўлиши мумкин, агарда бирданига бир неча сигналларни киришга рухсат этилса, мавкеъсиз Ш ўнлик рақамли хақиқий киришни номерини чиқишга унинг иккилик эквивалентга қайта ишловчи курилмага айтилади. Мавқеъсиз "4 дан 2" шифратор учун хажмлар жадвали (20 расм) қуйидаги кўринишга эга.

Шифраторларнинг кўриниши ва шартли белгиланиши 23 расмда келтирилган.

5.5-расм.

Мультиплексор ва Демультиплексорлар синтези

Сигнални ахборот киришдан чиқишларнинг бирига узатувчи, қабул қилувчи чиқишларнинг номер эса адрес киришларга берилаётган иккилик коднинг ўнлик эквивалентига тенг қурилмалар демультиплексор (ДМ) деб аталади. ДМ сифатида дешифратор ишлатилиши мумкин бўлиб, унинг ОЕ сигнали ўрнини Х информатцион сигнал берилади. Масалан, агар киришларга а1а0=10(BIN)=2(DEC) берилса, у холда Хсигнал У2 чиқишда пайдо бўлади. Қолган чиқишларда эса yi=0. 16 расмда ДМ "1 да4" ДМ ва унинг механик аналоги келтирилган.

5.6-расм. Демультиплексор ва унинг механик аналоги.

5.1-жадвал.

Мультиплексор

деб n ахборот киришдаги сигналлардан бирини ягона чиқишга узатувчи

узатилаётган киришда адреснинг ўнлик эквивалент иккилик адресига ni тенг қурилмага

айтилади. Агарда ОЕ чиқишга рухсат бериш кириши мавжуд бўлса, у холда

киришда "0" холат чиқиши пассив холатга (5.1-жадвалнинг охирги қатори)

ўтказади. "4 дан

1" мультиплексорни кўриб

чиқамиз, у 4 информатцион кириш ва

lod4=2 адрес киришга эгадир.

5.1-жадвал.

Унинг умумий мантиқий тенгламаси қуйидаги кўринишга тенгдир.

Y=OE(x0*~a1*~a0+x1*~a1*a0+….) (38)

Келтирилган ифоданинг ўнг томонидагиларга икки марта инверлаш ва ўз-ўзига ўтиш аксиомаларни қўллаб аниқлаймиз.

Y=~(OE x0~a1*~a0+….+OE*x3*a1*a0) (39)

5.7-расм. Мультиплексорнинг механик аналоги.

(17) ифодага мос схема 5.7-расмда

келтирилиб, унинг шартли белгиси ва механик аналоги кўрсатилган.

лаборатория ишини бажариш учун вариантлар

5.2-жадвал. дешифраторлар синтези

|

№ |

код |

№ |

код |

№ |

код |

№ |

код |

№ |

код |

|

1-16 |

1248 |

4-19 |

1235 |

7-22 |

1245 |

10-25 |

1225 |

13-28 |

1234 |

|

2-17 |

1237 |

5-20 |

1247 |

8-23 |

1136 |

11-26 |

1227 |

14-29 |

1135 |

|

3-18 |

1236 |

6-21 |

1246 |

9-24 |

1226 |

12-27 |

1228 |

15-30 |

1136 |

5.3-жадвал. мультиплексорлар синтези

|

№ |

кириш |

№ |

кириш |

№ |

кириш |

№ |

кириш |

№ |

кириш |

|

1 |

4 |

4 |

5 |

7 |

6 |

10 |

7 |

13 |

8 |

|

2 |

9 |

5 |

10 |

8 |

11 |

11 |

12 |

14 |

13 |

|

3 |

14 |

6 |

15 |

9 |

16 |

12 |

2 |

15 |

3 |

5.4-жадвал. демультиплексорлар синтези

|

№ |

чиқиш |

№ |

чиқиш |

№ |

чиқиш |

№ |

чиқиш |

№ |

чиқиш |

|

16 |

4 |

19 |

5 |

22 |

6 |

25 |

7 |

28 |

8 |

|

17 |

9 |

20 |

10 |

23 |

11 |

26 |

12 |

29 |

13 |

|

18 |

14 |

21 |

15 |

24 |

16 |

27 |

2 |

30 |

3 |

Ҳисобот қуйидагилардан ташкил топган бўлиши керак:

1. Шахсий вариантга кўра дешифратор хақида бошланғич маълумот.

2. Дешифраторнинг босқичма-босқич бажарилган синтези.

3. Дешифратор схемаси. (И-НЕ, ИЛИ-НЕ базисларида).

4. Шахсий вариант бўйича мультиплексор ёки демультиплексор хақида бошланғич маълумотлар.

5. Мультиплексор ёки демультиплексорнинг босқичма-босқич бажарилган синтези.

6. Мультиплексор ёки демультиплексорнинг схемаси. (И-НЕ, ИЛИ-НЕ базисларида).

Назорат саволлари

1. Тўлиқ дешифратор деганда қандай қурилма тушунасиз?

2. Тўлиқ шифратор деганда қандай қурилма тушунасиз?

3. Тўлиқ мультиплексор деганда қандай қурилма тушунасиз?

4. Тўлиқ демультиплексор деганда қандай қурилма тушунасиз?

5. Шифратор ва дешифраторларнинг фарқи нимада?

6. Мультиплексор ва демультиплексорларнинг фарқи нимада?

7. Бир чиқишли ва кўп чиқишли КДА ларга мисол келтиринг.

8. Бир чиқишли ва кўп чиқишли КДА ларнинг фарқи нимада?

9. Буль алгебрасининг функция ва амаллари.

10. Буль алгебрасининг қонун ва қоидалари.

8, 9 – Лаборатория ишлари

назорат схемалари ва мажоритар элементлар

Ишдан мақсад: Сумматорлар, назорат схемалари ва мажоритар элементларнинг ишлаши, қуриш тамойиллари ва синтезини бажариш бўйича амалий кўникма ва малакавий билимларга эга бўлиш

Қисқача назарий маълумотлар

Жамлагич n-разрядли Х=(Х(n-1), ....X0) ва Y=(y(n-1),....y0) кодларни арифметик қўшишни амалга оширувчи қурилмага айтилади. Икки бир разрядли иккилик сонларнинг қўшиш қоидаси

0 (+) 0 = 0

0 (+) 1 = 1 (+) 0 = 1

1 (+) 1 = 0 юқори разрядга узатилади

Учта бир разрядли сонларнинг қўшиши қуйидаги амалга оширилади.

0 (+) 0 (+) 0 = 0

0 (+) 0 (+) 1 = 1

0 (+) 1 (+) 1 = 0 1 юқори разрядга узатилади

1 (+) 1 (+) 1 = 1 1 юқори разрядга узатилади.

Келтирилган қоидага асосан тўлиқ жамлагич мантиқий функцияси қуйидагича:

Жамлагич разряд натижаси

c(i+1) = xi*yi + xi*ci + yi*ci. (40)

Орттирма

si = ~yi(xi (+) ci) + yi~(xi (+) ci) =

yi (+) (xi (+) ci) = yi (+) xi (+) ci. (41)

Бир разрядли тўлиқ жамлагичнинг (18) ва (19) тенгламаларга мос схема ва шартли белги 21 расмда келтирилган.

8.1-расм. Бир разрядли тўлиқ жамлагич

схемаси

лаборатория ишини бажариш учун вариантлар

8.1-жадвал.

|

№ вариант |

Разрядлар сони |

Буйруқлар рўйхати |

Операнд коди |

|

|

А |

В |

|||

|

1-16 |

2 |

А + В; А – 1; В + 1; Ā. |

01 |

11 |

|

2-17 |

3 |

А – В; А – 1 ; В – 1 ; А. |

010 |

011 |

|

3-18 |

4 |

А+В; А – 1; А – В – 1; В. |

0101 |

0111 |

|

4-19 |

2 |

А – В; В – 1; А+В+1; Ā. |

10 |

11 |

|

5-20 |

3 |

А+В; А+1;А – В+1; В. |

101 |

010 |

|

6-21 |

4 |

А – В; А – 1; А+В – 1; А. |

0111 |

0011 |

|

7-22 |

2 |

А+В; В+1;А – В – 1; В. |

11 |

01 |

|

8-23 |

3 |

А – В; А – 1; А+В+1; Ā. |

011 |

101 |

|

9-24 |

4 |

А+В; А+1;А – В +1; В. |

1111 |

0010 |

|

10-25 |

2 |

А – В; В+1;А+В – 1; А. |

11 |

10 |

|

11-26 |

3 |

А+В; А+1; А – В – 1; В. |

111 |

101 |

|

12-27 |

4 |

А – В; В – 1; А+В+1; Ā. |

0101 |

1010 |

|

13-28 |

2 |

А+В; А – 1; А+В – 1; В. |

01 |

01 |

|

14-29 |

3 |

А – В; В+1;А – В +1; Ā. |

110 |

011 |

|

15-30 |

4 |

А+В; А+1;А-В – 1; В. |

0111 |

0110 |

Ҳисобот қуйидагилардан ташкил топган бўлиши керак:

- Шахсий вариантга кўра сумматор хақида бошланғич маълумот.

- Сумматорнинг босқичма-босқич бажарилган синтези.

- Сумматор схемаси. (И-НЕ, ИЛИ-НЕ базисларида).

Назорат саволлари

1. Сумматор (жамлагич) ларга таъриф беринг.

2. Сумматор (жамлагич) ларнинг қандай турлари мавжуд?

3. Назорат схемаларига таъриф беринг.

4. Мажоритар элементларга таъриф беринг.

5. Жамлагичлар қандай амалларни бажаради?

6. Жамлагичларда қўшиш ва айириш амаллари қандай бажарилади?

7. Назорат схемаларида амал бажариш вақти қандай аниқланади?

8. Мажоритар элементни назорат схемасидан фарқи нимада?

10, 11 – Лаборатория ишлари

КЎП ТАКТЛИ ДИСКРЕТ АВТОМАТЛАРНИНГ СИНТЕЗИ

Ишнинг мақсади: кўп тактли дискрет автоматларни бистабил ячейкалар ва улар асосида қуриладиган мураккаброқ триггерлар мисолида ишлаш асосларини ва қуриш услубларини ўрганиш. Уларни синтезлаш бўйича амалий кўникма ва малакавий билимларга эга бўлиш.

Назариядан қисқача маълумотлар

Рақамли қурилмаларда ахборотларни сақлаш учун триггер ишлатилади. Триггер элементар эслаб қолувчи бистабил ячейка (БЯ) ва бошқариш схемасидан тузилган элементардан иборат автоматдир.

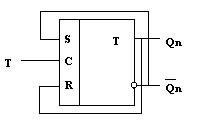

Триггернинг умумий схемаси 10.1-

расмда келтирилган. ![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

БЯ

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Бошқарув схемаси

Sy

f1 Q

Xı

![]() Xn

Xn

![]() Cı

Коммут.

Cı

Коммут.

![]() Cm :

: кириш.

Cm :

: кириш.

f2![]()

![]()

![]() Vı

Vı

![]() . Q

. Q

![]()

![]() Vk

Vk

Ry

Ry

10.1 – расм. Триггернинг умумий схемаси.

Хı, . . . ,Хn - ахборот киришлари; Сı, . . . , Сm- синхронизация киришлари, Vı, . . . , Vk – бошқарув киришлари;Sy,Rу ўрнатувчи киришлар; f1, f 2 – БЯнинг ахборот киришлари; Q (тўғри) ва ¯Q (тескари)–чиқишлар.

Дастурлаштириладиган универсиал триггерларда коммутация киришлари ташқи уланишлар учун ишлатилади.

Триггерлар мантиқий фаолияти ва ахборотни ёзиш усули бўйича тасниф қилиниши мумкин.

Мантиқий фаолияти бўйича триггерлар RS, JK, T, D, DV, TV ва комбинация асосида тузилган турларга бўлинади.

Ёзиш усули бўйича асинхрон ва синхрон триггерлар мавжуд. Асинхрон триггерларнинг ҳолатлари ахборот кириш сигналлари асосида ўрнатилади. Синхрон триггерларнинг холатлари ахборот сигнали асосида синхрон (такт) С сигнали узатилган вақтда ўрнатилади.

Триггерлар такт сигналининг сонига қараб бир тактли ва кўп тактли бўлиши мумкин.

Триггерлар такт сигналини қабул қилиши бўйича сигнал даражаси (қиймати) ва сигнал фронти билан бошқариланадиган турларга бўлинади. Биринчи тур триггерларда сигналнинг маълум бир қиймати триггернинг бир ҳолатини , сигналнинг бошқа қиймати эса триггернинг иккинчи (биринчи ҳолатига тескари) ҳолатини ўрнатади. Иккинчи тур триггерларнинг ҳолати такт сигналарини 1 дан 0 га (ёки 0 дан 1 га) ўтиш даврида ўрнатилади.

Сигнал даражаси билан бошқариланадиган триггерлар бир поғонали ва кўп поғонали бўлади. Бир поғонали триггерлар битта қисмдан (каскаддан) тузилган бўлиб, такт сигналининг келиши билан янги ҳолатга ўтадилар. Икки поғонали триггерлар кириш ва чиқиш каскадларидан тузилган бўлиб, олдин кириш каскади, кейин чиқиш каскади ўз ҳолатларини ўзгартирадилар. Кўп поғонали триггерларнинг ишончлиги ва ҳолатларини тўғри ўрнатиши бўйича бир поғонали триггерларга нисбатан юқоридир.

Триггернинг параметрлари қаторига ишлатилган мантиқий элементларнинг қуйидаги параметрларини киритиш мумкин: Кбр – кириш бўйича бирлаштириш коэффициенти; Кбў – чиқиш бўйича бўлиниш коэффициенти, «0» ва «1» сигналларининг даражаси (қиймати), кириш ва чиқиш токлари ва ҳ.з.

Триггерларнинг юқорида келтирилган параметрлардан ташқари қуйидаги махсус параметрлари мавжуд:

Кириш сигналининг минимал узунлиги

k

tи = ∑ tзр, (42)

iқ1

бу ерда k – кириш сигналининг нечта элементдан ўтишини кўрсатади, tзр – сигнални битта элементдан ўтиш вақти.

Триггер ҳолатини ўзгартиришга кетадиган вақт

m

tз.пер=∑ tзр (43)

i=1

бу ерда m - маълум триггергача бўлган элементлар сони.

Триггернинг характеристик функцияси

Qn=ı = f (Xn ,Qn) (44)

бу ерда Qn ва Qnқ1 триггернинг n ва nқ1 дискрет вақтлардаги ҳолати, Xn – кириш сигналарининг n дискрет вақтдаги қийматлари.

Триггерлар маълум бир кириш сигналари асосида ўз холатларини қуйидагича ўзгартиришлари мумкин Qn →Qn=ı :

0→0 , 0→1 , 1→0 , 1→1.

Триггер фаолиятини характеристик функция ва ўтиш жадвали билан ифодалаш мумкин. Ўтиш жадвалида триггернинг кириш сигналлари, ички холатлари ва чиқиш сигналларининг қийматлари кўрсатилади.

Триггерлар асосида регистрлар, ҳисоблагичлар ва турли хотира элементлари қурилади.

Ушбу услубий қўлланмади кенг тарқалган оддий триггерлар келтирилган.

Талабалар махсус функция асосида ишлайдиган триггерларни синтез қилишлари керак.

Структурали синтезнинг каноник усули асосида триггернинг синтез масаласи триггернинг бошқарув комбинацион схемасини синтез қилиш масаласига айлантирилади. Ушбу ҳолда триггернинг чиқиш сигналлари ва БЯ нинг кириш сигналлари (f1, f2) триггернинг кириш сигналлари орқали ифодаланади.

Бистабил ячейкали хотира

Бистабил ячейканинг ишлаши 10.1–ўтиш жадвали билан ифодаланади.

10.1–жадвал

|

f1 |

f2 |

Qn=ı |

|

0 0 1 1 |

0 1 0 1 |

× 1 0 Qn |

БЯ f1=f2=1 сигналида олдинги ҳолатини сақлаб қолади, f1=0 ва f2=1 бўлганда бир (1) ҳолати ўрнатилади, f1=1 ва f2=0 бўлганда ноль(0) ҳолати ўрнатилади, f1=f2=0 комбинацияси таъқиқланган ва ушбу сигналлар учун ноаниқлик ҳолати (х) кўрсатилган.

БЯ характеристик функциясини Карно картаси ёрдамида топамиз (10.2-расмга қаранг).

![]() f1

f2

f1

f2

![]()

|

×

|

0 |

0 |

Qt-1 |

||

|

×

|

0 |

|

|

10.2 – расм. БЯ учун Карно картаси.

Карно картасида 1 ва х катакларни 10.2–расмда кўрсатилгандек, бирлаштириб характеристик функцияни топамиз.

Qn=ı = f1 V f2Qn. (45)

Топилган функциядан икки мартта инверсия олиб И-НЕ базисига ўтамиз.

![]()

![]() Qn–ı = f1 V f2Qn= f1∙ f2Qn (46)

Qn–ı = f1 V f2Qn= f1∙ f2Qn (46)

|

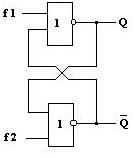

БЯнинг И-НЕ ва ИЛИ-НЕ базисидаги схемалари 3-расмда келтирилган

|

![]()

![]()

![]()

![]() а) б)

а) б)

![]()

![]() 10.3-расм.

И-НЕ (а) и ИЛИ-НЕ (б) базисларидаги БЯ схемалари.

10.3-расм.

И-НЕ (а) и ИЛИ-НЕ (б) базисларидаги БЯ схемалари.

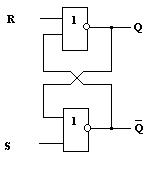

RS – триггер

Асинхрон RS-триггер иккита киришли триггер бўлиб, бошқарув ҳар бир кириш орқали алохида амалга оширилади. Сигнал S киришига узатилганда триггер бир (1) ҳолатига ўрнатилади, R киришига сигнал келганда триггер нол (0) ҳолатига ўтади, иккала киришига сигнал (1) узатиш таъқиқланади, чунки триггер аниқ бир холатни қабул қилмайди (ноаниқлик ҳолати). RS-триггернинг фаолияти 10.2-ўтиш жадвали билан тасвирланган.

10.2-жадвал

|

S |

R |

Qn=ı |

|

0 1 0 1 |

0 0 1 1 |

Qn 1 0 Х |

10.2-жадвалдан кўриниб турибдики, 0 қийматли кириш сигналларида триггер аввалги (Qn) ҳолатини сақлаб қолмоқда.

RS-триггери фаолиятини қуйидаги Карно картаси билан тасвирлаш мумкин.

![]() S R

S R

|

||

|

0

|

1 |

x |

0 |

|

1

|

|

x |

0 |

Qn

10.4-расм. RS-триггери Карно картаси.

Карно картасидан характеристик функциянинг И-НЕ кўринишида топамиз:

![]()

![]()

![]()

![]()

Qn+ı= S v RQn = S ·RQn (47)

Характеристик функциянинг ИЛИ-НЕ кўриниши қуйидагича бўлади. Топилган функциялар асосида RS-триггер схемаларини қурамиз:

![]()

![]() Qn+ı

= R v (S v Qn) (48)

Qn+ı

= R v (S v Qn) (48)

|

|

а) б)

10.5-расм. RS-триггернинг И-НЕ (а) ва ИЛИ-НЕ(б) базисидаги схемалари ва шартли кўринишлари.

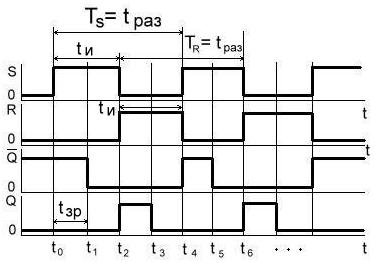

RS-триггернинг динамик режимдаги фаолиятининг вақт диаграммаси 10.6- расмда келтирилган.

|

10.6 – расм. RS – триггерининг динамик режимидаги фаолиятининг вақт диаграммаси.

10.6 – расмда tзр- идел мантиқий элементдан сигналнинг узатиш вақти, t2 = t1 = tзр 1 сигналининг триггер чиқишида пайдо бўлишига кетган вақт. Триггернинг ҳолатини ўрнатиш учун tи = 2tзр вақт керак. Диаграмма бўйичаTs = T R = 4tзр.

Синхрон

|

RS-триггернинг схемаси ва уни шартли кўриниши қуйидаги расмда келтирилган.

а) б)

10.7-расм. Синхрон RS-триггернинг схемаси (а) ва унинг шартли кўриниши(б).

Cинхрон триггерларда С=0 бўлганда, БЯнинг киришида 1 сигналлари бўлади ва БЯ аввалги холатни сақлаб қолади. Агар С=1 бўлса, унда синхрон триггер ўтиш жадвали (10.2-жадвал) асосида ишлайди.

Икки поғонали RS-триггернинг схемаси ва унинг шартли тасвирланиши 10.8–расмда келтирилган.

|

а) б)

10.8-расм. Икки поғонали RS- триггер (а) ва унинг шартли белгиланиши.

Икки поғонали триггерлар кириш ва чиқиш поғоналаридан иборат бўлгани учун улар MS (master – slave) туридаги триггерлар деб аталади. MS туридаги триггерлар бир поғонали триггерларга нисбатан ишончли ишлайди.

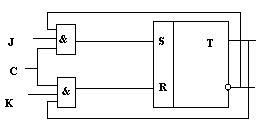

JK – Триггер

JK-триггери универсал бўлиб, 1 ва 0 ҳолатлари алохида ўрнатилади. Триггернинг 1 холати J (Jerk ) кириш сигнали билан ўрнатилади, 0 ҳолати эса K (Kill ) кириш сигнали билан ўрнатилади. RS-триггерда иккита киришга бирданига 1 сигналлари бериш таъқиқланган бўлса, JK- триггерда эса таъқиқланмаган. Ушбу кириш комбинациясида JK-триггер аввалги ҳолатини тескарига ўзгартиради (10.3-жадвал).

10.3-жадвал

|

J |

K |

Qn+ı |

|

0 1 0 1 |

0 0 1 1 |

Qn 1 0

|

JK- триггерининг Карно картаси 10.9-расмда келтирилган.

Картада кўрсатилган контурларни ҳосил қилиб, қуйидаги характеристик функцияни топамиз:

![]()

![]()

![]()

![]() Qn+ı

= J

Qn V K Qn (49)

Qn+ı

= J

Qn V K Qn (49)

J K

![]()

![]()

|

0

|

1 |

1 |

0 |

|||

|

|

1 |

0 |

0 |

Qn

10.9- расм. JK- триггернинг Карно картаси..

Синхрон JK – триггернинг схемаси 10.10-расмда келтирилган.

|

.

10.10-расм. Синхрон JK- триггернинг схемаси.

Т- Триггер

Т-триггерининг битта кириши бор. Ушбу Т(akt) кириш санаш кириши деб аталади. Ҳар бир кириш сигнали (1) триггернинг чиқиш ҳолатини тескари қийматга ўзгартиради (10.4-жадвал).

10.4-жадвал

|

Т |

Qn+ı |

|

0

1 |

Qn

|

Т-триггернинг Карно картаси қуйидаги кўринишга эга:

Т

|

0

|

1 |

|

|

0 |

Qn

10. 11- расм. Т- триггер Карно картаси.

Ушбу Карно картаси асосида характеристик функцияни топамиз ва Т-триггер схемасини тузамиз:

![]()

![]()

|

Qn+ı = T Qn V T Qn.

10.12-расм. Т-триггернинг схемаси.

D - Триггер

D(irect) – триггернинг битта кириши бор. Триггер ҳолати келаётган кириш сигналининг қийматига тенг (10.5-жадвал).

10. 5-жадвал

|

D |

Qn+ı |

|

0 1 |

0 1 |

Карно картаси (10.13-расм) бўйича Qn+ı = D.

D

![]()

|

0

|

1

|

|

0

|

|

Qn

3.13-расм. D-триггер Карно картаси.

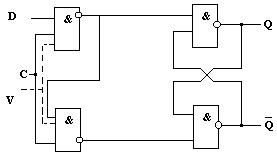

D-триггер схемаси қуйидаги кўринишга эга:

|

10. 14- расм. D-триггер схемаси.

DV–триггерида такт сигнали киришига (С) параллел ҳолда V–кириши қўшилади. Триггер V=1 бўлганда оддий ҳолда ишлайди, V=0 бўлганда, олдинги ҳолатини сақлаш режимида ишлайди.

Ихтиёрий триггер синтези

БЯ асосида икки киришдан иборат 10.6-жадвал асосида ишлайдиган синхрон триггерни синтез қилиш керак.

10.6-жадвал

|

Е1 |

Е2 |

Qn |

|

1

0 1 |

0 0

1 1 |

0 Qn

Qn 1 |

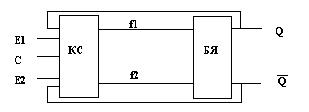

Синтез қилмоқчи бўлган триггеримизнинг тузилиши 10.15-расмда келтирилган.

|

10. 15-расм. Ихтиёрий триггер тузилиши.

Триггер синтези масаласи унинг комбинацион схемасини қуриш йўли билан ечилади. Комбинацион схема кириш сигналларини (Е1 и Е2) чиқиш сигналларига (f1 и f2) шундоқ ўтказиши керакки, бунда БЯ ихтиёрий триггерининг ўтишини 10.6-жадвал асосида амалга оширсин.

Комбинацион схеманинг ишлаш жадвали ихтиёрий триггер ўтиш жадвали (10.6-жадвал) ва КБЯнинг бошқарув жадвали (10.7-жадвал) асосида тузилади.

10.7-жадвал

|

Qn |

Qn+ı |

f1 |

f2 |

|

0 0 1 1 |

0 1 0 1 |

1 0 1 ~ |

~ 1 0 1 |

Комбинацион схеманинг ишлаш жадвали (10.8-жадвал) кириш сигналлари қийматларининг 16 та комбинациясидан иборат ( С, Е1, Е2, Qn) . Жадвалнинг бешинчи устуни (Qn+ı) триггернинг ўтиш жадвали (10.6-жадвал), олтинчи (f1) ва еттинчи (f2) устунлари эса БЯнинг бошқарув жадвали (10.7-жадвал).асосида тўлдирилади.

10.8-жадвал

|

С |

Е1 |

Е2 |

Qn |

Qn+ı |

f1 |

f2 |

|

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 |

0 1 0 1 0 1 0 1 0 0 1 0 0 1 1 1 |

1 ~ 1 ~ 1 ~ 1 ~ 1 1 0 1 1 ~ 0 ~ |

~ 1 ~ 1 ~ 1 ~ 1 ~ 0 1 0 ~ 1 1 1 |

Синхрон триггер фаолиятидан маълумки, С=0 бўлганда триггер аввалги ҳолатини сақлаб қолади (Qn+ı=Qn), С=1 бўлганда эса, триггер ўтиш жадвали асосида ишлайди.

Карно карталаридан қуйидагиларни топамиз:

![]()

![]()

![]()

![]() f1 = C + Е2 + Qn + C∙Е2∙Qn (50)

f1 = C + Е2 + Qn + C∙Е2∙Qn (50)

![]() f2

= C +Е1 +Qn +C∙Е1∙Qn (51)

f2

= C +Е1 +Qn +C∙Е1∙Qn (51)

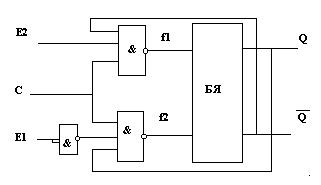

Топилган функциялар асосида ихтиёрий триггернинг схемасини қурамиз:

|

10.18- расм. Ихтиёрий триггер схемаси.

лаборатория ишини бажариш учун вариантлар

10.9-жадвал. Вариантлар.

|

№ |

Е1 |

Е2 |

Qn+ı |

№ |

Е1 |

Е2 |

Qn+ı |

|

1

|

0 1 0 1 |

0 0 1 1 |

1 0 0 Qn |

15 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 Qn |

|

|

0 1 0 1 |

0 0 1 1 |

0 1 1 –Qn |

16 |

0 1 0 1 |

0 0 1 1 |

1 0 1 Qn |

|

3 |

0 1 0 1 |

0 0 1 1 |

0 1 0 Qn |

17 |

0 1 0 1 |

0 0 1 1 |

0 1 Qn –Qn |

|

4 |

0 1 0 1 |

0 0 1 1 |

1 1 0 –Qn |

18

|

0 1 0 1 |

0 0 1 1 |

1 –Qn 0 Qn |

|

5 |

0 1 0 1 |

0 0 1 1 |

Qn 1 0 0 |

19 |

0 1 0 1 |

0 0 1 1 |

Qn 1 –Qn 0 |

|

6 |

0 1 0 1 |

0 0 1 1 |

–Qn 1 0 1 |

20 |

0 1 0 1 |

0 0 1 1 |

Qn 0 1 1 |

|

7 |

0 1 0 1 |

0 0 1 1 |

Qn 1 1 0 |

21 |

0 1 0 1 |

0 0 1 1 |

0 Qn Qn 1 |

|

8 |

0 1 0 1 |

0 0 1 1 |

1 –Qn 1 0 |

22 |

0 1 0 1 |

0 0 1 1 |

1 –Qn Qn 0 |

|

9

|

0 1 0 1 |

0 0 1 1 |

0 Qn 1 1 |

23 |

0 1 0 1 |

0 0 1 1 |

0 0 1 1 |

|

10 |

0 1 0 1 |

0 0 1 1 |

1 –Qn 1 0 |

24 |

0 1 0 1 |

0 0 1 1 |

1 0 1 0 |

|

11 |

0 1 0 1 |

0 0 1 1 |

1 1 Qn 0 |

25 |

0 1 0 1 |

0 0 1 1 |

1 1 0 0 |

|

12 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 0 |

26 |

0 1 0 1 |

0 0 1 1 |

0 1 1 0 |

|

1 |

0 1 0 1 |

0 0 1 1 |

0 –Qn 1 Qn |

27 |

0 1 0 1 |

0 0 1 1 |

1 0 0 1 |

|

14 |

0 1 0 1 |

0 0 1 1 |

1 Qn 0 –Qn |

28 |

0 1 0 1 |

0 0 1 1 |

1 0 Qn –Qn |

12-лаборатория иши

Бир триггер туридан иккинчи триггер турига ўтиш

Ишдан мақсад: Талабалар ишлаб чиқаришда учрайдиган муаммолардан бири – бир триггер типи асосида иккинчи триггер қуриш масалаларини ўрганиб, малакавий билим орттиришлари керак.

Назариядан қисқача маълумотлар

Рақамли қурилмаларни қуриш жараёнида бир триггер асосида бошқа турдаги триггерни қуриш керак бўлади. Масалан, Т–триггери асосида RS-триггерни қуриш керак.

|

Т-триггери асосидаги RS-триггернинг функционал тузилиши 10.19- расмда келтирилган.

12.1–расм. Синтез қилинаётган RS-триггернинг функционал тузилиши.

Ихтиёрий триггер синтези масаласидан маълумки, триггер синтези масаласи комбинацион схемани қуриш йўли билан ечилади. Комбинацион схеманинг ишлаш жадвали RS –триггернинг ўтиш жадвали (12.2-жадвал) ва Т – триггернинг бошқарув жадвали (12.1-жадвал) асосида тузилади.

12.1-жадвал

|

Qn Qn+ı |

S R |

J K |

T |

D |

|

0 0 0 1 1 0 1 1 |

0 ~ 1 0 0 1 ~ 0 |

0 ~ 1 ~ ~ 1 ~ 0 |

0 1 1 0 |

0 1 0 1 |

Комбинацион схеманинг ишлаш жадвали (12.2-жадвал) кириш сигналлари (S,R,Qn) қийматларининг 8 та комбинациясидан иборат. Qnқ1 сигналининг қиймати (тўртинчи устун) RS – триггернинг ўтиш жадвали асосида, Т сигналининг қиймати (бешинчи устун) эса, Т – триггерининг бошқарув жадвали асосида топилади..

12.2-жадвал

|

S |

R |

Qn |

Qn+ı |

T |

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 1 0 0 1 1 х х |

0 0 0 1 1 0 х х |

Т- функцияси қуйидаги Карно картаси билан ифодаланади:

Qn R

![]()

![]()

|

0

|

0 |

1 |

0 |

|||

|

1

|

0 |

X |

x |

S

12.2-расм. Т- функциясининг Карно картаси.

Карно картасидан қуйидагини топамиз:

![]() Т

=

SQn v RQn. (52)

Т

=

SQn v RQn. (52)

Т- функцияни И-НЕ базисига ўтказамиз:

![]()

![]()

![]() -- _

-- _

Т = SQn · RQn. (53)

Топилган фунция асосида триггер схемасини қурамиз:

|

12.3- расм. Т- триггер асосида қурилган RS – триггер схемаси.

Талабалар 12.3-жадвал асосида берилган триггер бўйича бошқа турдаги триггерни синтез қилишлари керак.

лаборатория ишини бажариш учун вариантлар

12.3-жадвал

|

Вариант рақами |

Берилган триггернинг тури |

Синтез қилинадиган триггернинг тури |

|

1 2 3 4 5 6 7 8 9 10 11 12 |

RS JK D T RS JK D T RS JK D T |

JK RS RS JK T D JK RS D T T D |

Ҳисобот қуйидагилардан ташкил топган бўлиши керак

1. Ишнинг мақсади.

2. Масаланинг қўйилиши.

3. Ихтиёрий триггер синтези ва ишлаш бўйича вақт диаграммаси.

4. Берилган триггер асосида бошқа турдаги триггернинг синтези.

5. Хулоса.

Назорат саволлари

1. Триггернинг вазифаси ва қўллаш сохалари.

2. Триггерларнинг таснифи.

3. Триггерларнинг параметрлари ва тавсифлари.

4. Бистабиль ячейканинг ишлаш принципи.

5. Триггер фаолиятини ифодалаш усуллари.

6. Триггер турлари.

7. RS – триггери турлари.

8. Асинхрон ва синхрон триггерлар.

9. Универсал JK – триггернинг ишлаш принципи.

10. Т – триггернинг ишлаш принципи.

11. D – триггернинг ишлаш принципи.

12. Икки поғонали триггернинг ишлаш принципи.

13. БЯ асосида қуриладиган триггер синтези босқичлари.

14. Берилган триггер асосида бошқа турдаги триггернинг синтези.

13 ва 14 – Лаборатория ишлари

силжитувчи ва универсал Регистрлар синтези

Ишдан мақсад: Рақамли автоматларнинг асосий қурилмаларидан бири бўлган–регистрларни ўрганиш, кўп функцияли регистрларни синтезлаш усулини эгаллаш, регистрларни экспериментал тарзда йиғиш ва созлаш бўйича тушунчага эга бўлиш.

Назариядан қисқача маълумотлар

Регистр деб ахборот қабул қилиш, ҳотирада сақлаш ва узатиш, шунингдек ушбу ахборот устида айрим мантиқий ҳаракатларни бажариш имкониятига эга бўлган қурилмага айтилади. Бажарадиган функцияларига кўра регистрлар қуйдаги турларга бўлинади

1. Маълумотни паралел ёзувчи ва паралел ўқувчи.

2. Маълумотни кетма–кет ёзувчи ва паралел узатувчи (маълумотни кетма–кетидан паралел код ўзгартирувчи қурилма).

3. Маълумотни паралел ёзувчи, кетма-кет ёзувчи (маълумотни паралелдан кетма-кет кодга айлантирувчи қурилма).

4. Силжувчи регистр (ўнгга, чапга, циклик ).

Регистр маълум бир тарзда уланган қурилма бўлиб, айрим амалларни бажарилишини ҳам таъминлайди.

Уларга:

-регистрни дастлабки холатга ўрнатиш.

-бошқа қурилмадан маълумотни қабул қилиш.

-бошқа қурилмага маълумотни узатиш.

-регистр таркибини ўнгга ёки чапга суриш.

-маълумот кодини кетма-кетдан паралелга ўзгартириш.

13.1-расмда маълумотни паралел ёзувчи n-даражали регистр чизмаси келтирилган.

![]()

![]()

![]()

![]() DOo DO1 Чиқишлар DO n-2

DO n-1

DOo DO1 Чиқишлар DO n-2

DO n-1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

T Т T T

![]()

![]()

![]()

![]()

![]() R C D R C D R

C D R C D

R C D R C D R

C D R C D

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() ''0''

''0''

Регистр юклаш.

DJ0 DJ1 Киришлар DJ n-2 DJn-1

13.1-расм. Паралел ёзувчи ва ўқувчи дастлабки ''0'' холатига ўтувчи, регистр чизмаси.

Киришида сигнал с=1 бўлган холатда регитрга Д киришдаги маълуьот ёзилади, R-киришга ''0'' сигнал берилган тақдирда регистр дастлабки холатга ўрнатилади, яъни регистрнинг барча киришларида ''0'' бўлади.

Рақамли автоматларда аксарият холларда бир неча иккилик сўзларни маълумотига ишлов берувчи қурилманинг бевосита яқинига жойлаштириш талаб қилинади. Шунинг учун бир регистрдан иккинчи регистрга маълумот ўта оладиган регистрлар массиви яратилади.

Регистрлараро маълумот алмашинувининг юқори тезлигини таъминлаш учун маълумотни паралел кодда узатиш талаб этилади. Айни бир вақтда ҳамма n- даражалар регистрлараро ахборотни ташкил қилиш учун n-та мултиплексорлардан фойдаланилади, улар ёрдамида хар бир регистрнинг чиқиши мультиплексор ёрдамида уланган. Маълумотнинг сони эса регистрнинг разрядига боғлиқ.

Узатувчи регистр адрес кодини мулътиплексорнинг бошқарувчи киришларига узатиб маълумотлар шинасида унинг таркибини олиши мумкин.

Ахборотни маълумотлар шинасидан керакли регистрга ёзиш учун унинг С киришига ёзишни рухсат этувчи 1 сигналини узатиш керак.

Ёзишни рухсат этувчи сигнални хосил қилиш учун дешифратор ишлатилади, унинг киришига қабул қилувчи регистрнинг адрес коди узатилади. Дешифраторнинг киришлар сони қуйдагича аниқланади. k=log2(m+1): Буерда м-регистрлар сони. Агар каср сон чиқса уни ўзига яқин катта сонгача яхлитлаш керак. Мултиплексор ва дешифраторнинг дастлабки холатида киришларига фақат ноллардан ташкил топган (0, 0…0) код узатилади. Шунинг учун бирор бир регистр танланган бўлмайди.

Кўп холларда рақамли автоматлар, регистр таркибини маълумот бор даражалар сонига қараб ўнгга ёки чапга силжитиш керак бўлади. Бу амални силжитиш регистрлари бажаради.

Ахборотни сақлаш учун n-та триггер қўлловчи силжиш регистрига n даражали силжиш регистри дейилади. Четдаги чап даражани катта, ўнгни эса кичик даража деб қабул қилинган. Катта даража ''0'' номерга эга, кичиги эса (n-1) га. Шунинг учун ўнг ва чап силжиш ҳақида гапирилади.

Умумий холатда регисрда силжиш операцияси I-триггердан иборат ахборотни g+I триггергга узатиб, сўнг g-i дан I – триггерга узатилади.

Силжитилувчи ахборот йўқолиши, ёки қайтарилиши учун автоматнинг бошқа қурилмаларига узатилиши мумкин.

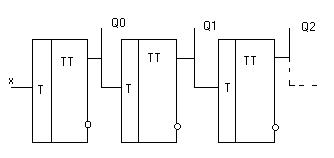

Триггерлар ва камбинацион схемаларнинг асосий хусусиятига, улар энг оддий холатда ахборотни кейинги триггерга узатиши ва бир вақтнинг ўзида, олдингидан қабул қилиш имконини бериш мумкин. Бунда ишлатилаётган триггернинг тури катта ахамиятга эга. 13.2-расмда бир каскадли ва икки каскадли триггерлар учун силжитиш схемаси келтирилган.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() от I-3 D T

D T D T D T

от I-3 D T

D T D T D T

![]()

![]()

![]()

![]() к I+2

к I+2

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() C

C C C

C

C C C

![]() шс1 i-2

I-1

I I+1

шс1 i-2

I-1

I I+1

шс2

![]()

![]()

а)

![]()

![]()

![]()

![]()

![]() J TT J TT J TT

J TT

J TT J TT J TT

J TT

![]()

![]()

![]()

![]()

![]() от i-3

от i-3

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() C C

C C к(I+2)-

му

C C

C C к(I+2)-

му

![]()

![]()

![]()

![]()

![]() K K

K K

K K

K K

шс i-2 I-1 I I+1

![]()

б)

13.2-расм силжитиш схемалари.

а) Д турдаги бир каскадли триггерлар учун.

б) jk турдаги бир каскадли триггерлар учун.

Бир каскадли триггерларнинг регистрида ахборотни силжитиш учун иккита ШС-1 ва ШС-2 силжитиш шиналари ишлатилади. Жуфт триггерлардан ток триггерларга ахборотни ёзиш учн ШС-1 шина хизмат қилади. Токлардан жуфтга ёзиш учун эса ШС-2 шина хизмат қилади. Ток триггерлар силжитиш амалини бажариш ахборотни оралиқ сақлаш учун хизмат қилади. Силжишнинг биринчи тактида сигнал ШС-1га узатилади, иккинчи тактда эса ШС-2га.

Икки каскадли триггернинг силжиш регистри схемасида битта силжиш схемаси зарурдир. Икки каскадли триггерда регистрнинг ишлашини 13.3-расмда кўрсатилган вақт диаграммасида кўрсатиш мумкин.

![]()

![]()

![]()

![]()

![]() tu

tu

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() шс

шс

![]()

![]()

![]() t

t![]()

![]()

![]()

![]()

![]()

![]()

![]() Qi-1 tзфтр

Qi-1 tзфтр

|

|||

![]()

![]()

![]() t

t

tф

![]()

![]()

![]()

![]()

![]() Qi-1

Qi-1

|

![]()

![]() t

t

![]()

![]() Qi

Qi

t

13.3-расм. JK триггерида силжиш регистри ишининг вақт диаграммаси.

Вақт диаграммасидан регистрнинг тезкорлигини аниқлаш мумкин. Тсдв нинг қиймати силжитиш импульси етиб келиш моментининг схемадан ўтиш жараёни моменти тугагунига қадар оралиқ интервалга тенг. (13.3-расмга қаранг). Вақт диаграммасидан Т сдв нинг қиймати Т сдв = tф +tи билан аниқланади.

Агар ахборотни К даражага силжитиш талаб этилса, К марта ''1'' разрядга кетма-кет силжишни амалга ошириш керак. Бу амалнинг бажарилиш вақтини камайтириш учун регистр схемаси мултиплексорлар билан тўлдирилади.

Керакли силжишни амалга ошириш учун разрядлар сони, мултиплексорларнинг бошқарилувчи киришларига узатилувчи код билан аниқланади. 13.4-расмда ахборотни 1,2…d даражага силжитишни рухсат этувчи силжитиш регистри схемаси келтирилган. Силжишнинг бошлашдан олдин мултиплексорларнинг бошқарувчи киришларига, регистрдаги сақланувчи сонни кераклича силжитиш учун разрядлар сони коди ўрнатилади. Натижада мултиплексор I-триггер киришини керакли (i-k) чи триггер чиқиши билан коммутациялайди, сўнгра силжиш импулси ШС шинасига узатилади ва амал тугалланади.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() бошқа d бошқа

d

бошқа d бошқа

d

![]()

![]() триггердан.

3 MS триггердан. 3

MS

триггердан.

3 MS триггердан. 3

MS

![]()

![]()

![]()

![]()

![]()

2 2

2 2

![]()

![]()

![]() D TT D D TT D

D TT

D TT D D TT D

D TT

![]()

![]()

![]()

![]()

![]() 1 1

1 1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() C X C X

C

C X C X

C

шс i-1 i i+1

![]()

![]()

![]() силжувчи разряд квд сони

силжувчи разряд квд сони

![]()

13.4-расм. 1,2…d даражага силжитиш регистри.

Мултиплексорни ишлатиб, ахборотни ҳам ўнгга ва ҳам чапга силжитиш имконини берувчи, реверсив силжиш регистрларини қуриш мумкин. Бунинг учун мултиплексор киришларининг бир қисмини, ҳам ўнгга ва чапга жойлашган триггерлар билан улаш керак. Унда кодларнинг бир қисмини ўнгга силжишни, бошқа қисми эса чапга силжишни аниқлайди.

Замонавий рақамли автоматларда, силжиш регистрлари ахборотни паралел ёзиш ва ўқиш имкониятига эга. Бунинг учун ҳар бир триггер белгиланган функцияларни бажариш учун, керакли мантиқий схема билан таъминланган. 13.5-расмда шунақа регистрнинг схемаси келтирилган.

![]()

![]()

![]()

![]()

![]()

![]() посл

/ пар Ji

Ji-1

посл

/ пар Ji

Ji-1

|

![]()

![]()

![]()

![]()

![]() посл

/ пар

& &

посл

/ пар

& &

![]()

![]()

![]()

![]() 1 1

1 1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

& &

& &

![]()

![]()

![]()

![]()

![]() D

TT D

TT D TT

D

TT D

TT D TT

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() C

C C

C

C C

шс i-1 I I+1

![]()

13.5-расм. Паралел юклашли силжитиш регистри.

Агар киришда кетма-кет паралел ''1'' сигнал бўлса, бу сигнални ШС га узатишда ахборот силжиши ёки кетма-кет ёзиш амалга ошади.

Агар кетма-кет паралел сигнал нолга тенг бўлса, регистрнинг Ji киришларда мавжуд бўлган ахборт ёзилади, яъни ахборотни паралел ёзиш амалга оширилади. Бундай регистрнинг ахборотга кетма-кет паралел ва паралел кетма-кет ишлов берувчи сифатида қўллаш мумкин.

Силжитиш регистрининг умумий функционал схемаси 13.6-расмда келтирилган.

шс

![]()

![]()

![]()

![]() Q1

Q2

Qn

Q1

Q2

Qn

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Е1

Т Е1 Т

Е1 Т

Е1

Т Е1 Т

Е1 Т

![]()

![]()

![]()

![]()

![]()

![]()

![]() С

С …….. С

С

С …….. С

![]()

![]()

![]() Q1 Q2

Qn

Q1 Q2

Qn

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Е2

Е2 Е2

Е2

Е2 Е2

![]()

кс

![]()

![]()

![]()

![]()

У1 У2 У3 Уm

13.6-расм. Силжиш регистрининг умумий функционал схемаси.

Комбинацион схеманинг (КС) киришларига регистр триггерлари чиқишларидан сигналлар узатилади ва yi i=1,m ташқи бошқариш сигналлари бир триггерлардан бошқаларига силжиш занжирларини аниқлайди ва бошқа занжирлар ишини тақиқлайди. Сигналлар КС чиқишларидан триггерлар киришларига узатилади. i- триггер киришларини уйғотиш функциясини қуйдаги кўринишда ёзиш мумкин:

Е1i= ф1i(O1(t), O2(t)…On(t), y1, y2,…ym); (54)

Е2i=ф2i(O1(t), O2 (t)…On(t), y1, y2,…ym); (55)

Триггерлар тури берилганда регистрларни лойиҳалаштириш масаласини ечиш учун, ҳар бир триггер киришини уйғотиш функциясини тузиш ва топилган қийматларни минималлаштириш керак.

Маълумки, исталган триггер функцияларини ўтишлар жадвали ёрдамида бериш мумкин. Аммо, регистр синтези учун бу жадвални қўллаш маълум қийинчиликларни туғдиради. Бу қийинчиликларни ўтиш матрицасига айлантириб бартараф этиш мумкин. Ўтишлар матрицаси элементлари qQ(t), Ек сигнал қийматларини кўрсатади. У таъсирида k триггер Q(t) холатдан Q(t+1) холатга ўтади.

Ҳар бир матрица элементи 0; 1 га тенг бўлиши ёки унинг қиймати ноаниқ бўлиши мумкин.

DV ва JK триггерлар ўтишлар жадвалининг матрицасига айланиш жараёнини кўриб чиқамиз.

DV триггеридан бошлаймиз. 13.1-жадвалдан триггерни Q(T)=0 холатдан Q(t+1)=0 холатга ўтказувчи D ва V кириш сигналларини қийматини топамиз. 13.1-жадвалдан шунингдек, Д=0 ва V=0: Д=0 ва V=1 га тенг бўлгандагина олиш мумкин.

Агар ўзгарувчи Д (0 ёки 1) ўзгарувчан қийматни қабул қилса у холда Д га боғлиқ бўлмайди. Бу боғлиқлик ўтишлар матрицасида қуйдагича ифодаланиши мумкин. Агар Д устуннинг биринчи қаторига а1 ни ёзсак, унда V устунда а1*в1 ни ёзиш керак , бунда а1 ва в1 ''0'' ва ''1'' қийматларни қабул қилувчи коэффицентлар ''0-1'' га ўтиш учун Д=1 ва V=1 бўлганда амалга ошади. ''1-1'' га ўтиш қуйидаги сигналлар билан амалга оширилади. Д=0, V=0; Д=1, V=0; Д=0-1, V=1.

Бундан ДV триггерининг ўтишлар матрицаси қуйидаги кўринишга эга

Д V

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

0-0

![]()

![]() а1

а1в1

а1

а1в1

0-1 1 1

1-0 0 1

1-1 а2 а2в2

Аналогик холатда J-K триггерлари учун 2-жадвалдан ўтишлар матрицасини олиш мумкин.

![]()

![]()

![]()

![]() J K

J K

13.1-жадвал 13.2-жадвал 0-0 0 а1

![]()

![]()

0-1 1 а2

0-1 1 а2

t t+1 t t+1 1-0 а3 1

![]()

![]()

![]()

![]()

![]()

![]()

![]() Д V Q(t) Q(t+1) J

K Q(t)

Q(t+1) 1-1

а4 0

Д V Q(t) Q(t+1) J

K Q(t)

Q(t+1) 1-1

а4 0

![]()

![]()

0 0 0 0 0 0 0 0

0 0 1 1 0 0 1 1

0 1 0 0 0 1 0 1

0 1 1 0 0 1 1 0

1 0 0 0 1 0 0 1

1 0 1 1 1 0 1 1

1 1 0 1 1 1 0 1

1 1 1 1 1 1 1 1

Регистр синтезининг кейинги босқичларида бошқарувчи шиналар сонини ва триггерларни уйғотиш функцияларни уларга қўйилган ўтишлар матрицаси ва лойиҳалаштирилаётган регистр шартларига риоя қилиб аниқлаш керак.

Бунинг учун битта регистр қийматини кўриб чиқиш етарлидир, чунки регистр схемаси бир хил схемалардан ташкил топган яъни у бир хилдир. Синтезлаш мисолини кўриб чиқамиз, реверсив силжиш регистрини синтезлаш керак. (регистр, ўнг ва чапга силжиш имконига эга). Бажарилувчи амаллар сони 2 тадан ошмаслиги учун, битта бошқариш шинаси етарли.

Триггерларни уйғотиш функциялари қуйдаги кўринишни олади.

Е1i=f1i(Qi+1(t),Qi-1(t), y); (56)

E2i=f2i(Qi+1(t),Qi-1(t), y); (57)

Ўтишлар жадвалини тузамиз, бунда у=0 бўлганда силжиш бир даража чапга силжитиш деб қабул қиламиз.

13.3-жадвалнинг чапидаги 5та устунни лойихалаштириш регистрининг I-триггернинг ўтиш жадвалини ҳосил қилади.

Жадвалнинг кейинги икки устуни JK триггерлар асосида қурилган триггерларниг уйғониш функцияси аниқланади.

Жадвалнинг охирги 2та устуни DV триггерли регистрлар учун. JK триггер учун 13.3-жадвал 1-қаторини кўриб чиқамиз. у=0 бўлганда I триггер JK триггерлар матрицалар ўтишига асосланиб, 0-0 га ўтишни амалга ошириш керак. Шунга ўхшаш JK ва DV триггерлар учун жадвалнинг бошқа қаторлари тўлдирилади.

y Qi-1 Qi Qi+1 Qi Ji Ki Di Vi

0 0 0 0 0 0 а0 а0 а0в0

0 0 0 0 0 0 а1 а1 а1в1

0 0 1 0 0 а2 1 0 1

0 0 1 1 0 а3 1 0 1

0 1 0 0 1 1 а4 1 1

0 1 0 1 1 1 а5 1 1

0 1 1 0 1 а6 0 а6 а6в6

0 1 1 1 1 а7 0 а7 а7в7

1 0 0 0 0 0 а8 а8 а8в8

1 0 0 1 1 1 1 0 1

1 0 1 1 1 а11 0 а11 а11в11

1 1 0 0 0 0 а12 а12 а12в12

1 1 0 1 1 1 а13 1 1

1 1 1 0 0 а14 1 0 1

1 1 1 1 1 а15 0 а15 а15в15

Шундай қилиб, бизга триггерларни уйғотиш функциялари берилган, ва уларни минималлашириш керак. Бунинг учун Карно картасидан фойдаланиш керак.

![]()

![]()

![]() шс

шс

i-2

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1 &

1 1 3 &

1

1 &

1 1 3 &

1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

J TT Qi-1

J TT Qi

J TT Qi-1

J TT Qi

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() C C

C C

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() 1 & 2

1 & 1

1 & 2

1 & 1

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() K K

K K

4

![]()

![]()

![]() У I-1 I

I+1

У I-1 I

I+1

13.9-расм. JK ва DV триггерларига асосланган реверсив силжиш регистри.

Синтезловчи регистрнинг вақт характеристикаларининг аниқлаш учун ишни вақт диаграммаларидан бошлаш керак. Расмга асосланиб, мантиқий элемент ва триггерларнинг кўрилган қийматлари ушлаб турилганда силжиш вақти.

Тсдв=tзфтр+tи +2tзф +tзф га тенг. (58)

Ёпиқ холатдаги силжиш регистри асосида қурилган 10-расмдаги диаграмма, вақт боғликларини аниқлашга имкон беради. Лекин регистр ишини тажрибавий кузатиш учун бу режимни қўллаб бўлмайди. Бунинг учун жараённи циклик қайтарилишини таъминлаш керак. Буни амалга ошириш учун регистрни халқага бирлаштириш керак. Бу режимда силжитувчи импулсларнинг узлуксиз серияси регистрга ёзилган сўзнинг циркуляциясини таъминлайди. Бу режимда осцилограф ёрдамида регистр ишидаги носозликлар ва вақт параметрларини аниқлаш мумкин.

лаборатория ишини бажариш учун вариантлар

13.3-жадвал

|

№ |

Силжиш амали |

Триггер тури |

Код |

|

1 |

Чапга 1 разряд, ўнгга 1 разряд |

D |

0001 |

|

2 |

Чапга 1 разряд, ўнгга 2 разряд |

JK |

0010 |

|

3 |

Чапга 1 разряд, ўнгга 3 разряд |

RS |

0011 |

|

4 |

Чапга 1 разряд, ўнгга 4 разряд |

SR |

0100 |

|

5 |

Чапга 2 разряд, ўнгга 1 разряд |

T |

0101 |

|

6 |

Чапга 2 разряд, ўнгга 2 разряд |

D |

0110 |

|

7 |

Чапга 2 разряд, ўнгга 3 разряд |

JK |

0111 |

|

8 |

Чапга 2 разряд, ўнгга 4 разряд |

RS |

1000 |

|

9 |

Чапга 3 разряд, ўнгга 1 разряд |

SR |

1001 |

|

10 |

Чапга 3 разряд, ўнгга 2 разряд |

T |

1010 |

|

11 |

Чапга 3 разряд, ўнгга 3 разряд |

D |

1011 |

|

12 |

Чапга 3 разряд, ўнгга 4 разряд |

JK |

1100 |

|

13 |

Чапга 4 разряд, ўнгга 1 разряд |

RS |

1101 |

|

14 |

Чапга 4 разряд, ўнгга 2 разряд |

SR |

1110 |

|

15 |

Чапга 4 разряд, ўнгга 3 разряд |

T |

1111 |

|

16 |

Чапга 4 разряд, ўнгга 4 разряд |

D |

0001 |

|

17 |

Чапга 1 разряд, ўнгга 1 разряд |

JK |

0010 |

|

18 |

Чапга 1 разряд, ўнгга 2 разряд |

RS |

0011 |

|

19 |

Чапга 1 разряд, ўнгга 3 разряд |

SR |

0100 |

|

20 |

Чапга 1 разряд, ўнгга 4 разряд |

T |

0101 |

|

21 |

Чапга 2 разряд, ўнгга 1 разряд |

D |

0110 |

|

22 |

Чапга 2 разряд, ўнгга 2 разряд |

JK |

0111 |

|

23 |

Чапга 2 разряд, ўнгга 3 разряд |

RS |

1000 |

|

24 |

Чапга 2 разряд, ўнгга 4 разряд |

SR |

1001 |

|

25 |

Чапга 3 разряд, ўнгга 1 разряд |

T |

1010 |

|

26 |

Чапга 3 разряд, ўнгга 2 разряд |

D |

1011 |

|

27 |

Чапга 3 разряд, ўнгга 3 разряд |

JK |

1100 |

|

28 |

Чапга 3 разряд, ўнгга 4 разряд |

RS |

1101 |

|

29 |

Чапга 4 разряд, ўнгга 1 разряд |

SR |

1110 |

|

30 |

Чапга 4 разряд, ўнгга 2 разряд |

T |

1111 |

ҳисобот қуйидагилардан ташкил топиши керак

1.Регистр i –даражасини ўтиш жадвали.

2.Триггерлар уйғонишининг Карно карталари.

3. Регистр схемаси.

4. Вақт диаграммалари.

Назорат саволлари

1.Регистрлар нима мақсадда ишлатилади?

2.Регистрларга классификация беринг?

3.Регистрлар синтезини асосий босқичларини айтинг?

4.Матрицалар ўтиши нима мақсадда керак?

5.Мисоллар ёрдамида қандай қилиб силжиш регистри паралел

кодни кетма-кетга ва тескарига ўтказиш мумкин?

6.Тадқиқ қилинганда нима мақсадда регистрни халқа усулида

улаш керак?

15 ва 16 – Лаборатория ишлари

ҲИСОБЛАГИЧЛАР СИНТЕЗИ

Ишдан мақсад: Иккилик ҳисоблагичларнинг ишлаш асослари ва қуриш усулларини ўрганиш бўйича амалий кўникма ва малакавий билимларни орттириш

АСОСИЙ НАЗАРИЙ МАЪЛУМОТЛАР

Ҳисоблагич рақамли қурилмалар таркибига киради ва импульслар сонини санайди. Импульслар ҳисоблагичнинг киришига узатилади. Ҳисоблагичнинг чиқишида эса саналган импульслар сони ўрнатилган кодда тасвирланади.

Ҳисоблаш модули (сиғими) М ҳисоблагичларнинг асосий кўрсаткичларидан биридир. Ҳисоблаш модули ҳисоблагични максимал нечтагача (М) санаши мумкинлигини курсатади. Ҳисоблагич М та импульсни санагандан сўнг яна бошидан санайди.

Ҳисоблаш модулининг қиймати бўйича ҳисоблагичлар иккилик ва иккиликда тасвирланган (кодланган) бўлиши мумкин. Иккиликда тасвирланган ҳисоблагичларнинг ҳисоблаш модули ихтиёрий бўлади, лекин санаши иккилик кодларда бўлади.

Санаш йўналиши бўйича ҳисоблагичлар қўшувчи (тўғри санайдиган), айирувчи (тескари санайдиган) ва реверсив (санаш йўналиши ўзгарувчан) бўлади.

Разрядлараро боғланиш усули бўйича ҳисоблагичлар кетма-кет, параллел ва комбинацион бўлиши мумкин.

Ҳисоблагичларнинг ишлаш тезлиги қуйидаги кўрсаткичлар билан белгиланади:

1. Кодни ўрнатиш вақти - Тк.

2. Ўтиш разрядини узатиш вақти -Ту.

3. Кириш ипульсларининг максимал частотаси -Fм.

Кириш сигналини бошидан ҳисоблагични янги ҳолати ўрнатилгангача бўлган вақт кодни ўрнатиш вақти ҳисобланади. Кириш сигналининг бошланиш вақтидан чиқиш сигналининг бошланиш вақтигача бўлган давр ўтиш разрядини узатиш вақти ҳисобланади.

Иккилик ҳисоблагичнинг ҳисоблаш модули 2 нинг n-чи даражасига (М=2ⁿ) тенг, бу ерда n – ҳисоблагичнинг разрядлар сони. Ҳисоблагичнинг ҳолати триггерларнинг чиқишидан олинадиган қуйидаги Qn-1 …. Q1 Q0 иккилик коди билан ифодаланади.

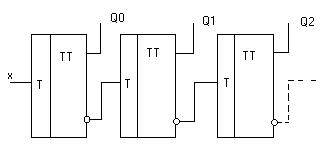

Қўшувчи (йиғувчи) ва айирувчи иккилик ҳисоблагичларнинг ишлаш жараёни 15.1-жадвалда келтирилган. Кичик(Q0) разряд триггери хар бир кириш сигналидан сўнг ўз қийматини ўзгартиради(жадвалнинг ўнг устунида Q0 0 ва 1 қийматларни галма гал қабул қилади). Кейинги Q1 разряд иккита 0 ва иккита 1 қийматларни галма-гал қабул қилади, кейинги Q2 разряд тўртта 0 ва тўртта 1 қийматларни галма гал қабул қилади ва ҳ.з.. Ҳар бир кейинги триггер ҳолатини ўзгариш частотаси олдинги триггер ҳолатини ўзгариш частотасидан икки мартта кичикдир. Ҳисоблагичларни триггерларни кетма-кет улаш йўли билан қуриш мумкин. Қўшувчи ва айирувчи хисоблагичларнинг схемалари 15.1-расмда келтирилган.

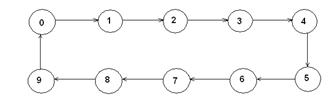

Қурилган ҳисоблагичлар кетма-кет хисоблагичлар қаторига киради, чунки ҳар бир триггернинг ҳолати кейинги триггернинг чиқиш сигнали келгандан сўнг ўрнатилади. Кетма-кет ҳисоблагичларнинг схемаси оддий, лекин ишлаш тезлиги паст.

15.1 -жадвал

|

Кириш |

Тўғри санаш |

Тескари санаш |

||||||||

|

Q3 |

Q2 |

Q1 |

Q0 |

N ўнлик |

Q3 |

Q2 |

Q1 |

Q0 |

N ўнлик |

|

|

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 |

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 |

1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 |

1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 |

1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 |

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

|

а)

|

б)

15.1-расм. Қўшувчи (а) ва айирувчи (б) кетма-кет ҳисоблагичлар.

Кетма-кет хисоблагични ўрнатиш вақти ҳисоблагичнинг разрядлар сонига (n) ва триггерни ҳолатини ўрнатиш вақтига (Ттг) тўғри пропорционал

Тк = n Ттг. (59)

Параллел ҳисоблагичларда триггерлар бир-бирига конъюкторлар билан уланади (15.2-расм). Ҳисоблагичга кириш сигнали келганда хамма триггерлар бирданига ўз холатларини ўрнатадилар. Хар бир триггер ўз ҳолатини фақат олдинги триггерлар “1” холатида бўлган тақдирдагина ўзгартиради.

Параллел ҳисоблагичнинг ўрнатиш вақти разрядлар сонига боғлик эмас ва қуйидагича топилади

Тк = Тзк = Ттг, (60)

бу ерда Т

зк – сигналнинг конъюктордан ўтиш вақти.

15.2-расм . Параллел ҳисоблагич.

Ихтиёрий модули ҳисоблагич синтези

Талабалар ихтиёрий модулли ҳисоблагични қуришлари керак.

Ихтиёрий К модулли ҳисоблагични қуриш учун М=2ⁿ модулли иккилик ҳисоблагичдан фойдаланиш керак. Иккилик ҳисоблагичнинг разрядлар сони n қуйидаги шартни қониқтириши керак: n = ┐log 2K┌.

Иккилик ҳисоблагичнинг ортиқча (L = M – K) ҳолатлари чиқариб ташланиши керак.

Ихтиёрий ҳисоблагичнинг ўтиш жадвали қурилади. Жадвалнинг чап тарафида ҳисоблагич триггерининг ҳозирги ҳолати, ўнг тарафида эса кейинги ҳолати кўрсатилади. Жадвал асосида ҳисоблагич триггерлари қайси ҳолатдан қандай ҳолатга ўтиш керакликлари аниқланади. Триггернинг бошқарув жадвали асосида тригернинг киришига қандай сигнал узатилиши кераклиги топилади.

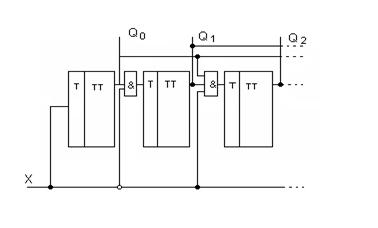

Мисол учун параметрлари К = 10 ва n = 4 бўлган декадали ҳисоблагични синхрон Т триггери асосида қурамиз.

Декадли ҳисоблагичнинг ўтиш графи 15.3-расмда келтирилган. Ҳисоблигичнинг ички ҳолатлари ва бир ҳолатдан кейинги ҳолатда ўтишлари графда тасвирланган. S10, S11, S12, S13, S14, и S15 ҳолатлари ишлатилмайди.

15.3-расм. Ҳисоблигичнинг ўтиш графи.

Ўтиш графи асосида ҳисоблагичнинг ўтиш жадвали қурилган (15.2-жадвал). Жадвалнинг ўнг тарафида тўртта триггернинг кириш сигналарининг қиймати келтирилган. 15.2-жадвал бўйича қандай ўтиш бўлганлиги аниқланади ва бунинг учун триггер киришига қандай сигнал узатиш кераклиги триггернинг бошқарув жадвали асосида топилади.

15.2 - жадвал

|

N |

T |

t+1 |

T3 |

T2 |

T1 |

T0 |

||||||

|

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

Q2 |

Q1 |

Q0 |

|||||

|

0 1 2 3 4 5 6 7 8 9 |

0 0 0 0 0 0 0 0 1 1 |

0 0 0 0 1 1 1 1 0 0 |

0 0 1 1 0 0 1 1 0 0 |

0 1 0 1 0 1 0 1 0 1 |

0 0 0 0 0 0 0 1 1 0 |

0 0 0 1 1 1 1 0 0 0 |

0 1 1 0 0 1 1 0 0 0 |

1 0 1 0 1 0 1 0 1 0 |

0 0 0 0 0 0 0 1 0 1 |

0 0 0 1 0 0 0 1 0 0 |

0 1 0 1 0 1 0 1 0 0 |

1 1 1 1 1 1 1 1 1 1

|

Барча Т сигналлари учун Карно карталари 15.4-расмда келтирилган. Ҳисоблигичнинг ишлатилмайдиган ҳолатлари d белги билан тасвирланган.

Т0 Q0 Q1

T0 =1

![]()

![]()

|

1 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

|

|

D |

D |

D |

|

1 |

1 |

D |

D |

![]()

![]()

T1

Q0 Q1

|

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

0 |

|

D |

D |

D |

D |

|

0 |

0 |

D |

D |

T2

Q0 Q1

|

|||||

|

T2 = Q0 Q1 |

0 |

1 |

0 |

||

|

Q3 |

0 |

1 |

0 |

||

|

|

D |

D |

D |

||

|

0 |

0 |

D |

D |

T3

Q0

Q1

Q2

![]()

![]()

|

T3 = Q0 Q1 Q2 + Q0 Q3 |

0 |

0 |

0 |

||

|

Q3 |

0 |

1 |

0 |

||

|

d |

d |

d |

d |

||

|

0 |

1 |

d |

d |

15.4-расм. Т0, Т1, Т2 ва Т3 функциялар учун Карно карталари.

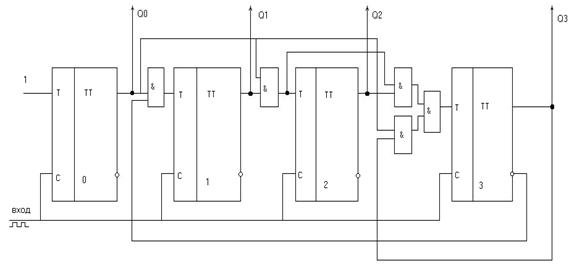

Карно карталари асосида Т0, Т1, Т2 ва Т3 функицялари топилган. Декадали ҳисоблигичнинг схемаси 15.5-расмда келтирилган.

|

а)

|

б)

15.5-расм. Декадали ҳисоблагич схемаси(а) ва авария сигнали учун схема(б).

Агар ҳисоблагич айрим носозликлар сабабли таъқиқланган ҳолатга ўтса, унда унинг ишлаши махсус сигнал билан тўхталиши ва авария сигнали берилиши мумкин. Ҳисоблигични таъқиқланган холатга ўтишини 15.5-расмдаги схема(б) аниқлайди. Авария сигнали қуйидаги функция билан ифодаланади