# A CONTROL-THEORETIC DESIGN AND ANALYSIS FRAMEWORK FOR RESILIENT HARD REAL-TIME SYSTEMS

by

#### PRADEEP M. HETTIARACHCHI

#### **DISSERTATION**

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

#### DOCTOR OF PHILOSOPHY

2015

| MAJOR: COMPUTER SCIENCE |      |  |  |  |

|-------------------------|------|--|--|--|

| Advisor                 | Date |  |  |  |

| Advisor                 | Date |  |  |  |

|                         |      |  |  |  |

ProQuest Number: 3723517

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 3723517

Published by ProQuest LLC (2015). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 - 1346

### **ACKNOWLEDGEMENTS**

My journey of PhD would not be a success without a few key people.

Prof. Nathan Fisher, my PhD advisor who did not restrict his guidance on academics but extended to a great deal helping me as a person. I am very fortunate and blessed to have him as my advisor. The difference I see in my academic life from the time I joined the PhD program to date is mainly because of the constructive guidance given by Dr. Fisher. I managed to stand on my feet and continue my graduate studies while facing substantial life challenges during the last five years mainly because my advisor's kind support. I convey my heartfelt gratitude and sincere thanks to Dr. Fisher.

During this challenging exercise, I got continuous support and advice from Dr. Le Yi Wang from Electrical Engineering Department. Also, comments and suggestions given by Dr. Weisong Shi and Dr. Monica Brockmeyer were extremely valuable. Furthermore, my CoPaRTS lab mates were always a critical factor for my success. I am very thankful to all of them.

This dissertation was supported by an NSF CAREER Grant (CNS-0953583), an NSF CSR Grant (CNS-1116787), an NSF CRI Grant (CNS-12-5338), and a grant from Wayne State University Office of Vice President of Research. Also, I must thankful for the Wayne State University Computer Science Department for accommodating and facilitating me for six year.

I am always grateful to the key persons who encouraged me to peruse graduate studies and opened the path in the United States, Eng. Samarasiri and Prof. Herath. Furthermore my loving appreciation to my parents, in-laws and sisters who helped and always encouraged me to achieve this goal. My special thanks to Malitha, my wife, and children, Induvari, Vidushani, Dushyanth, and Ravindu who partnered with me in this journey for always being patient, supportive and encouraging.

Finally, I thank anyone if I missed to mention here.

## TABLE OF CONTENTS

|    |         |                                               |                                                     | Page |  |  |

|----|---------|-----------------------------------------------|-----------------------------------------------------|------|--|--|

| A  | cknow   | ledgem                                        | ents                                                | ii   |  |  |

| de | dicati  | on                                            |                                                     | ii   |  |  |

| Li | st of T | Гables .                                      |                                                     | viii |  |  |

| Li | st of I | Figures .                                     |                                                     | ix   |  |  |

| 1  | Chaj    | pter 1: I                                     | ntroduction                                         | 1    |  |  |

|    | 1.1     | Overvi                                        | ew                                                  | 1    |  |  |

|    |         | 1.1.1                                         | Real-time Systems                                   | 1    |  |  |

|    |         | 1.1.2                                         | Motivation                                          | 1    |  |  |

|    | 1.2     | Object                                        | ives                                                | 3    |  |  |

|    |         | 1.2.1                                         | Thesis                                              | 4    |  |  |

|    | 1.3     | Summ                                          | ary of Contributions                                | 4    |  |  |

|    | 1.4     | Organi                                        | zation                                              | 5    |  |  |

| 2  | Chaj    | pter 2: R                                     | Related Work                                        | 7    |  |  |

|    | 2.1     | Thermal-Aware Design for Uniprocessor Systems |                                                     |      |  |  |

|    |         | 2.1.1                                         | General (Non-Real-time) Thermal-Aware System Design | 7    |  |  |

|    |         | 2.1.2                                         | Real-Time Thermal-Aware System Design               | 7    |  |  |

|    | 2.2     | Therm                                         | al-Aware Design for Multicore Processor Systems     | 8    |  |  |

|    |         | 2.2.1                                         | Control-Theoretic Based Designs                     | 8    |  |  |

|    |         | 2.2.2                                         | Proactive Methods                                   | 9    |  |  |

| 3  | Chaj    | pter 3: N                                     | Models and Definitions                              | 13   |  |  |

|    | 3.1     | Real-T                                        | ime Systems Model                                   | 13   |  |  |

|    |         | 3.1.1                                         | Jobs and Tasks                                      | 13   |  |  |

|    |         |                                               | 3.1.1.1 Periodic Task Model                         | 13   |  |  |

|    |         |                                               | 3.1.1.2 Sporadic Task Model                         | 14   |  |  |

|    |         |                                               | 3.1.1.3 Online and Offline Algorithms               | 14   |  |  |

|      | 3.1.2     | Scheduling Algorithms                        | 15 |

|------|-----------|----------------------------------------------|----|

| 3.2  | Model     | ing of Uniprocessor Systems                  | 15 |

|      | 3.2.1     | System Hardware Models                       | 15 |

|      | 3.2.2     | Periodic Resource Model                      | 16 |

|      | 3.2.3     | Software Model                               | 17 |

|      | 3.2.4     | Performance Modes                            | 18 |

|      | 3.2.5     | Mode Change Semantics                        | 18 |

|      | 3.2.6     | Selection of the Scheduling Algorithm        | 18 |

|      | 3.2.7     | Power/Thermal Model                          | 19 |

| 3.3  | Model     | ing of Multicore Processor Systems           | 20 |

|      | 3.3.1     | System Hardware Model                        | 20 |

|      | 3.3.2     | Software Model                               | 21 |

|      | 3.3.3     | Performance Modes                            | 22 |

|      | 3.3.4     | Power/Thermal Model                          | 23 |

|      | 3.3.5     | Generalized Model                            | 25 |

|      | 3.3.6     | Generalized System Software Model            | 25 |

| 3.4  | Contro    | ol Systems Basics                            | 26 |

|      | 3.4.1     | Basic Control Terminology                    | 27 |

|      | 3.4.2     | The Phase and Gain Margins                   | 28 |

| 3.5  | Classic   | cal Control Theory                           | 29 |

|      | 3.5.1     | Proportional Integral Derivative Controllers | 30 |

|      | 3.5.2     | Anti-Windup Controller                       | 31 |

| 3.6  | Moder     | rn Control Theory                            | 31 |

|      | 3.6.1     | Optimal Controllers                          | 33 |

|      | 3.6.2     | Model Predictive Controllers (MPC)           | 34 |

| 3.7  | Summ      | ary                                          | 35 |

| Chap | oter 4: T | Thermal-Resiliency on Uniprocessor Systems   | 36 |

| 4.1  | Introdu   | uction                                       | 37 |

4

|   | 4.2  | Method     | ology Overview                                              | 8 |

|---|------|------------|-------------------------------------------------------------|---|

|   | 4.3  | Models     |                                                             | 0 |

|   |      | 4.3.1      | The Testbed                                                 | 1 |

|   |      | 4.3.2      | Power/Thermal Derivations                                   | 4 |

|   | 4.4  | Control    | ler Design                                                  | 5 |

|   |      | 4.4.1      | Continuous Power Modes                                      | 6 |

|   |      | 4.4.2      | Active/Inactive Power Modes                                 | 0 |

|   | 4.5  | Therma     | l-Resiliency Calculation                                    | 2 |

|   | 4.6  | Validati   | on                                                          | 7 |

|   |      | 4.6.1      | Simulations                                                 | 7 |

|   |      | 4.6.2      | Experiments upon Hardware Testbed                           | 1 |

|   | 4.7  | Summa      | ry                                                          | 2 |

| 5 | Chap | oter 5: Th | nermal-Resiliency on multicore processor Systems            | 5 |

|   | 5.1  | Introduc   | etion                                                       | 6 |

|   | 5.2  | Models     |                                                             | 8 |

|   |      | 5.2.1      | Power/Thermal Derivations                                   | 9 |

|   | 5.3  | Control    | ler Design                                                  | 1 |

|   |      | 5.3.1      | State-Space Controller Details                              | 1 |

|   |      | 5.3.2      | Continuous Power Modes                                      | 2 |

|   |      | 5.3.3      | Stability Analysis and Optimal State Feedback               | 2 |

|   |      | 5.3.4      | Continuous Power Emulation with Active/Inactive Power Modes | 4 |

|   | 5.4  | Therma     | I-Resiliency Calculation                                    | 7 |

|   | 5.5  | Validati   | on                                                          | 9 |

|   |      | 5.5.1      | Simulations                                                 | 9 |

|   |      | 5.5.2      | Testbed Details                                             | 0 |

|   |      | 5.5.3      | Results                                                     | 2 |

|   |      | 5.5.4      | Experiments upon Hardware Testbed                           | 5 |

|   | 5.6  | Summa      | ry                                                          | 1 |

| 6   | Chapter 6: A Generalized Design Framework for Adaptive Real-Time System Resiliency 92 |           |                                          |  |  |  |  |

|-----|---------------------------------------------------------------------------------------|-----------|------------------------------------------|--|--|--|--|

|     | 6.1                                                                                   | Introdu   | action                                   |  |  |  |  |

|     | 6.2                                                                                   | Metho     | dology Overview                          |  |  |  |  |

|     | 6.3                                                                                   | System    | Models                                   |  |  |  |  |

|     |                                                                                       | 6.3.1     | System Hardware Models                   |  |  |  |  |

|     |                                                                                       | 6.3.2     | System Software Model                    |  |  |  |  |

|     | 6.4                                                                                   | Contro    | ller Model and the Design                |  |  |  |  |

|     |                                                                                       | 6.4.1     | System Constraints                       |  |  |  |  |

|     |                                                                                       | 6.4.2     | Control Integration of Design Objectives |  |  |  |  |

|     | 6.5                                                                                   | System    | Resiliency Calculation                   |  |  |  |  |

|     | 6.6                                                                                   | GSR F     | ramework Case Study                      |  |  |  |  |

|     |                                                                                       | 6.6.1     | System Hardware Model                    |  |  |  |  |

|     |                                                                                       | 6.6.2     | Hardware Testbed Details                 |  |  |  |  |

|     |                                                                                       | 6.6.3     | System Software Model                    |  |  |  |  |

|     |                                                                                       | 6.6.4     | Controller Design                        |  |  |  |  |

|     |                                                                                       | 6.6.5     | System Constraints                       |  |  |  |  |

|     |                                                                                       | 6.6.6     | Resiliency Calculation                   |  |  |  |  |

|     |                                                                                       | 6.6.7     | Discrete-Time Controller                 |  |  |  |  |

|     | 6.7                                                                                   | Validat   | ion                                      |  |  |  |  |

|     |                                                                                       | 6.7.1     | Simulations                              |  |  |  |  |

|     |                                                                                       | 6.7.2     | Results                                  |  |  |  |  |

|     | 6.8                                                                                   | Conclu    | sions                                    |  |  |  |  |

| 7   | Chap                                                                                  | oter 7: C | Conclusion and Future Work               |  |  |  |  |

|     | 7.1                                                                                   | Future    | Works Beyond the Thesis                  |  |  |  |  |

|     |                                                                                       | 7.1.1     | Multi-Mode Physiological Control-Systems |  |  |  |  |

| Li  | st of P                                                                               | Publicati | ons                                      |  |  |  |  |

| A T | ODEAU                                                                                 | DIV       | 120                                      |  |  |  |  |

## A APPENDIX A: B APPENDIX B: **B.2** B.3 **B.4** B.5 **B.6** B.7 References

## LIST OF TABLES

| 1.1 | The Contribution of each Chapter                                 | 6   |

|-----|------------------------------------------------------------------|-----|

| 2.1 | Thermal-aware researches and their contributions                 | 12  |

| 4.1 | Testbed parameters for uni-processor simulations                 | 59  |

| 5.1 | Testbed parameters for multicore processor simulations           | 80  |

| B.1 | Testbed parameters for generalized system resiliency simulations | 141 |

## LIST OF FIGURES

| 3.1  | The sampling and mode change in the thermal control system (uni-processor systems)                 | 17 |

|------|----------------------------------------------------------------------------------------------------|----|

| 3.2  | The basic equivalent circuit for a working CPU and its working environment                         | 20 |

| 3.3  | The sampling and mode change in the thermal control system (multicore processor system).           | 22 |

| 3.4  | The thermal model of the CPU and its working environment                                           | 24 |

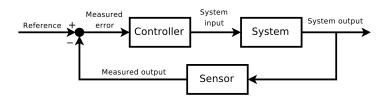

| 3.5  | A control system with a feedback                                                                   | 27 |

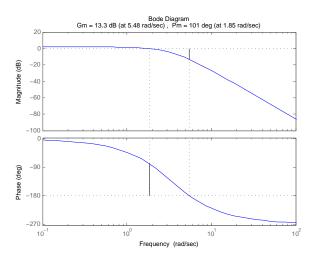

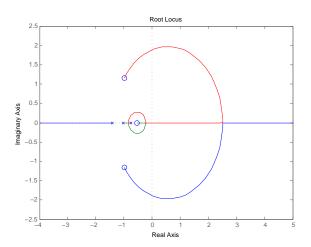

| 3.6  | The phase margin and the gain margin of a system                                                   | 29 |

| 3.7  | The root locus of transfer function $G(s)$                                                         | 30 |

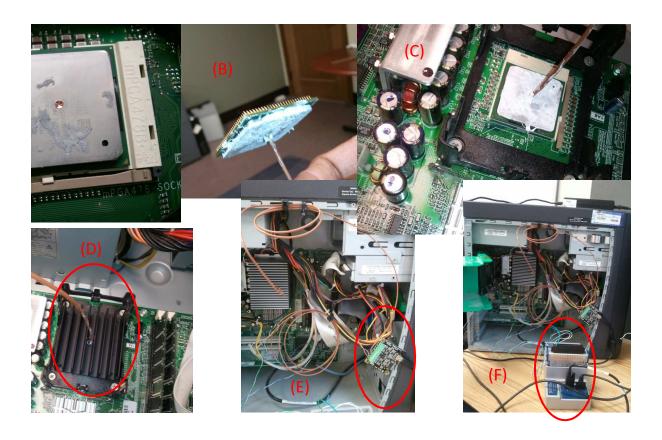

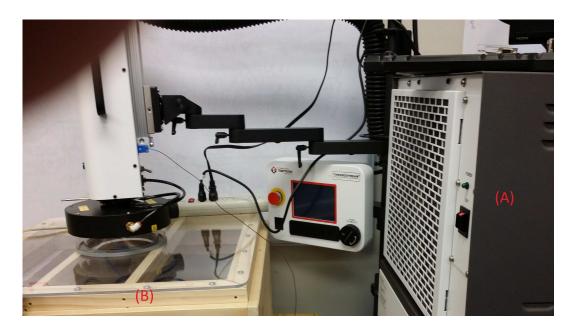

| 4.1  | The implementation details of the testbed                                                          | 42 |

| 4.2  | The physical testbed preparation steps                                                             | 43 |

| 4.3  | The basic equivalent circuit for a working CPU and its working environment                         | 44 |

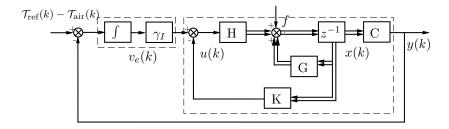

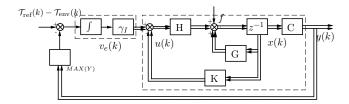

| 4.4  | The thermal control design with state feedback and integral actuator                               | 46 |

| 4.5  | The simplified power and modulation relationship                                                   | 51 |

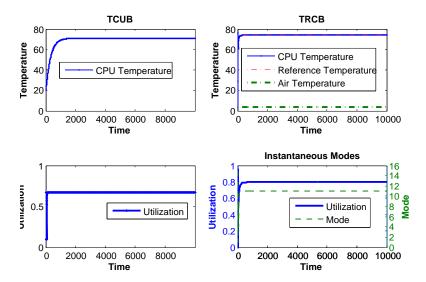

| 4.6  | Fixed $\mathcal{T}_{air}$ for Simulation. Left plots represent TCUB and right plots represent TCRB | 59 |

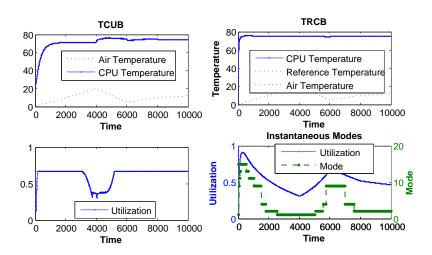

| 4.7  | Simulation comparison under varying $T_{air}$                                                      | 60 |

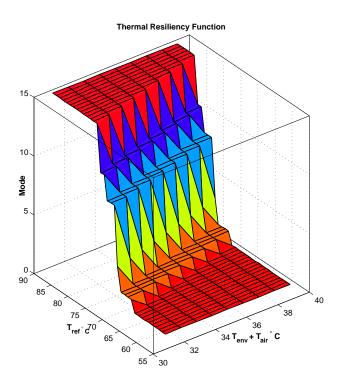

| 4.8  | Thermal resiliency over modes and $\mathcal{T}_{ref}$                                              | 61 |

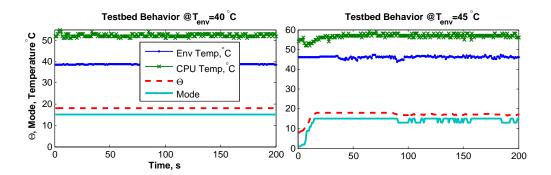

| 4.9  | The testbed behavior under different $\mathcal{T}_{env}$ values                                    | 62 |

| 4.10 | Simulated Thermal Resiliency Comparison with Testbed Data                                          | 63 |

| 4.11 | The Thermal Forcing System (A) and the Thermal Cabinet (B)                                         | 63 |

| 5.1  | The sampling and mode change in our thermal control system                                         | 69 |

| 5.2  | The multicore equivalent electrical circuit                                                        | 70 |

| 5.3  | The thermal control design with state feedback and integral actuator                               | 71 |

| 5.4  | The simplified power and modulation relationship                                                   | 75 |

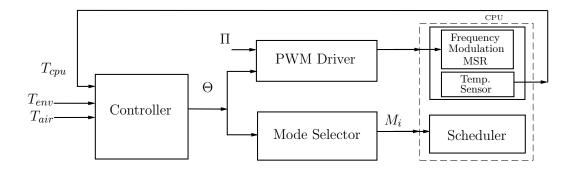

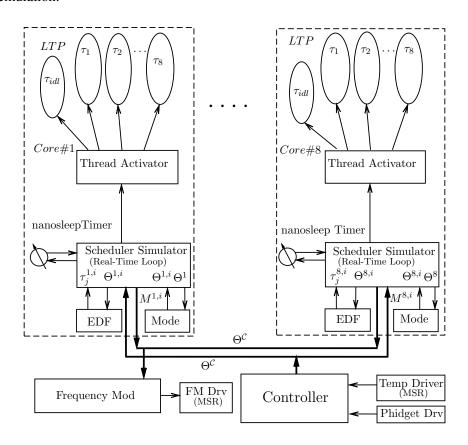

| 5.5  | The block diagram of the testbed implementation                                                    | 81 |

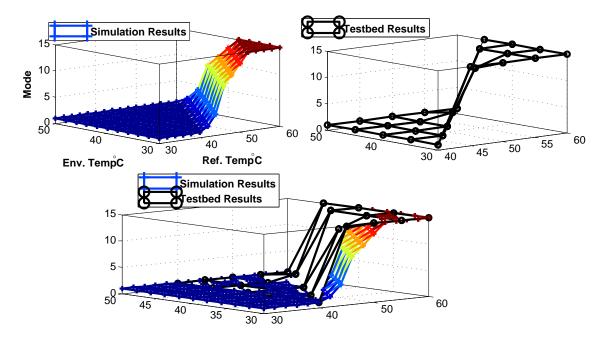

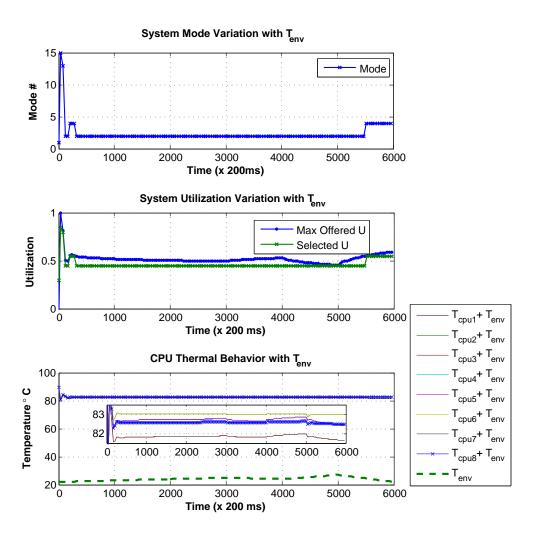

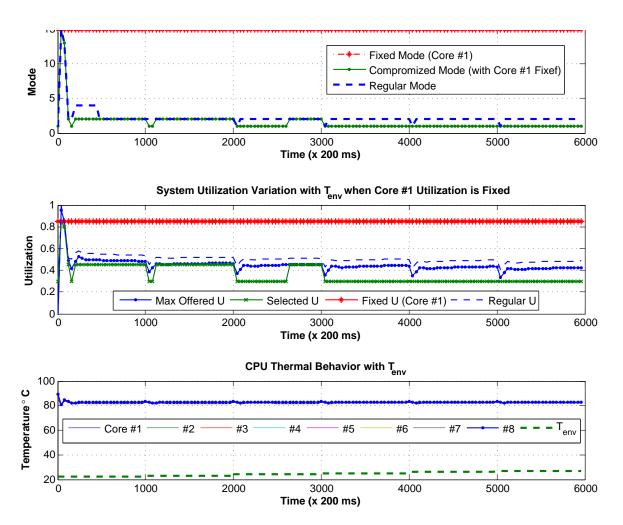

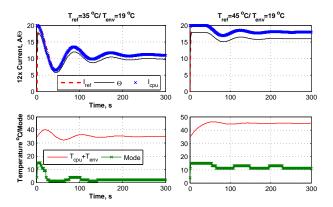

| 5.6  | The controller capability over $\mathcal{T}_{env}$ temperature variation                           | 83 |

| 5.7  | The mode variation of cores under different environment temperatures                               | 84 |

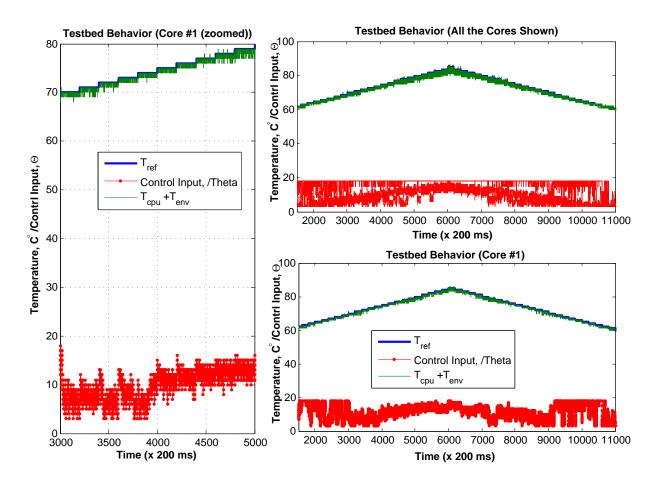

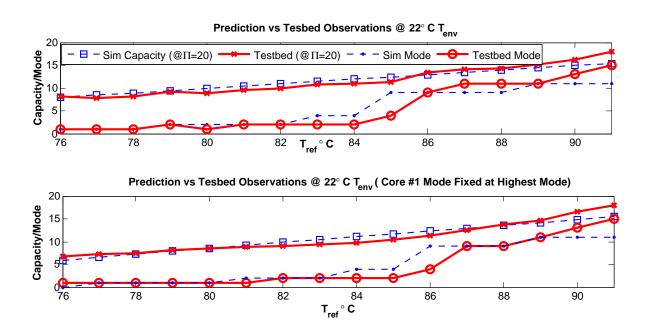

| 5.8  | The controller tracking capability                                                                                  | 87  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | The controller behavior under $\mathcal{T}_{env}$ temperature variations                                            | 88  |

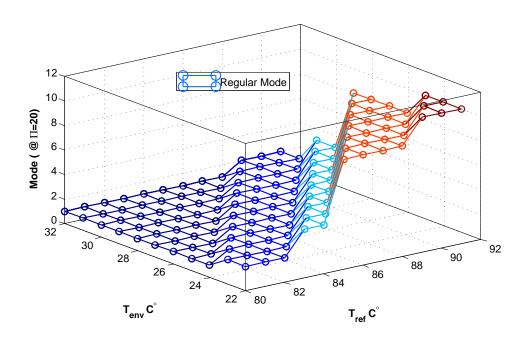

| 5.10 | Thermal Resiliency for the system for all the possible $\mathcal{T}_{env}$ and $\mathcal{T}_{ref}$ values           | 88  |

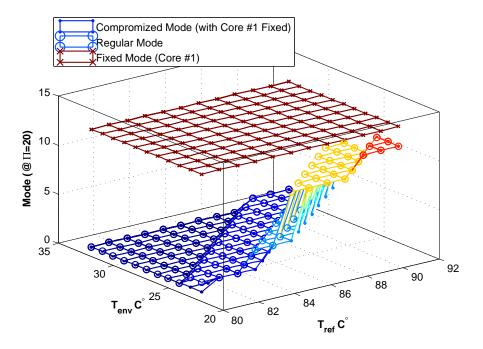

| 5.11 | Thermal resiliency when a task is statically pinned to a core                                                       | 89  |

| 5.12 | The inverse resiliency                                                                                              | 90  |

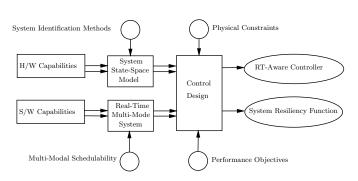

| 6.1  | GSR Framework Methodology                                                                                           | 95  |

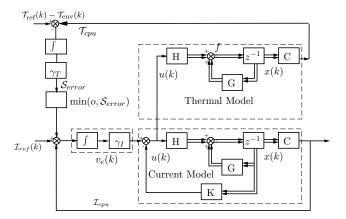

| 6.2  | The RAS controller                                                                                                  | 04  |

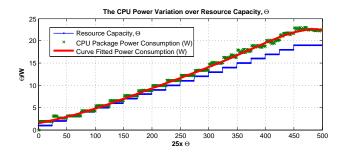

| 6.3  | The testbed CPU power variation                                                                                     | 06  |

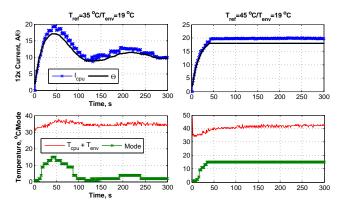

| 6.4  | The effect of the reference temperature, $\mathcal{T}_{ref}$ , on CPU current $\mathcal{I}_{cpu}$                   | 11  |

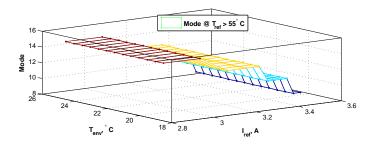

| 6.5  | The mode variation over external temperature, $\mathcal{T}_{	ext{env}}$ and reference current, $I_{ref}$            | 11  |

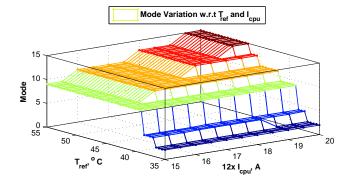

| 6.6  | The mode variation over reference temperature, $\mathcal{T}_{\text{ref}}$ and CPU current, $I_{cpu}$                | 11  |

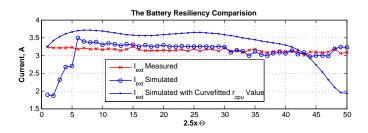

| 6.7  | The calculated and measured external current comparison                                                             | 12  |

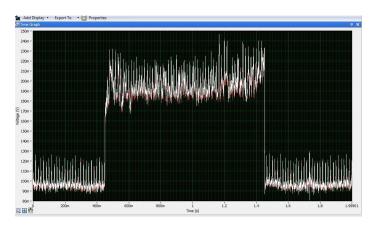

| A.1  | The voltage variation of shunt resister for random workload                                                         | 126 |

| B.1  | The effect of the reference temperature, $\mathcal{T}_{\text{ref}}$ on CPU current $\mathcal{I}_{cpu}$ from testbed | 42  |

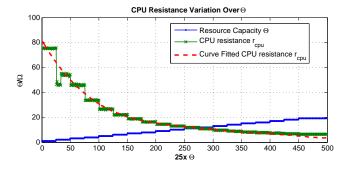

| B.2  | The CPU impedance variation of the testbed.                                                                         | 142 |

## **CHAPTER 1: INTRODUCTION**

#### 1.1 Overview

#### 1.1.1 Real-time Systems

Real-time systems include the notions of both *logical* and *temporal correctness* [7]. There are two main type of real-time systems: the soft-real-time systems, such as video decoding, can *tolerate occasional deadline misses*; the hard-real-time systems, such as avionics and radar control systems, can not tolerate deadline misses and have *strict temporal requirements*. Real-time systems work as a functional manager in consumer electronics and cyber-physical systems. Today's standard computing platform [40, 41]—multicore processors—are often the underlying computing architecture of these systems. Furthermore, their correct functionality upon various conditions is extremely important. For example, in the automobile industry, the modern vehicle braking system consists of hard real-time computer and electro mechanical actuators; the accuracy of the vehicle braking action in various environmental conditions determines the safety of the driver. Therefore, the system designer should assure the correct functionality of the real-time computer and mechanical parts for all the operating conditions of the system.

#### 1.1.2 Motivation

Today, multicore processors with advanced capabilities and high clock frequencies are common [60, 38]. Also, many manufacturers offer complete embedded computers, which include a powerful processor, I/O interface, and communication interfaces in a single compact printed circuit board [61]. These modern embedded computers are ideal for contemporary hard-real-time system development as they have higher computing capabilities and reliability, and are less expensive. Despite these advantages, modern real-time systems face many physical challenges and hardware constraints at design and during runtime. For example, the excessive processor thermal dissipation and high power consumption [3] due to higher clock rates, high leakage current [52], and increased chip package density—dark silicon [82, 25] issues—are common problems in modern microprocessor based systems. As a solution to the excess thermal dissipation and larger power consumption, these real-time systems may set to operate at a lower clock frequency or

dynamically adjust the processor clock frequency [84, 85]. However, lower clock frequency degrades the performance of the system, arbitrary clock frequency reduction may affect the underlying real-time system and fail to achieve its essential task deadlines. Therefore, the system designer needs to analyze multiple system constraints towards any remedial solution (a tradeoff) for excessive thermal dissipation and should choose the best possible solution. Furthermore, as an example of an embedded system where thermalstress analysis is essential, consider microprocessors found in implantable medical devices (IMDs). IMDs are increasingly being used to treat various diseases and medical conditions (e.g., pacemakers for heart disease or neural implants to restore hearing/vision). However, recent studies [53, 55] have shown that the heat dissipated from IMDs due to the microprocessor activity is non-negligible. Thus, designing IMDs with minimum thermal dissipation is critical as medical research has shown that a temperature increase of even  $1^{\circ}C$  can have long-term effect on tissue [54] and, in the extreme, death may even result from excessive tissue heating [70]. Complicating the safe thermal design of IMDs, body temperature naturally fluctuates over time and varies depending on location [50]. An IMD designer must balance (under temperature fluctuations) the real-time computational requirements of the device with the non-harmful thermal operating limits. In the presence of an increased surrounding temperature, an IMD will have to reduce its computational load to prevent tissue damage due to heat<sup>1</sup>. However, as the correct and safe functioning of the IMD is an absolute requirement, the system designer requires techniques to formally verify the effect of different body temperatures on the correct operation of the IMD. Similarly, as a less safety-critical example, consider how the quality of audio/video decoding may degrade in a hand-held device as the system reacts to increases in temperature by reducing computational processing (e.g., via instruction fetch toggling). Ideally, a system designer would like to determine how much the performance will degrade under different thermal operating conditions.

Until the last decade, real-time systems were mainly constrained by the CPU processing power, as the CPU processing power was the most scarce resource. Also, the cost of real-time hardware was substantially high, compared to the cost of software design and testing altogether [76]. For the past couple of years, the cost per tera flop has been reduced exponentially [51]. By now, the modern real-time system manufacturers face different challenges; today, real-time software engineering has grown as a different discipline [18]. The real-time software design, development, and testing cost is the highest portion of the

<sup>&</sup>lt;sup>1</sup>As IMD microprocessors typically do not have DVS capabilities, an IMD may have to reduce non-essential tasks such as communication with other nodes in a body-area network [83].

system development cost due to its size and complex nature. For example, resource, energy, and thermal efficient real-time multicore processor systems design and development process are hard and need many design hours. Lack of proper frameworks and the difficultly involved in streamlining the real-time design process can explain this higher cost. Furthermore, real-time system designers have to concentrate more on the software design and the implementation issues, when systems experience physical and hardware constraints. Thus, designing a reliable system (provisioning) for different hardware and physical constraints has become a central issue in real-time system design paradigm. Furthermore, the optimized CPU resources allocation on each task on a real-time task system is fundamentally hard question. Also, under various physical constraints, the real-time system design needs to gracefully degrade the quality of service, without interfering the essential real-time services on the system.

Modern real-time systems operate on multi-inputs and multi-output environments. They need to adapt to various physical and logical constraints that are dynamic in nature. These systems need to dynamically allocate the resources for the essential activities at a given time. Over the years, control-theoretic based methods have shown to be the best, as they have the capability to analyze and control multiple inputs and outputs precisely at run-time.

There are many important previous results on thermal-aware and power-aware real-time system designs (see Chapter 2). But, none of them addresses the issues of hard-real-time performance guarantee upon multiple unpredictable physical and hardware-constraints for multi-modal system. Therefore, in this thesis, we try to fill this gap. We propose a generalized control-theoretic system-resiliency framework.

In the rest of this chapter, we first discuss the objectives as well as the contributions of our work. Then we will outline the rest of the thesis in the end of this chapter.

## 1.2 Objectives

In this thesis, we introduce a new metric called *system-resiliency* which characterizes the maximum prior unknown unpredictable external stresses that any hard-real-time performance mode can withstand. Our proposed system-resiliency framework addresses resiliency determination for real-time systems with physical and hardware limitations. Furthermore, our framework advises the system designer about the feasible trade-offs between different system resources. For example, in a solar-powered device, a sunny day benefits the device's battery charging-level, but may negatively affect the performance of the CPU (by raising

the environmental temperature and forcing the CPU to run a lower power level to reduce thermal dissipation). Therefore, finding a balanced trade-off between these two external factors for a better system design is essential.

The runtime efficiency is also an important factor to consider during the design process. Therefore, we study the effective scheduling of real-time tasks with intra-task parallelism to reduce the energy-consumption of multiprocessor platforms. Furthermore, we investigate the potential temperature rise of a uniprocessor due to task execution. We show the thermal effect of periodic resource due to different resource capacity and investigate the influences of the peak-temperature of a uniprocessor.

The concept we introduce as system-resiliency closely resembles the stress test in materials engineering. Thus, our design framework and analysis may be classified as a *system-stress-analysis* for real-time systems.

#### **1.2.1** Thesis

The thesis of this document is:

Our newly introduced metric, *system-resiliency* defines the maximum external stresses that any hard-real-time system mode can withstand before violating timing constraints. A carefully designed control-theoretic framework effectively facilitates the ability of the system designers to quantify the system-resiliency. Furthermore, we consider effective scheduling of real-time tasks with intra-task parallelism to reduce the energy consumption of multiprocessor platforms, to maintain the energy-efficiency of the system design.

## 1.3 Summary of Contributions

The main contributions of this thesis are listed as the follows:

1. As a proof of concept, we propose a subset of system-resiliency, a new metric, called *thermal-resiliency* which characterizes the maximum external thermal stress that any hard-real-time performance mode can withstand (see Chapter 4). We show how to solve some of the issues and challenges of designing predictable real-time systems that guarantee hard deadlines even under transitions between modes in an unpredictable thermal environment where environmental temperature may dy-

namically change, using our new metric. In our framework, the system designer specifies a set of hard-real-time performance modes under which the system may operate automatically adjusts the real-time performance mode based on the external thermal stress.

- 2. We extend the derivation of thermal-resiliency, that was proposed for uniprocessor systems to multicore systems and determines the limitations of external thermal stress that any hard-real-time performance mode can withstand (see Chapter 5). Our control-theoretic framework allows system designer to allocate asymmetric processing resource upon a multicore processor and still maintain thermal constraints.

- 3. We introduce the *generalized system-resiliency* (GSR) design framework that predictably quantifies the real-time performance level attainable under unpredictable dynamic external conditions (see Chapter 6). We show how the designer derives the optimal supported-modes for a multi-constrained system under various processing resources allocations while maintaining maximum system constraints.

- 4. The fine-grain power and energy consumption of a task system is essential for balanced and optimized task partitioning on a multicore processer. Therefore, we investigate the potential utility of parallelization for meeting real-time constraints and minimizing energy. We consider malleable Gang scheduling of implicit-deadline sporadic tasks upon multiprocessors.

- 5. Verifying theoretical results is essential in real-time system design. Therefore, we implemented a testbed to verify our theoretical results upon the testbed runs (see Appendix A and Appendix B).

## 1.4 Organization

The following table gives the details of each chapter:

Table 1.1: The Contribution of each Chapter

| Chapter # Contribution                                                     |                                                                       |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Chapter 3 Models and definitions used in rest of the thesis                |                                                                       |  |  |

| Chapter 4                                                                  | Thermal-resiliency calculation details on uniprocessor systems        |  |  |

| Chapter 5                                                                  | Thermal-resiliency calculation details on multicore processor systems |  |  |

| Chapter 6                                                                  | Generalized system-resiliency calculation details                     |  |  |

| Chapter 7 Conclusion and future work beyond the final dissertation of this |                                                                       |  |  |

| Appendix A Details on practical implementation, such as                    |                                                                       |  |  |

|                                                                            | temperature calculation, control parameter derivations,               |  |  |

|                                                                            | and system-identification details                                     |  |  |

| Appendix B Further details on multicore processor model                    |                                                                       |  |  |

|                                                                            | and multicore processor testbed details                               |  |  |

## **CHAPTER 2: RELATED WORK**

In this chapter, we present prior research on thermal and power-aware real-time systems design techniques. Also, we briefly present some of the works related the energy estimation on parallizable workloads and the maximum temperature estimation of a uniprocessor upon real-time task execution.

### 2.1 Thermal-Aware Design for Uniprocessor Systems

In this thesis, we introduce the system-resiliency framework that addresses resiliency determination for real-time systems with physical and hardware constraints. Toward this final goal, first we present the thermal-resiliency framework for uniprocessor in Chapter 4 and the multiprocessor thermal-resiliency framework details in Chapter 5. Furthermore, to properly understand the importance of our results (explained in the Chapter 4 and Chapter 5), in this subsection, we give a brief, high-level overview of previous research in both general (non-real-time), thermal-aware system design and real-time-specific thermal-aware design.

#### 2.1.1 General (Non-Real-time) Thermal-Aware System Design

For non-real-time systems, Brooks and Martonosi ([12]) investigated major components of any dynamic thermal management scheme and suggested policies and mechanisms for implementing dynamic thermal management for current and future high-end CPUs. They evaluated the benefits of using dynamic thermal management to reduce the cooling system costs of CPUs and developed an architectural-level power modeling tool called Wattch. For the micro-architecture level of thermal modeling, Skadron et al. ([78]) proposed a compact, dynamic, and portable thermal model and a tool called *HotSpot* for use at the architecture level for micro-architectures.

#### 2.1.2 Real-Time Thermal-Aware System Design

For real-time systems in the online setting, Bansal and Pruhs [6] explored algorithms for minimizing both peak-temperature and energy efficiency for online jobs with deadline constraints. In the off-line setting, previous work on scheduling under thermal constraints has followed two main approaches: reactive and

proactive schedulers. In a reactive scheduler, the processor speed is reduced in response to a thermal trigger. Wang et al. [89] studied schedulability analysis under the reactive setting. In the proactive setting, the speed schedule for the processor is determined at design time. Chen et al. [16] addressed proactive scheduling for the periodic task model. Quan and Zhang [68] consider feasibility analysis of leakage-aware periodic tasks under temperature constraints. However, previous work on both settings assumed either simple task models or the existence of "ideal" processor speeds. Also, they have not addressed the issues related to multicore processor based systems. Recent dynamic temperature management strategies also exist for multiprocessor real-time systems [15, 13, 31]; however, most of these focus upon static speed-assignment approaches and not a proactive schedule. Thermal analysis has also been studied in the context of web servers [26], but hard deadlines are not guaranteed. The work by Y. Fu et al. [37] and X. Fu et al. [36] address handling unpredictable thermal events; however, the results do not provide any *a priori* guarantees that may be used to equate real-time performance and thermal resiliency.

### 2.2 Thermal-Aware Design for Multicore Processor Systems

Multicore processor-based systems that operate under external temperature constraints are an important focus in real-time systems research. In this subsection, we overview the prominent work and previous research on thermal-aware, real-time thermal-aware system design, and multicore real-time systems at high-level. Furthermore, we discuss the work on scheduling under thermal constraints, under two main approaches: reactive and proactive schedulers. Although there are many scattered individual works that address the thermal-aware design, power-aware design, and real-time multicore processor systems design, no prior work suggested a generalized design framework for graceful degradation of quality of service of a real-time system.

#### 2.2.1 Control-Theoretic Based Designs

Ghosh et al. [42] proposed a framework for mapping, the level of service and resource requirements for dynamic environmental conditions. They presented an integrated QoS optimization, which is performed using Q-RAM [69]. Lu et al. [62] proposed adaptive utilization based multi-processors real-time design for constrained MIMO systems. Fu et al. [34] proposed a control based solution for simultaneous thermal and timeliness guarantees for distributed real-time embedded systems running in unpredictable environments.

In contrast to these work, that rely on mapping techniques to adopt the varying environmental conditions, we provide the system designer real-time and performance guarantee.

Yao et al. [93] discussed an online adaptive mechanism, based on the utilization control, for multiprocessor real-time settings with online system identification and LQ controllers for a system with multiple constraints. Fu et al. [33] suggested a solution, that integrates core-level feedback control with processor-level optimization to minimize dynamic and leakage power consumption of a multi-core real-time embedded system. Their research may offer accurate control solutions suitable for soft real-time systems that needs to adjust the utilization by means of task rate adjustments at runtime. However, their methods have limited applicability for systems that need hard real-time and multi-mode capabilities. Seo et al. [71] studied energy-efficient multicore real-time scheduling using processor-wide DVFS; however, their results do not provide any hard real-time or performance guarantee. Further, each of these prior results do not provide a mechanism to specify the graceful degradation of the system's operating modes in an unfavorable environment.

#### 2.2.2 Proactive Methods

In this subsection, we give the previous work on thermal-aware real-time systems design focused on proactive scheduling based techniques. In a reactive scheduler, the processor speed is reduced in response to a thermal trigger (e.g.,the maximum system operating temperature is reached). In the proactive setting, the speed schedule for the processor is determined at design time. Chantem et al. [14] made an interesting observation for maximizing work load under thermal constraints. While working with proactive scheduling, the authors show that the scheduler which maximizes workload under thermal constraints must be a periodic. The authors determined a speed schedule such that the peak temperature constraints were met and total work completed was maximized using a DVFS control policy for processors with discrete speed levels.

Wang et al. [87, 88, 89] studied temperature-constrained real-time systems and performed schedulability analysis of a task system. They computed upper bound on the worst-case delay for tasks with arbitrary job arrivals for both first-in-first-out (FIFO) and static-priority (SP) scheduling algorithms, and also showed that this simple reactive speed control decreased the response time of tasks compared with any constant-speed scheme. However, the previous aforementioned work on proactive and reactive schemes

assumes either simple task models or the existence of "ideal" processor speeds which may not be feasible even by using the recent top-of-the-line microprocessors.

There has been extensive research work on finding an optimal feasible speed for minimizing energy consumption as well as temperature minimization. Finding an optimal speed is always possible under the assumption that the processor can run at any speed. Yao et al. [92]. formulated speed scaling problems as scheduling problems to minimize energy consumption. The authors developed an optimal off-line greedy polynomial-time algorithm, and also two online algorithms. Bansal et al. [6] explored algorithms for minimizing both peak temperature and energy efficiency, and proposed an algorithm with constant approximation ratio with respect to the optimal algorithm for managing temperature. Hung et al. [49]. investigated both power-aware and thermal-aware approaches and found a power-aware approach alone is not able to address the temperature challenge; furthermore, many low-power techniques have insufficient impact on chip temperature because they do not directly target the spatial and temporal behavior of the operating temperature. DTM strategies also exist for multiprocessor real-time systems [15, 14, 31]; however, most of these focus upon static speed-assignment approaches and not on a proactive schedule. Real-time thermal analysis has been studied in the context of web servers [26], but hard deadlines are not guaranteed. Real-time scheduling under thermal constraints has also been evaluated for multi-function phased array radar systems via energy minimization [43, 42]. Numerous results exist for the periodic resource model without thermal settings. Shin and Lee [73, 74] obtained linear-time algorithms for determining the capacity of aperiodic resource (given a periodic task system); however, the allocation may potentially over-provision the amount of capacity needed by the task system leading to wasted processor resources. Easwaran [23, 24] devised an exact algorithm for capacity determination and for determining the best period of repetition. While these exact algorithms ensure that no processing resources are wasted, they may require exponential-time in the worst case. Bini et al. [10] studied minimization of energy consumption using periodic-resource considering discrete speed DVFS processor. Fisher and Dewan [28] developed a polynomial-time approximation algorithm which permits a system designer to choose a trade-off between accuracy and response time based on their requirements for non-thermal settings. In a related publication, Fisher [29] proposed a polynomial-time approximation for determining the period of repetition in aperiodic resource.

The Table 2.1 shows the summary of previous results. Note that  $\sqrt{ }$  and x indicate wether a particular research contribute to a given category or not respectively.

The analysis of the previous work does not answer the following: is there any framework, that quantifies the impact of real-time timing properties upon unpredictable external constraints and advises the designer about the trade-offs between various physical and hardware constraints? Due to lack of an answer to this question, we introduce a metric called system-resiliency which characterizes the maximum external stresses that any hard-real-time performance mode can withstand. This is a generalized framework for hard-real-time system design process. This proposed framework addresses resiliency determination for real-time systems with physical and hardware limitations. Also, it serves as a design tool that predicts the QoS or mode degradation due to external constraints.

Our system-resiliency framework provides a powerful model of cyber and physical system behavior. Theocratically, the correctness of the system-resiliency is explainable; however, it is too abstract to demonstrate the finer behavior of real-time system under multi-constrained environment. Therefore, we derive the system-resiliency for a sub-domain (lower-dimension) to demonstrate its correctness in practice. Our previous work [46, 48] introduces thermal resiliency – a design metric that quantifies the external thermal constraints. Finally, we introduce the generalized system-resiliency to complete our work.

Table 2.1: Thermal-aware researches and their contributions

| Research                  | Real-<br>Time | Multi-<br>Core | Control-<br>Theoritic       | Deployment       | Contribution                                             |

|---------------------------|---------------|----------------|-----------------------------|------------------|----------------------------------------------------------|

| Brooks et al. [12]        | X             | X              | X                           | -                | Framework (DTM triggers, responses, init policies)       |

| Chen et al. [15]          |               | X              | X                           | Proactive        | -                                                        |

| Zanini et al. [94]        | X             |                | √(MPC)                      | X                | -                                                        |

| Cohen et al. [17]         | X             | X              | √(Optimal)                  | X                | -                                                        |

| Fu et al. [35]            | $\checkmark$  |                | $\sqrt{\text{(Robust)}}$    | X                | DRE, simultaneous thermal-timeliness optimization (MIMO) |

| Ma et al. [63]            | X             | X              | X                           | -                | Microcode implementation                                 |

| Skadron. [79]             | X             | X              | x                           | CPU architecture | Hybrid architectural DTM                                 |

| Wang et al. [90]          | X             |                | √(MPC)                      | x                | Simultaneous power-frequency optimization (MIMO)         |

| Wang et al. [88]          | <b>√</b>      | X              | x                           | -                | Framework (task degradation analysis)                    |

| Fu et al. [37]            |               | X              | $\sqrt{\text{(Classical)}}$ | x                | Anti-windup                                              |

| Skadron et al. [78]       | X             | X              | X                           | -                | Framework (Hotspot)                                      |

| Coskun et al. [19]        | x             |                | X                           | O/S              | OS level implementation                                  |

| Ferreira et al. [27]      | <b>√</b>      | X              | х                           | -                | Framework (System wide RC model)                         |

| Skadron et al. [77]       | X             | X              | $\sqrt{\text{(Classical)}}$ | x                | Localized DTM techniques                                 |

| Hettiarachchi et al. [46] | <b>√</b>      | X              | <b>√</b>                    | <b>√</b>         | Hard-real-time, thermal-resiliency                       |

| Hettiarachchi et al. [48] | <b>√</b>      |                | <b>√</b>                    | <b>√</b>         | Hard-real-time, thermal-resiliency                       |

## **CHAPTER 3: MODELS AND DEFINITIONS**

In this chapter, we will introduce a basic overview on notations, concepts, and models used in the thesis. However, we only provide a very concise yet complete overview on the concepts and theories and details can be found in relevant textbooks.

### 3.1 Real-Time Systems Model

In next sub sections we present real-time models, notations, and definitions.

#### 3.1.1 Jobs and Tasks

Any real-time system can be considered as a set of concurrent *tasks*. Each task generates an infinite number of jobs. The jobs from a same task obey sequential order of execution.

**Definition 1** (Job). A real-time job j = (A, E, D) is characterized by three parameters, an arrival time A, an execution requirement E, and a deadline D, with the interpretation that this job must receive e units of execution over the interval [A, D).

#### 3.1.1.1 Periodic Task Model

In the periodic task model [7], a task  $T_i$  is completely characterized by a 4-tuple  $(a_i, e_i, d_i, p_i)$ , where

- 1. the *offset*  $a_i$  denotes the instant at which the first job generated by this task becomes available for execution.

- 2. the execution requirement  $e_i$  specifies an upper limit on the execution requirement of each job generated by this task.

- 3. the *relative deadline*  $d_i$  denotes the temporal separation between each jobs arrival time and deadline. A job generated by this task arriving at time-instant t has a deadline at time-instant  $(t + d_i)$ .

- 4. the  $period p_i$  denotes the temporal separation between the arrival times of successive jobs generated by the task.

That is,  $T_i = (a_i, e_i, d_i, p_i)$  generates a potentially infinite succession of jobs, each with execution-requirement  $e_i$ , at each instant  $(a_i + kp_i)$  for all integer  $k \ge 0$ , and the job generated at instant  $(a_i + kp_i)$  has a deadline at instant  $(a_i + kp_i)$  [7].

#### 3.1.1.2 Sporadic Task Model

The sporadic task model differs from the periodic task model because of its inability to express job arrival time until the run-time moment. A sporadic task system is comprised of a finite collection of sporadic tasks [7].

**Definition 2** (Sporadic Task). A sporadic task  $\tau_i = (e_i, d_i, p_i)$  is characterized by a worst-case execution requirement  $e_i$ , a (relative) deadline  $d_i$ , and a minimum inter-arrival separation  $p_i$ . Such a sporadic task generates a potentially infinite sequence of jobs, with successive job-arrivals separated by at least  $p_i$  time units. A sporadic task system  $\tau \stackrel{def}{=} \{\tau_1, \dots, \tau_n\}$  is a collection of n such sporadic tasks.

The utilization indicates the amount of time that system becomes busy due to tasks in a task model. Formally, the the utilization  $U_i$  of a periodic or sporadic task  $T_i$  is defined to be the ratio of its execution requirement to its period:  $U_i = \frac{e_i}{p_i}$ . The utilization  $U(\tau)$  of a periodic or sporadic task system  $\tau$  is defined to be the sum of the utilizations of all tasks in  $\tau: U = \sum_{T_i \in \tau} U_i$ . for any task system under any known uni-processor scheduling algorithm, the utilization should not exceed 1 and cannot schedulable otherwise; however, this does not necessarily say that a system is scedulable if the utilization is under 1. This dissertation primarily focuses upon real-time work generated under the more general sporadic task model.

#### 3.1.1.3 Online and Offline Algorithms

In *offline* scheduling algorithms, all scheduling decisions are made before the system begins executing. These scheduling algorithms select jobs to execute by referencing a table describing the pre-determined schedule. Usually, offline schedules are repeated after a least common multiple (LCM) period. The offline schedulers require the full knowledge of the job before the they execute.

In *online* scheduling algorithms, scheduling decisions are made without specific knowledge of jobs that have not yet arrived. These scheduling algorithms select jobs to execute by examining properties of

active jobs. Online algorithms can be more flexible than offline algorithms since they can schedule jobs whose behavior cannot be predicted ahead of time.

#### 3.1.2 Scheduling Algorithms

The job execution selection in a CPU is done by the scheduler. The scheduler uses a scheduling algorithm to achieve this task. Typical examples of scheduling algorithms are earliest deadline first (EDF), least laxity first (LLF), rate monotonic (RM), deadline monotonic (DM), etc. In EDF algorithm at each time-instant t schedule the job j active at time-instant t whose deadline parameter is the smallest [7]. Similarly, in LLF algorithm, the job with the smallest laxity has highest priority at all times. One very well-known fixed priority scheduling algorithm is the RM algorithm. In this algorithm, the task period is used to determine priority [58]. Tasks with shorter periods have higher priority. In DM algorithm, the deadline is used to determine the the priority. Tasks with shorter deadline have higher priority [58].

Depending on the requirement, a system might employ *online* or *off-line* scheduling algorithms. For example, if system has a well predefined task set and there are no runtime task modifications expected, then an off-line algorithms might be suitable. The off-line scheduling algorithms are suitable for systems with sufficient resources. However, an off-line scheduling algorithm cannot be used to withstand continuously varying dynamic task/job management. Sometimes, an online scheduling techniques which take the dynamics of the task into account is implemented [58]. Usually online scheduling algorithms of above kind use either control-theoretic or heuristic methods based approaches.

The primary intention of this document is to review work that analyzes the effects of resilient behavior on a real-time system. Therefore, this document describes the outcomes of the research on different scheduling techniques as applicable.

In next subsections, we give details on the system hardware model related to the uniprocessor systems.

## 3.2 Modeling of Uniprocessor Systems

#### 3.2.1 System Hardware Models

We consider a single processor system with rudimentary DPM capabilities of only *active* and *inactive* power modes. At any time t > 0, we denote the instantaneous CPU power as  $\mathcal{P}_{\text{cpu}}(t)$ . The processor

dissipates thermal power at a constant rate  $\mathcal{P}_{cpu}(t) = \mathcal{P}_{act}$  in the active mode and  $\mathcal{P}_{cpu}(t) = \mathcal{P}_{inc}$  in the inactive mode and these power dissipation corresponds to the current of the equivalent electrical circuit. While the processor is active, it dissipates heat at a constant rate  $\mathcal{P}_{cpu}(t) = \mathcal{P}_{act}$ . For the inactive mode, we will assume that the processor still continues to dissipate a small amount of power  $\mathcal{P}_{cpu}(t) = \mathcal{P}_{inc}$ . Also, we assume that processor consumes  $e_{act}$  amount of energy to activate from inactive mode and  $e_{inc}$  amount of energy to deactivate from the active mode. Even though the processor may be minimally active while in the low-power state, we will assume (as a pessimistic assumption for the purpose of schedulability analysis) that the processor is unavailable for task execution during this interval. If the aforementioned assumption does not hold, the system will behave "better" than the analysis and our results will continue to be valid. We believe this model of active/inactive modes is a very general model, applicable to a large number of available embedded processors with rudimentary DPM capabilities<sup>1</sup>.

Furthermore, the active/inactive mode setting can model processing platforms that have limited thermal management capabilities. For example, in a processor with a single power-mode, we may say that the processor is active when running normal computational processes and inactive when running a "dummy" idle process. For ideal processors with continuous power modes,  $\mathcal{P}_{\text{cpu}}(t)$  may be selected from the range  $[0, \mathcal{P}_{\text{act}}]$ .

#### 3.2.2 Periodic Resource Model

Our control system for the active/inactive processor will enforce strict periodic mode changes. For this purpose, we employ a recently proposed *thermal-aware periodic resource* [5] model, which is an extension of the well-known periodic resource model proposed by [74] for compositional real-time systems. In the thermal-aware periodic resource model, the processing resource is characterized with a two-tuple  $(\Pi, \Theta)$ . The parameter  $\Pi$  is called the *resource period* and  $\Theta$  is called the *resource capacity*. We will assume that  $\Pi$  is a non-negative integer (likely subject to the system tick granularity). The interpretation is that processor will be active for  $\Theta$  amount of time at the beginning of each successive  $\Pi$ -length intervals<sup>2</sup>. The ratio  $\Theta/\Pi$  is called the *resource bandwidth*. Within each processor allocation, an arbitrary uniprocessor scheduling algorithm (e.g., EDF or RM) may be employed to schedule the underlying task system. See

$<sup>^{1}</sup>$ Practically, we implement a system with  $\mathcal{P}_{act}$  and  $\mathcal{P}_{inc}$  power modes from any CPU with clock modulation feature, which is standard for many low end CPUs. Also, if the CPU has DVFS capabilities,  $\mathcal{P}_{act}$  and  $\mathcal{P}_{inc}$  power modes can be emulated by switching the CPU frequency between the highest and lowest available CPU frequencies.

<sup>&</sup>lt;sup>2</sup>For system with clock modulation or DVFS capabilities, CPU active interval is  $\Theta$  and inactive for  $\Pi - \Theta$  interval.

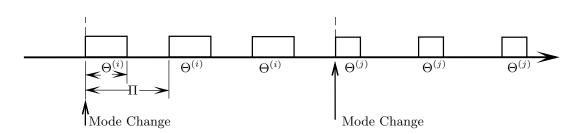

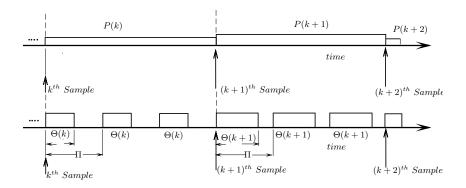

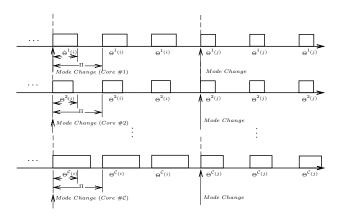

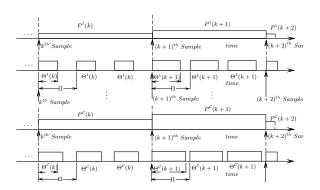

Figure 3.1: The sampling and mode change in the thermal control system (uni-processor systems).

The blocks indicate time periods during with the processor is active under the thermal-aware periodic resource model. Sporadic tasks are scheduled within the activation blocks.

Figure 5.1 for an illustration of the thermal-aware periodic resource.

#### 3.2.3 Software Model

For the uniprocessor case, we assume each performance mode  $M_i$  is characterized by a  $sporadic \ task \ system^3$  [64] with  $n_i$  tasks and the resource capacity  $\Theta^{(i)}$ . That is,  $M_i = \left(\left\{\tau_1^{(i)}, \tau_2^{(i)}, \dots, \tau_{n_i}^{(i)}\right\}, \Theta^{(i)}\right)$  where each  $\tau_j^{(i)} \in M_i$  is a sporadic task characterized by a three-tuple  $(e_j^{(i)}, d_j^{(i)}, p_j^{(i)})$  and  $\Theta^{(i)}$  is the minimum capacity required to meet the deadlines of the tasks of  $M_i$ . (Note that we are abusing notation by allowing  $M_i$  to represent the set of tasks and the two-tuple of the mode's task system and required resource capacity.) In this three-tuple representation for a task,  $e_j^{(i)}$  is the worst-case execution requirement,  $d_j^{(i)}$  is the relative deadline, and  $p_j^{(i)}$  is the minimum inter-arrival separation parameter (historically called the "period"). A sporadic task  $\tau_j^{(i)}$  may produce a (potentially infinite) sequence of jobs, where each job has an execution requirement of  $e_j^{(i)}$  time units and must complete  $d_j^{(i)}$  time units after its arrival. The first job of  $\tau_j^{(i)}$  may arrive at any time after system-start time; however, successive jobs of  $\tau_j^{(i)}$  must arrive at least  $p_j^{(i)}$  time units apart. Further, throughout this thesis, unless we explicitly mentioned, we assume that the resource period  $\Pi$  is identical in all modes. For mode  $M_i$ , a resource capacity of  $\Theta^{(i)}$  is provided every resource period. Figure 3.1 illustrates the processing-time allocation in two different modes.

<sup>&</sup>lt;sup>3</sup>Note, we will be assuming the sporadic task model throughout our objectives, but the results could be extended to other task models without much change.

#### 3.2.4 Performance Modes

We will assume that there is an ordering of real-time performance modes based on their "computational requirements" to meet all of a mode's deadlines. The relation  $M_i \succeq M_j$  indicates that  $M_i$  is more computationally intensive than  $M_j$ . For notational convenience, we will assume that mode  $M_0$  represents the mode with no tasks and  $\Theta^{(0)}$  equal to zero. Furthermore, we assume that the modes are well-ordered and have been indexed in increasing order of computational requirements; i.e.,  $M_0 \preceq M_1 \preceq M_2 \preceq \ldots \preceq M_q$ . While there are many possible ways to define the  $\preceq$  relation, the only ordering required from the perspective of our thermal control is that  $M_i \preceq M_j$ , if and only if,  $\Theta^{(i)} \subseteq \Theta^{(j)}$ ; i.e., to reduce the temperature of the system, we need to decrease the processing-time allocation.

#### 3.2.5 Mode Change Semantics

Our model does not require any particular mode-change semantics to be adopted. Some potential options for dealing with incompletely-executed jobs upon a mode change are:

- 1. aborting any incomplete jobs;

- 2. delaying the release of jobs in the new mode until all jobs of the old mode have completed;

- 3. allowing jobs of the new mode to be released, as soon as legally allowable, while jobs of the old mode are still active.

For the purposes of our hardware testbed and simulations, we assume option 3.

#### 3.2.6 Selection of the Scheduling Algorithm

The scheduling of real-time performance mode  $M_i$  upon the thermal-aware periodic resource may be done by any uniprocessor real-time scheduling algorithm (e.g., earliest-deadline-first or rate-monotonic [57]). However,  $\Theta^{(i)}$  must be sufficiently large for the scheduling algorithm to correctly schedule all jobs of the task set of  $M_i$  (i.e.,  $\{\tau_1^{(i)}, \tau_2^{(i)}, \dots, \tau_{n_i}^{(i)}\}$ ) and (potentially) any jobs from the previous mode that have not completed by the mode change. To obtain a proper resource allocation,  $\Theta^{(i)}$ , for each mode, we use our recently-developed hard-real-time schedulability test (for EDF scheduling under hardware/software mode changes in the periodic resource model) to search for a safe value of  $\Theta^{(i)}$  for each mode [30] to ensure

that deadlines are <u>always</u> met. The multi-modal schedulability analysis ensures that for any valid sequence of mode changes and valid set of job arrivals under the sporadic task model that the EDF scheduler will always meet all deadlines. The analysis works by determining the maximum workload carried from one mode to another and testing whether this "carry-in" will cause a deadline miss. Furthermore, any other online scheduling algorithm can also be used (e.g., fixed priority).

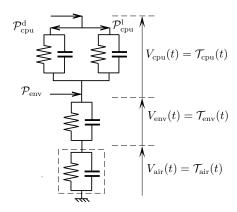

#### 3.2.7 Power/Thermal Model

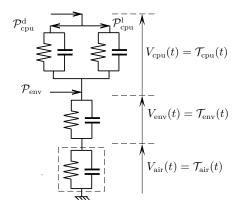

For the uniprocessor case, we use the duality principle in electrical and thermal circuits to describe the dynamics of the power dissipating source using electrical resistance/capacitance (RC) circuits. Therefore, we represent the CPU thermal model with a single RC circuit. Figure 3.2 shows the basic equivalent circuit for the CPU and its surrounding environment. We assume that total dissipated power of the CPU  $\mathcal{P}_{cpu}$  is equal to the sum of the power due to dynamic current  $\mathcal{P}_{cpu}^d$  and power due to leakage current  $\mathcal{P}_{cpu}^\ell$ . Furthermore, we assume that the temperature-dependant leakage power may be closely approximated by a linear function of CPU temperature [59].

Let  $V_{\text{cpu}}(t)$ ,  $V_{\text{env}}(t)$ , and  $V_{\text{air}}(t)$  represent the equivalent voltages for temperatures of the CPU, environment, and air (room) respectively. Let  $\mathcal{T}_{\text{cpu}}$  be the instantaneous relative temperature of the CPU with respect to the immediate environment (e.g., CPU casing),  $\mathcal{T}_{\text{env}}$  be the relative temperature of the immediate environment with respect to the room air temperature, and  $\mathcal{T}_{\text{air}}$  be the (absolute) room air temperature. For example, if  $\mathcal{T}_{\text{air}}$  is  $20^{\circ}C$ ,  $\mathcal{T}_{\text{env}}$  is  $10^{\circ}C$ , and  $\mathcal{T}_{\text{cpu}}$  is  $15^{\circ}C$ , then the absolute temperature of the CPU is  $45^{\circ}C$ .

We assume  $\mathcal{P}_{\text{cpu}}^{\mathbf{d}}(t)$ ,  $\mathcal{P}_{\text{cpu}}^{\ell}(t)$ , and  $\mathcal{P}_{\text{env}}(t)$  represent, respectively, the dynamic CPU, leakage CPU, and environment power dissipation. Let  $R_{\text{cpu}}^{\mathbf{d}}$ ,  $R_{\text{cpu}}^{\mathbf{l}}$ ,  $R_{\text{env}}$ ,  $C_{\text{cpu}}^{\mathbf{d}}$ ,  $C_{\text{cpu}}^{\mathbf{l}}$ , and  $C_{\text{env}}$  represent the dynamic and leakage thermal resistance, environment resistance, CPU dynamic and leakage capacitance, and environment capacitance. Finally, we let  $\sigma_1 \stackrel{\text{def}}{=} \frac{1}{C_{\text{cpu}}^{\mathbf{d}} + C_{\text{cpu}}^{\mathbf{l}}}$  and  $k_T$  and  $k_C$  represent processor-dependent constants used in approximating the temperature-dependant leakage current.

Next, we give the details on the system hardware model related to the multicore processor case as follows.

Figure 3.2: The basic equivalent circuit for a working CPU and its working environment

## 3.3 Modeling of Multicore Processor Systems

Similar to the uniprocessor case, we develop our power model to represent a wide range of embedded processors with minimal amount of power management capabilities.

#### 3.3.1 System Hardware Model

We will assume that the multicore processor consists of m number of active cores and each core has active and inactive power modes  $^4$ . We denote the instantaneous CPU power of  $\mathcal{C}$ 'th core as  $\mathcal{P}^{\mathcal{C}}_{cpu}(t)$ , ( $\mathcal{C} \in \{1...m\}$ ) and assume it dissipates thermal power at a constant rate  $\mathcal{P}_{act}$  and  $\mathcal{P}_{inc}$  in the active and inactive modes, respectively. Also, the power of each core,  $\mathcal{P}^{\mathcal{C}}_{cpu}(t) \ \forall \mathcal{C} \in \{1...m\}$  may vary from the range  $[0, \mathcal{P}_{act}]$ . Further, our model supports the processor to emulate the active and inactive power modes with dynamic voltage and frequency scaling (DVFS) if the processor does not have the real active and inactive implementation. Also, we assume that processor consumes  $e_{act}$  and  $e_{inc}$  amount of energy to acti-

<sup>&</sup>lt;sup>4</sup>Most of the modern CPUs do not support DFVS capability at the core granularity [1]. Therefore, in order to emulate active and inactive power level at the core granularity, the resource capacity  $\Theta$  of each core should be changed along with clock modulation or DVFS.

vate/deactivate from inactive/active modes. Further, during this interval, the processor is inactive while in the low-power state and unavailable for payload task execution. If the processor is minimally active instead of unavailable during inactive interval, the system will behave better than the analysis and our results will continue to be valid.

Our control system for the active/inactive processors will enforce strict periodic mode changes. For this purpose, we employ thermal-aware periodic resource [5] model. In the thermal-aware periodic resource model, the processing resource is characterized with a two-tuple  $(\Pi, \Theta^{\mathcal{C}})$ . The parameter  $\Pi$  is called the resource period and  $\Theta^{\mathcal{C}}$  is called the resource capacity of the  $\mathcal{C}$ 'th core. We will assume that  $\Pi(>0)$  is subject to the system tick granularity. The interpretation is that processor will be active for  $\Theta$  amount of time at the beginning of each successive  $\Pi$ -length intervals. Within each processor allocation, an arbitrary uniprocessor scheduling algorithm (e.g., EDF or RM) may be employed to schedule the underlying task system. See Figure 5.1 for an illustration of the thermal-aware periodic resource.

#### 3.3.2 Software Model

We will assume that each CPU core has specific number of possible performance modes. Also, the task migration at runtime is not permissable and the tasks are statically partitioned within the available processors. We assume each performance mode  $M^{\mathcal{C},i}$  of the  $\mathcal{C}$ 'th core is characterized by a  $sporadic \ task \ system^5$  [64] with  $n_i$  tasks and the resource capacity  $\Theta^{\mathcal{C},i}$ , where  $\Theta^{\mathcal{C},i}$  represents the minimum resource capacity required for i'th mode. That is,  $M^{\mathcal{C},i} = \left(\left\{\tau_1^{\mathcal{C},i},\tau_2^{\mathcal{C},i},\ldots,\tau_{n_i}^{\mathcal{C},i}\right\},\Theta^{\mathcal{C},i}\right)$  where each  $\tau_j^{\mathcal{C},i} \in M^{\mathcal{C},i}$  is a sporadic task characterized by a three-tuple  $(e_j^{\mathcal{C},i},d_j^{\mathcal{C},i},p_j^{\mathcal{C},i})$  and  $\Theta_j^{\mathcal{C},i}$  is the minimum capacity required to meet the deadlines of the tasks of  $M^{\mathcal{C},i}$ . (Note that we are abusing notation by allowing  $M^{\mathcal{C},i}$  to represent the set of tasks and the two-tuple of the mode's task system and required resource capacity.) In this three-tuple representation for a task,  $e_j^{\mathcal{C},i}$  is the worst-case execution requirement,  $d_j^{\mathcal{C},i}$  is the relative deadline, and  $p_j^{\mathcal{C},i}$  is the minimum inter-arrival separation parameter. A sporadic task  $\tau_j^{\mathcal{C},i}$  may produce an infinite sequence of jobs, where each job has an execution requirement of  $e_j^{\mathcal{C},i}$  time units and must complete  $d_j^{\mathcal{C},i}$  time units after its arrival. The first job of  $\tau_j^{\mathcal{C},i}$  may arrive at any time after system-start time; however, successive jobs of  $\tau_j^{\mathcal{C},i}$  must arrive at least  $p_j^{\mathcal{C},i}$  time units apart. We assume that the resource period  $\Pi$  is identical in all modes. For mode  $M^{\mathcal{C},i}$ , a resource capacity of  $\Theta^{\mathcal{C},i}$  is provided every resource period.

<sup>&</sup>lt;sup>5</sup>Note, we will be assuming the sporadic task model throughout our objectives, but the results could be extended to other task models without much change.

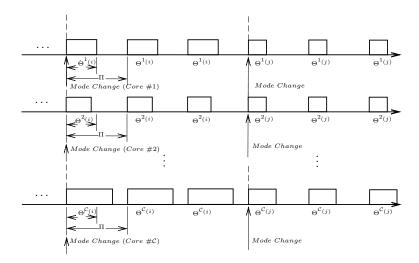

Figure 3.3: The sampling and mode change in the thermal control system (multicore processor system).

The blocks indicate time periods during with the processor is active under the thermal-aware periodic resource model. Sporadic tasks are scheduled within the activation blocks.

Figure 3.3 illustrates the processing-time allocation in two different modes.

#### 3.3.3 Performance Modes

Similar to the uniprocessor case, we assume that there is a partial ordering of real-time performance modes based on their "computational requirements" to meet all of a mode's deadlines. The relation  $M^{\mathcal{C},i} \succeq M^{\mathcal{C},j}$  indicates that  $M^{\mathcal{C},i}$  is more computationally intensive than  $M^{\mathcal{C},j}$ . For notational convenience, we will assume that mode  $M^{\mathcal{C},0}$  represents the mode where with no tasks and  $\Theta^{\mathcal{C},0}$  equal to zero. Furthermore, we assume that the modes are well-ordered and have been indexed in increasing order of computational requirements; i.e.,  $M^{\mathcal{C},0} \preceq M^{\mathcal{C},1} \preceq M^{\mathcal{C},2} \preceq \ldots \preceq M^{\mathcal{C},q}$ . While there are many possible ways to define the  $\preceq$  relation, the only ordering required from the perspective of our thermal control is that  $M^{\mathcal{C},i} \preceq M^{\mathcal{C},j}$ , if and only if,  $\Theta^{\mathcal{C},i} \subseteq \Theta^{\mathcal{C},j}$ ; i.e., to reduce the temperature of the system, we need to decrease the processing-time allocation. Furthermore, we do not define any relationship with modes on different processors. For example, the relationship  $M^{\mathcal{C}_p,i}$  to  $M^{\mathcal{C}_q,i}$ ,  $\mathcal{C}_p,\mathcal{C}_q \in \{1\ldots m\}$  is not defined. Our system allows jobs of the new mode to be released, as soon as legally allowable, while jobs of the old mode are still active.

The scheduling of real-time performance mode  $M^{\mathcal{C},i}$  upon the thermal-aware periodic resource may be done by any real-time scheduling algorithm (e.g., earliest-deadline-first or rate-monotonic [57]). Note that we do not consider the task migration within cores, thereby we can carry out the schedulability test on each core individually. However,  $\Theta^{\mathcal{C},i}$  must be sufficiently large for the scheduling algorithm to correctly schedule all jobs of the task set of  $M^{\mathcal{C},i}$  (i.e.,  $\{\tau_1^{\mathcal{C},i},\tau_2^{\mathcal{C},i},\ldots,\tau_{n_i}^{\mathcal{C},i}\}$ ) and (potentially) any jobs from the previous mode that have not completed by the mode change. To obtain a proper resource allocation,  $\Theta^{\mathcal{C},i}$ , for each mode, we use our hard-real-time schedulability test (for EDF scheduling under hardware/software mode changes in the periodic resource model) to search for a safe value of  $\Theta^{\mathcal{C},i}$  for each mode [30] to ensure that deadlines are always met.

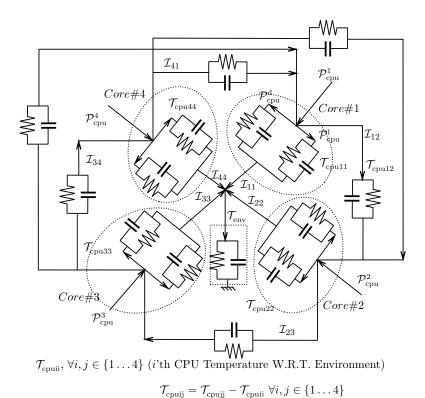

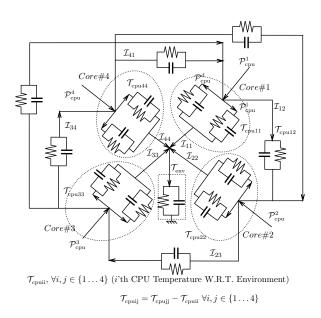

#### 3.3.4 Power/Thermal Model

The thermal architecture (model) of a multicore processor should contain the component to represent each CPU core as well as inter-core thermal effects. For multicore processor thermal model, we extend the RC circuit that we developed for the uniprocessor case. Therefore, we describe the dynamics of the power dissipating source using electrical resistance/capacitance (RC) circuits. Figure 3.4 shows the basic equivalent circuit of a multicore CPU and its surrounding environment. We assume that total dissipated power of  $\mathcal{C}$ 'th CPU core,  $\mathcal{P}_{\text{cpu}}^{\mathcal{C}}$  is equal to the sum of the power due to dynamic current  $\mathcal{P}_{\text{cpu}}^{\text{d}}$  and power due to leakage current  $\mathcal{P}_{\text{cpu}}^{\ell}$  of  $\mathcal{C}$ 'th core. Also, we assume that the leakage and the dynamic current parts within different cores are approximated with single component.

Let  $V_{\text{cpu}}^{\mathcal{C}}(t)$  and  $V_{\text{env}}^{\mathcal{C}}(t)$  represent the equivalent voltages for temperatures of the  $\mathcal{C}$ 'th core of the CPU and environment (room) respectively. Let  $\mathcal{T}_{\text{cpu}}^{\mathcal{C}}$  be the instantaneous relative temperature of the  $\mathcal{C}$ 'th core of the CPU with respect to the immediate environment (e.g., CPU casing),  $\mathcal{T}_{\text{env}}^{\mathcal{C}}$  be the relative temperature of the immediate environment.

Let  $\mathcal{P}_{\text{env}}(t)$  represents, the environment power dissipation. Let  $R_{\text{cpu}(i,j)}^{\text{d}}$ ,  $R_{\text{cpu}(i,j)}^{\ell}$ ,  $R_{\text{env}}$ ,  $C_{\text{cpu}(i,j)}^{\text{d}}$ ,  $C_{\text{cpu}(i,j)}^{\ell}$ , and  $C_{\text{env}}$  represent, respectively the dynamic and leakage thermal resistance, environment resistance, CPU dynamic and leakage capacitance, and environment capacitance between i'th and j'th cores,  $i,j \in \{1\dots m\}$ .

Figure 3.4: The thermal model of the CPU and its working environment.

The basic equivalent electrical circuit of the thermal model of the CPU and its working environment. (for simplicity, the figure shows the structure with 4 adjacent cores) Arrow direction shows the current (A) direction of the equivalent electrical circuit.

#### 3.3.5 Generalized Model