## Tunnel barrier engineering of titanium oxide for high non-linearity of selector-less resistive random access memory

Sangheon Lee, Jiyong Woo, Daeseok Lee, Euijun Cha, Jaesung Park, Kibong Moon, Jeonghwan Song, Yunmo Koo, and Hyunsang Hwang<sup>a)</sup>

Department of Materials Science and Engineering, Pohang University of Science and Technology (POSTECH), Pohang 790-784, South Korea

(Received 19 December 2013; accepted 25 January 2014; published online 7 February 2014)

In this study, the effect of the oxygen profile and thickness of multiple-layers  $TiO_x$  on tunnel barrier characteristics was investigated to achieve high non-linearity in low-resistance state current ( $I_{LRS}$ ). To form the tunnel barrier in multiple-layer of  $TiO_x$ , tunnel barrier engineering in terms of the thickness and oxygen profile was attempted using deposition and thermal oxidation times. It modified the defect distribution of the tunnel barrier for effective suppression of  $I_{LRS}$  at off-state ( $^1/_2V_{Read}$ ). By inserting modified tunnel barrier in resistive random access memory, a high non-linear  $I_{LRS}$  was exhibited with a significantly lowered  $I_{LRS}$  for  $^1/_2V_{Read}$ . © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4864471]

Resistive random access memories (ReRAMs) have been considered next-generation non-volatile memories, capable of solving the scaling limit problem of conventional flash memory. <sup>1–4</sup> ReRAM is a simple structure with a two terminals, and its high-density cross-point array is expected to be able to replace Flash memory.

However, the sneak path current which is the interference from neighboring cells can degrade the readout margin of a high density cross-point array. This sneak path current is caused by a high low-resistance state current (ILRS) at the off-state ( $^{1}/_{2}V_{Read}$ ). Current can flow to the low-resistance state (R<sub>LRS</sub>) cell during the reading operation for high-resistance state (R<sub>HRS</sub>) cell. To suppress the sneak path current, various selector devices-metal insulator transition (MIT), ovnonic threshold switching (OTS), mixed ionic-electronic conductors, and exponential switchinghave been investigated.<sup>5–8</sup> In case of MIT devices, it still retains high operating current for its selectivity. The exponential selector devices have significantly low operating current for high-density cross-point array applications with low sneak-path current. But, they exhibit also low current at on-state for I<sub>LRS</sub> of ReRAM. They cannot satisfy operating current (I) and voltage (V) of ReRAM for 1selector and 1ReRAM (1S1R). In case of OTS, it has very complicated materials composition for its reliable operation. In addition, these selector devices can increase the number of stacked layers in 1S1R devices fabrication. Furthermore, selector devices have required operating I–V matching with ReRAM operating range. To overcome the problems of 1S1R integration and operating I-V range, selector-less ReRAMs with non-linear characteristics have been investigated. 9-12 It requires very simple structure of its reliable operations. The simple structure of ReRAM devices can lead reliable operation with high yield in wafer level fabrication. Although non-linear ReRAMs have an advantage of its simple structure, their non-linearity values are still insufficient, and the origin of the non-linearity was not deeply investigated. However, TiO<sub>x</sub> has been reported to exhibit the non-linear  $I_{LRS}$  with thermally formed sub-oxide  $TiO_x$  by high compliance current. It obtained the non-linear  $I_{LRS}$  of  $TiO_x$  by using the method of thermally activated energy.

In this study, tunnel barrier engineering of multiplelayers of TiO<sub>x</sub> was investigated as a method to achieve the high non-linear I<sub>LRS</sub>. We had controlled thickness and the oxygen profile of TiO<sub>x</sub> tunnel barrier for high non-linearity. Optimum thickness and the oxygen profile of tunnel barrier can effectively reduce electron transfer at low voltage level with direct tunneling suppression, whereas this tunnel barrier can exhibit high current flowing at high voltage level with its Fowler–Nordheim (FN) tunneling of barrier lowering. Therefore, tunnel barrier engineering could be used to modify the defect distribution of the tunnel barrier to achieve high non-linearity and suppress  $I_{LRS}$  at  $1/2V_{Read}$ . Compared to a typical linear ReRAM, we could obtain the sufficient  $I_{LRS}$  at on-state ( $V_{Read}$ ), whereas the  $I_{LRS}$  at  $^{1}/_{2}V_{Read}$  could be significantly reduced by the highly non-linear tunnel barrier characteristics.

We fabricated Pt/Ti/HfO<sub>2</sub>/TiO<sub>x</sub>/Pt devices in a 250-nm via-hole structure. For the isolation layer, a 100-nm thick SiO<sub>2</sub> sidewall layer was deposited on a Pt/Ti/SiO<sub>2</sub>/Si substrate using plasma-enhanced chemical vapor deposition. Subsequently, a 250-nm via-hole was defined using the conventional KrF lithography process, followed by reactive ion etching. First, a 6-nm-thick layer of TiO<sub>x</sub> was deposited for a tunnel barrier in an Ar and O2 mixed plasma using RF sputtering. To form the multiple-layers of TiO<sub>x</sub>, TiO<sub>x</sub> layer was annealed in an oxygen ambient by using rapid thermal annealing at 300 °C. This could oxidize the top surface of the TiO<sub>x</sub> layer, which formed a  $TiO_v(y > x)$  layer at the top surface of the TiO<sub>x</sub>. A 4-nm-thick HfO<sub>2</sub> layer was deposited using an atomic layer deposition system to form the main switching layer, using tetrakis(ethylmethylamino)hafnium (TEMAH) as a precursor and H<sub>2</sub>O as an oxidizer at 250 °C. The Ti oxygen reservoir and Pt top electrode (TE) were deposited using DC sputtering and defined using a 50  $\mu$ m shadow mask (Figure 1).

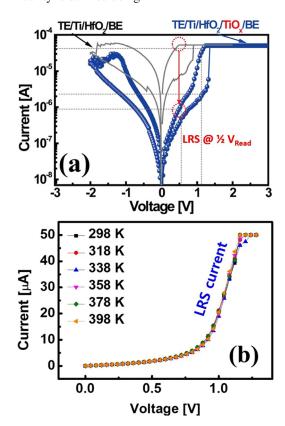

The gray line of Figure 2(a) shows the DC I–V curve, which indicates the linear characteristics of the typical ReRAM (TE/Ti/HfO<sub>2</sub>/BE). A DC bias was applied to the

a)Electronic mail: hwanghs@postech.ac.kr

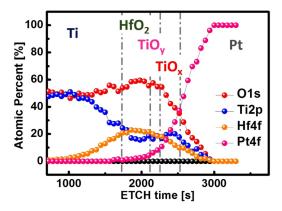

FIG. 1. XPS depth profile of selector-less ReRAM with Pt/Ti/HfO<sub>2</sub>/TiO<sub>y</sub>/Pt stacks. The multiple-layers TiOx tunnel barrier was observed.

TE, and the bottom electrode (BE) was grounded. The resistance changed from R<sub>HRS</sub> to R<sub>LRS</sub> with conductive filament when positive bias was applied to the TE. In contrast, the resistance changed from R<sub>LRS</sub> to R<sub>HRS</sub> with filament dissolution when negative bias was applied to the TE. Typical ReRAM switching is attributed to filament formation and dissolution at HfO2 main switching layer. This linear ReRAM has high  $I_{LRS}$  at  $1/2V_{Read}$ , it degrades readout margin at cross-point array operation. To lower I<sub>LRS</sub> at <sup>1</sup>/<sub>2</sub>V<sub>Read</sub>, TiO<sub>x</sub> tunnel barrier was inserted between main switching layer and BE.

Figure 2(a) shows the DC I-V curve of the high noncharacteristics of the selector-less ReRAM (TE/Ti/HfO<sub>2</sub>/TiO<sub>x</sub>/BE) with a 50 μA compliance current. Non-linearity is defined using<sup>9</sup>

FIG. 2. (a) Typical high non-linear DC I-V switching characteristics of the selector-less ReRAM with comparison of the linear ReRAM. (b) ILRS temperature independence behavior of the selector-less ReRAM with thermal stability.

Non-linearity =

$$(I @ V_{set})/(I @ 1/2V_{set})$$

. (1)

Compared with a typical linear ReRAM, the tunnel barrier engineered TE/Ti/HfO<sub>2</sub>/TiO<sub>x</sub>/BE structure exhibited a substantially lowered I<sub>LRS</sub> at ½V<sub>Read</sub> owing to its highly non-linear behavior. Hence, it can be applicable for cross-point array implementation without any selectors because of the high non-linearity. Figure 2(b) shows the thermal stability of the selector-less ReRAM up to 398 K. Based on this temperature independence behavior, we could confirm that the non-linearity originated with the tunnel barrier characteristics. Tunnel barriers are well known to exhibit temperatures that are not dependent on the non-linear I-V characteristics with direct and FN tunneling mechanisms as a results of the barrier height modification. Once a filament is formed in HfO<sub>2</sub>, the HfO<sub>2</sub> of the main switching layer can assume an ohmic state for the conductive filament, and the barrier height modification of the tunnel barrier mainly controls the non-linear I<sub>LRS</sub> behavior. Thus, we have to consider the non-linear I-V behavior in relation to the tunnel barrier characteristics.

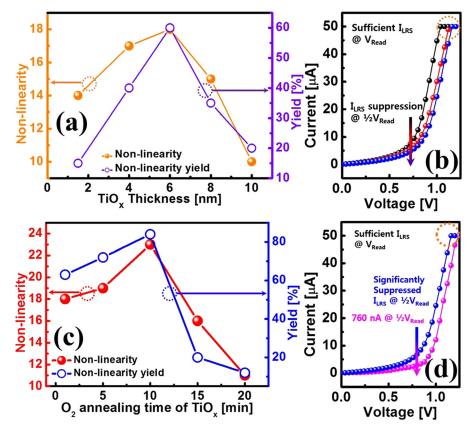

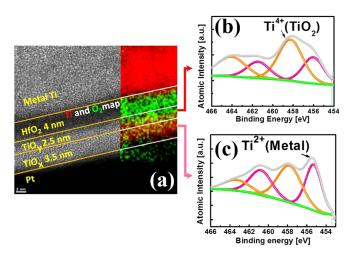

Hence, tunnel barrier engineering in terms of the TiO<sub>x</sub> thickness and oxygen profile control had been investigated because these characteristics modulate tunnel barrier properties in order to obtain high non-linearity in a selector-less ReRAM, as shown in Figures 3(a) and 3(c). 13,14 First, we could suppress the electron transfer at 1/2V<sub>Read</sub> along the tunnel barrier by using the optimum thickness of a tunnel barrier. However, if the tunnel barrier was too thick, it could not exhibit sufficient I<sub>LRS</sub> at V<sub>Read</sub> because the electron transfer was even too suppressed in high voltage level. By contrast, if the tunnel barrier was too thin, most electric field can be applied to the tunnel barrier, and high ILRS can flow. It is well known that high electric field can degrade oxide reliability. It results in poor endurance reliability of ReRAM. Hence, too thick or too thin tunnel barrier could decrease the non-linearity and its yield. Thus, it was found that a 6-nm-thick TiO<sub>x</sub> tunnel barrier exhibited the highest non-linearity (Figures 3(a) and 3(b)). Next, we controlled the oxygen profile of the 6-nm TiO<sub>x</sub> tunnel barrier to achieve higher non-linearity with thermal oxidation at 300 °C (Figures 3(c) and 3(d)). Thermal oxidation could elaborately oxidize the top surface of a TiO<sub>x</sub> tunnel barrier to form a more insulating state. Thus, it could precisely determine the thickness of the oxidized layer on the top surface with thermal oxidation time. Hereafter, we define the top surface of the insulating  $TiO_x$  as  $TiO_y$  (y > x). By adopting the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub>, the TiO<sub>x</sub> thickness was decreased to 3.5-nm with 2.5-nm of TiO<sub>v</sub> (Figure 4(a)). Energy-dispersive X-ray spectroscopy (EDX) shows that the top surface of TiO<sub>x</sub> tunnel barrier has more oxygen content than the TiO<sub>x</sub> bulk region. Hence, the single state TiO<sub>x</sub> was changed to the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub>, which contained an insulating top surface and a relatively metallic bulk region. The existence of this multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> was also confirmed using an X-ray photoelectron spectroscopy (XPS) binding energy analysis of the  $TiO_x$  layer (Figures 4(b) and 4(c)). <sup>15</sup> Consequently, dominant peak of Ti<sup>4+</sup>, which related to the insulating state was obtained at the top surface of TiOx tunnel barrier, and Ti<sup>2+</sup> as the relatively metallic state TiO<sub>x</sub>

FIG. 3. (a) Non-linearity and yield improvement up to critical thickness of TiO<sub>x</sub> tunnel barrier. (b) More suppressed  $I_{LRS}$  at  $^{1}\!/_{\!2}~V_{Read}$  and sufficient ILRS at VRead. (c) Oxygen profile dependence of non-linearity and yield. (d) Significantly suppressed I<sub>LRS</sub> at 1/2 V<sub>Read</sub> with sufficient on-state I<sub>LRS</sub>.

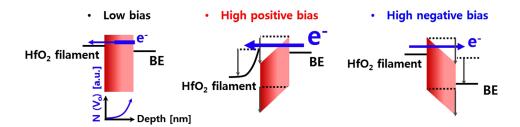

tunnel barrier was observed in the bulk region. Modulated TiO<sub>x</sub> tunnel barrier exhibited a higher non-linearity and yield with multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> by using 10 min of thermal oxidation. This tunnel barrier engineered multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> could directly modify the defect distribution of the tunnel barrier which in turn affected the non-linearity and yield of the selector-less ReRAM (Figure 5). As shown in Figure 5, the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> tunnel barrier attributes the high non-linear I-V characteristics with direct and FN tunneling mechanisms. In the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> tunnel barrier, the TiO<sub>v</sub> and TiO<sub>x</sub> layers play an important role for the direct tunneling suppression at low voltage level. TiO<sub>v</sub> can suppress direct tunneling owing to its insulating state.

FIG. 4. (a) TEM image with oxygen and Ti distribution of EDX analysis. (b) XPS binding energy analysis for TiO<sub>x</sub> tunnel barrier of the top surface. (c) XPS binding energy analysis for TiOx tunnel barrier of the bulk region.

Furthermore, TiO<sub>x</sub> assists to suppress electron transfer for lower current flowing at low voltage level because the thicker multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> can reduce direct tunneling than the thin single layer TiO<sub>v</sub>. In high voltage level, TiO<sub>x</sub> plays an important role in high ILRS. If we applied high positive bias, the TiO<sub>v</sub> region is lowered, and FN tunneling occurred at the TiO<sub>x</sub> layer. By contrast, the TiO<sub>x</sub> region is lowered, and FN tunneling occurred at the TiO<sub>v</sub> layer at high negative bias. In FN tunneling operation of the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub>, the relatively metallic TiO<sub>x</sub> can flow higher I<sub>LRS</sub> than the relatively insulating TiO<sub>y</sub> layer. As shown in the blue curve of Figure 2(a), the I<sub>LRS</sub> of the positive and negative polarities are different owing to different FN tunneling of TiO<sub>x</sub> and TiO<sub>y</sub> at high voltage level, respectively. Hence, the both optimum  $TiO_y$  (2.5-nm) and  $TiO_x$  (3.5-nm) play very important roles in the high non-linear I<sub>LRS</sub> with effectively suppressed direct tunneling and sufficient FN tunneling. The non-linearity is defined with I<sub>LRS</sub> ratio at V<sub>Set</sub> and  $^{1}/_{2}V_{Set}$ . Thus, the multi-layer  $TiO_{v}/TiO_{x}$  which has both insulating and metallic states is necessary for the high non-linearity and reliability of the selector-less ReRAM.

Consequently, the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> could effectively suppress electron transfer at a low voltage level of <sup>1</sup>/<sub>2</sub>V<sub>Read</sub> without any cell selector device by high non-linear characteristics of I<sub>LRS</sub>. In contrast, high voltage level for V<sub>Read</sub> could sufficiently lower the height of the modified tunnel barrier, and electrons could transfer to the conducting HfO<sub>2</sub> filament region by FN tunneling. By achieving reliable tunnel barrier characteristics, we could retain a sufficient  $I_{LRS}$  at  $V_{Read}$ , whereas the  $I_{LRS}$  at  $1/2V_{Read}$  could be significantly reduced by the highly non-linear tunnel barrier characteristics. Compared to the typical linear ReRAM, the selector-less ReRAM with the multi-layer TiO<sub>v</sub>/TiO<sub>x</sub> tunnel

FIG. 5. Tunnel barrier height modification with applying bias and polarity. In off-state, insulating  ${\rm TiO_y}$  and metallic  ${\rm TiO_x}$  effectively suppress electron transfer to reduce  ${\rm I}_{\rm LRS}$ . In on-state, the lowered region of tunnel barrier can be different with applying bias polarity.

barrier exhibited excellent non-linear I<sub>LRS</sub> without any cell selector device.

This research demonstrated the selector-less ReRAM ( $\sim 10\,\mathrm{nm}$  thickness) with high non-linearity by the tunnel barrier engineering of the multi-layer  $\mathrm{TiO_y/TiO_x}$ . The multi-layer  $\mathrm{TiO_y/TiO_x}$  tunnel barrier plays a very important role in high non-linearity by the suppressed direct tunneling and sufficient FN tunneling. It could reduce  $\mathrm{I_{LRS}}$  at off-state significantly compared with the typical linear ReRAM without degradation on-state  $\mathrm{I_{LRS}}$ . Furthermore, It shows a promise for future high density cross-point memory applications.

This work was supported by the R&D MOTIE/KEIT (10039191) and SK Hynix semiconductor.

<sup>5</sup>M. J. Lee, D. S. Lee, H. J. Kim, H. S. Choi, J. B. Park, H. G. Kim, Y. K. Cha, U. I. Chung, I. K. Yoo, and K. N. Kim, Tech. Dig. - Int. Electron Devices Meet. 2012, 2.6.2.

<sup>6</sup>S. H. Kim, X. Liu, J. B. Park, S. J. Jung, W. T. Lee, J. Y. Woo, J. H. Shin, G. D. Choi, C. H. Cho, S. S. Park, D. S. Lee, E. J. Cha, B. H. Lee, H. D. Lee, S. G. Kim, S. O. Chung, and H. S. Hwang, VLSI Symp. Tech. Dig. 2012 155

<sup>7</sup>W. T. Lee, J. B. Park, J. H. Shin, J. Y. Woo, S. H. Kim, G. D. Choi, S. J. Jung, S. S. Park, D. S. Lee, E. J. Cha, H. D. Lee, S. G. Kim, S. O. Chung, and H. S. Hwang, VLSI Symp. Tech. Dig. 2012, 37.

<sup>8</sup>J. Y. Woo, W. T. Lee, S. S. Park, S. H. Kim, D. S. Lee, G. D. Choi, E. J. Cha, J. H. Lee, W. Y. Jung, C. G. Park, and H. S. Hwang, VLSI Symp. Tech. Dig. **2013**, 168.

<sup>9</sup>H. D. Lee, S. G. Kim, K. Cho, H. Hwang, H. Choi, J. Lee, S. H. Lee, J. Suh, S. O. Chung, Y. S. Kim, K. S. Kim, W. S. Nam, J. T. Cheong, J. T. Kim, S. Chae, E. R. Hwang, S. N. Park, S. Sohn, C. G. Lee, H. S. Shin, K. J. Lee, K. Hong, H. G. Jeong, K. M. Rho, Y. K. Kim, S. Chung, J. Nickel, J. J. Yang, H. S. Cho, F. Perner, R. S. Williams, J. H. Lee, S. K. Park, and S. J. Hong, VLSI Symp. Tech. Dig. 2012, 151.

<sup>10</sup>H. Y. Chen, S. Yu, P. Huang, J. Kang, and H. S. P. Wong, Tech. Dig. - Int. Electron Devices Meet. 2012, 498.

<sup>11</sup>J. Y. Woo, S. H. Kim, W. T. Lee, D. S. Lee, S. S. Park, G. D. Choi, E. J. Cha, and H. S. Hwang, Appl. Phys. Lett. **102**, 122115 (2013).

<sup>12</sup>J. J. Yang, J. Borghetti, D. Murphy, D. R. Stewart, and R. S. Williams, Adv. Mater. 21, 3754 (2009).

<sup>13</sup>J. Jung and W. J. Cho, J. Semicond. Technol. Sci. **8**, 32 (2008).

<sup>14</sup>D. J. Kirk, D. Cockayne, A. K. Petford-Long, and G. Yi, J. Appl. Phys. 106, 123915 (2009).

<sup>15</sup>B. R. Chracanovic, A. R. Pedrosa, and M. D. Martins, Mater. Res. 15, 372 (2012).

<sup>&</sup>lt;sup>1</sup>R. Waser and M. Aono, Nature Mater. **6**, 833 (2007).

<sup>&</sup>lt;sup>2</sup>B. Govoreanu, G. S. Kar, Y.-Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I. P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, P. Hendrickx, G. Pourtois, H. Bender, L. Altimime, D. J. Wouters, J. A. Kittl, and M. Jurczak, Tech. Dig. - Int. Electron Devices Meet. **2011**, 729.

<sup>&</sup>lt;sup>3</sup>S. G. Park, B. Magyari-Kope, and Y. Nishi, VLSI Symp. Tech. Dig. **2011**, 46.

<sup>&</sup>lt;sup>4</sup>I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park, S. O. Park, H. S. Kim, I. K. Yoo, U. I. Chung, and I. T. Moon, Tech. Dig. - Int. Electron Devices Meet. **2004**, 587.

Applied Physics Letters is copyrighted by the American Institute of Physics (AIP). Redistribution of journal material is subject to the AIP online journal license and/or AIP copyright. For more information, see http://ojps.aip.org/aplo/aplcr.jsp